(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1990 |

|

SU1839257A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1545224A1 |

| Устройство диагностирования электронной аппаратуры | 1990 |

|

SU1837244A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

Изобретение относится к автоматическому контролю и позволяет повысить достоверность контроля. Устройство содержит генератор 1 слов, ЭВМ 3 и запоминающий блок 7. Введение блока 4 свертки, блока 5 сравнения, делителя 6 частоты, счетчика 8 адреса, блока 9 управления и мультиплексора 10 увеличивает количество контролируемых точек объекта диагностирования. 3 ил.

flus.f

Изобретение относится к автомати- ческому контролю и может быть использовано для контроля и диагностирования технологических дефектов электронных узлов.

Целью изобретения является повышение достоверности за счет увеличе- .ния количества контролируемых точек объекта диагностирования.

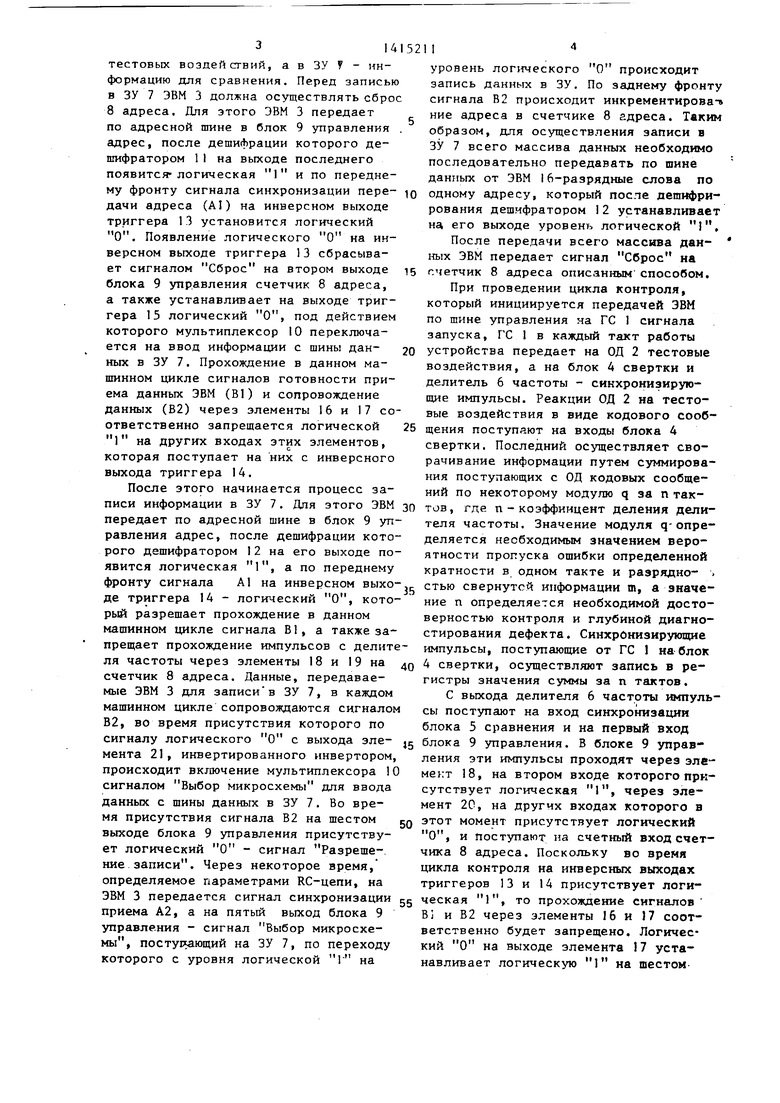

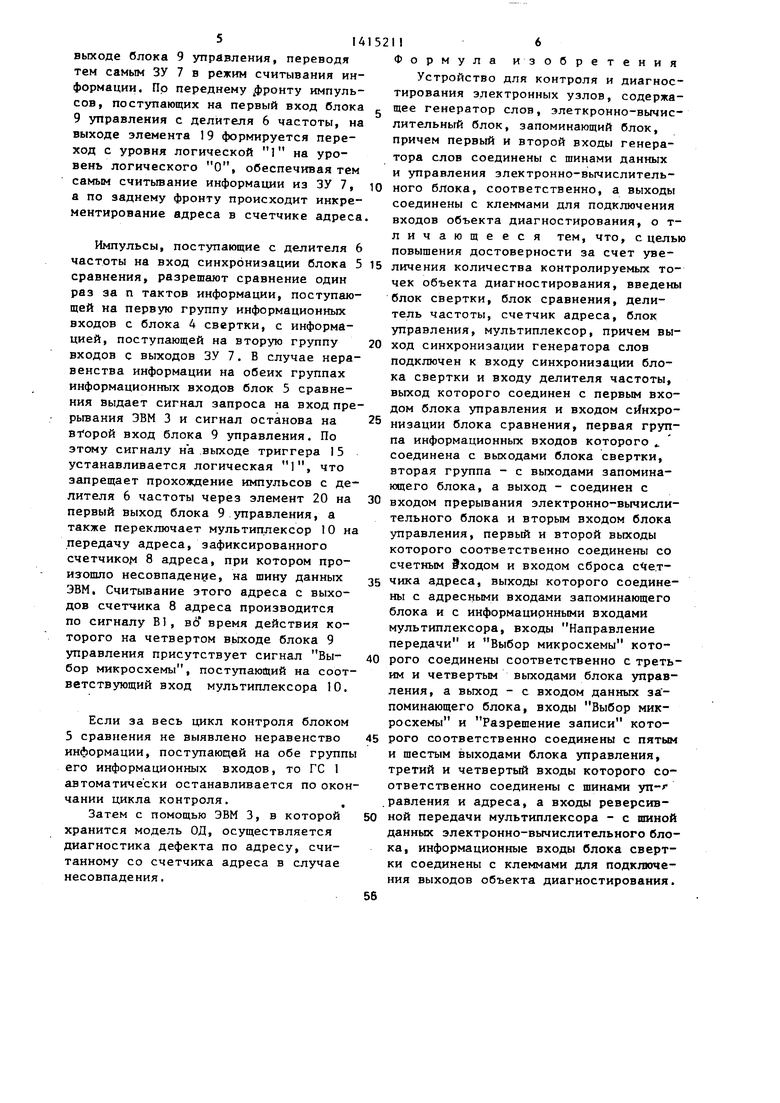

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - принципиальная схема блока управления; на фиг. 3 - функциональная схема блока свертки.

Устройство (фиг.1) содержит генератор 1 слов (ГС), объект 2 диагностирования (ОД), электронно-вычислительный блок 3 (ЭВМ), блок 4 свертки, блок 5 сравнения j делитель 6 частоты, запоми- мающий блок 7, счетчик 8 адреса, блок 9 управления и мультиплексор 10. Шины данных и управления ГС I соединены с соответствующими шинами ЭВМ 3. Выход синхронизации ГС 1 соединен с входом делителя 6 частоты и с входом синхро- низации блока 4 свертки. Выходы каналов ГС 1 соединены с входами ОД 2, выходы которого соединены с информационными входами блока 4 свертки. Выходы блока 4 свертки соединены с первой группой информационных входов блока 5 сравнения, а выходы запоминающего блока 7 (ЗУ) - с второй группой. Выход делителя 6 частоты соединен с первым входом блока 9 управления и с входом синхронизации блока 5 сравнения, выход которого соединен с входом прерывания ЭВМ 3 и с входом блока 9 управления. Первый и второй в ыходы блока 9 управления соединены с входами Счетный вход и Сброс счетчика 8 адреса соответственно. Третий и четвертьй выходы блока 9 управления соединены с входами Направление передачи и Выбор микросхемы мультиплексора 10 соответственно. Пятый и шестой выходы блока 9 управления соединены с выходами Выбор микросхемы и Разрешение записи ЗУ 7 соответственно . Выход счетчика 8 адреса сседи- йен с адресным входом ЗУ 7 информационным входом мультиплексора 10, выход которого соединен с входом данных ЗУ 7. Шина данных ЭВМ 3 соединена с входом данных мультиплексора 10, а шины управления и адреса соединены соответственно с третьим и четвертым входами блока 9 управления.

д

5

Q 5 - Q . 0 5 5

5

Блок 9 управления фиг.2 содержит дешифраторы II и 12, триггеры 13-15, элементы ИЛИ-НЕ 16 и 17, элементы И 18 и 19, элементы ИЛИ 20 и 21, инверторы 22-27, резистор 28, конденсатор 29.

Первый вход блока соединен с первым входом элемента И 18, выход которого соединен с первым входом элемента ИЛИ 20 и через инвертор 26 с первым входом элемента И 19. Второй вход элемента И 19 соединен через инвертор 25 с первыми вьгаодами резистора 28, конденсатора 29 и через инвертор 24 с выходом синхронизации приема блока. Второй вход блока соединен с установочным входбм триггера 15, третьи . входы блока через дешифраторы II и 12 соединены с информационными входами триггеров 13 и 14, тактовые входы которых через инвертор 22 соединены с входом синхронизации передачи адреса. Выход триггера 14 соединен с вторым входом элемента И 18, первыми входами элементов ИЛИ-НЕ 16 и 17, вторые входы которых соединены с входами готовности приема данных ЭВМ и сопровождения данных соответственно. Выход элемента ИЛИ 20 соединен с первым выходом блока. Второй выход блока соединен с выходом триггера I3 и входом сброса триггера 15, выход которого соединен с третьим выходом блока и вторым входом элемента ИЛИ 20. Четвертый выход блока через инвертор 23 соединен с вторым выводом резистора 28 и выходом элемента ИЛИ 21. Пятый выход блока соединен с выходом элемента И 19. Шестой выход блока через инвертор 27 соединен с третьим входом элемента И 20, выходом элемента ИЛИ- НЕ 17 и первым входом элемента ИЛИ 21, второй вход которого соединен с выходом элемента ИЛИ-НЕ 16.

Блок А свертки (фиг.З) может быть реализован (пример для свертки по модулю 7), например, как последовательно соединенные сумматор 30, регистр 31 и элемент 32 свертки, причем первые входы сумматора соединены с первыми входами блока, вторые входы - с выходами регистра 31, второй вход которого соединен с вторым входом блока.

Устройство работает следующим образом.

На этапе подготовки к проведению контроля ЭВМ производит запись в ГС 1

314

тестовых воздействий, а в ЗУ У - информацию для сравнения. Перед записью в ЗУ 7 ЭВМ 3 должна осуществлять сброс 8 адреса, 11пя этого ЭВМ 3 передает по адресной шине в блок 9 управления адрес, после дешифрации которого дешифратором 11 на выходе последнего появится-логическая 1 и по переднему фронту сигнала синхронизации пере- дачи адреса (AI) на инверсном выходе триггера 13 установится логический О. Появление логического О на инверсном выходе триггера 13 сбрасывает сигналом Сброс на втором выходе блока 9 управления счетчик 8 адреса, а также устанавливает иа выходе триггера 15 логический О, под действием которого мультиплексор 10 переключается на ввод информации с шины дан- ных в ЗУ 7. Прохождение в данном машинном цикле сигналов готовности приема данных ЭВМ (В1) и сопровождение данных (В2) через элементы 16 и 17 соответственно запрещается логической 1 на других входах этих элементов, которая поступает на них с инверсного выхода триггера 14.

После этого начинается процесс записи информации в ЗУ 7. Для этого ЭВМ передает по адресной шине в блок 9 управления адрес, после дешифрации которого дешифратором 12 на его выходе появится логическая 1, а по переднему фронту сигнала А1 на инверсном выходе триггера 1А - логический О, который разрешает прохождение в данном машинном цикле сигнала В1, а также запрещает прохождение импульсов с делителя частоты через элементы 18 и 19 на счетчик 8 адреса. Данные, передаваемые ЭВМ 3 для записи в ЗУ 7, в каждом машинном цикле сопровождаются сигналом В2, во время присутствия которого по сигналу логического О с выхода эле- мента 21, инвертированного инвертором, происходит включение мультиплексора 10 сигналом Выбор микросхемы для ввода данных с шины данных в ЗУ 7. Во время присутствия сигнала В2 на шестом выходе блока 9 управления присутствует логический О - сигнал Разреше-. ние записи. Через некоторое время, определяемое параметрами RC-цепи, на ЭВМ 3 передается сигнал синхронизации приема А2, а на пятый выход блока 9 управления - сигнал Выбор микросхемы, посту1 ающий на ЗУ 7, по переходу которого с уровня логической Г на

11

уровень логического О происходит запись данных в ЗУ. По заднему фронт сигнала В2 происходит инкрементирова ние адреса в счетчике 8 адреса. Таки образом, для осуществления записи в ЗУ 7 всего массива данных необходимо последовательно передавать по шине данных от ЭВМ 16-разрядные слова по одному адресу, который после дешифрирования дешифратором 12 устанавливае на, его выходе уровенг:. логической I

После передачи всего массива дан- ных ЭВМ передает сигнал Сброс на счетчик В ащреса описанным способом.

При проведении цикла контроля, который инициируется передачей ЭВМ по шине управления на ГС 1 сигнала запуска, ГС 1 в каждый такт работы устройства передает на ОД 2 тестовые воздействия, а на блок 4 свертки и делитель 6 частоты - синхронизирующие импульсы. Реакции ОД 2 на тестовые воздействия в виде кодового сообщения поступают на входы блока 4 свертки. Последний осуществляет сворачивание информации путем суммирования поступающих с ОД кодовых сообщений по некоторому модулю q за п тактов, где п - коэффиицент деления делителя частоты. Значение модуля q-определяется необходимым значением вероятности пропуска ошибки определенной кратности в одном такте и разрядно- стью свернутой информации т, а эначе- ние п определяется необходимой достоверностью контроля и глубиной диагностирования дефекта. Синхронизирующие импульсы, поступающие от ГС 1 на блок 4 свертки, осуществляют запись в регистры значения суммы за п тактов.

С выхода делителя 6 частоты импульсы поступают на вход синхронизации блока 5 сравнения и на первый вход блока 9 управления. В блоке 9 управления эти импульсы проходят через элемент 18, на втором входе которого присутствует логическая 1, через зле- мент 2С, на других входах которого в этот момент присутствует логический О, и Поступают на счетный вход счетчика 8 адреса. Поскольку во время цикла контроля на инверсных выходах триггеров 13 и 14 присутствует логическая 1, то прохождение сигналов В и В2 через элементы 16 и 17 соответственно будет запрещено. Логический О на выходе элемента 17 устанавливает логическую 1 на шестом

514

выходе блока 9 управления, переводя тем самым ЗУ 7 в режим считывания информации. По переднему фронту импульсов, поступающих на первый вход блока 9 управления с делителя 6 частоты, на выходе элемента 19 формируется переход с уровня логической 1 на уровень логического О, обеспечивая тем самым считьтание информации из ЗУ 7, а по заднему фронту происходит инкре- ментирование адреса в счетчике адреса

Импульсы, поступающие с делителя 6 частоты на вход синхронизации блока 5 сравнения, разрешают сравнение один раз за п тактов информации, поступающей на первую группу информационных входов с блока Д свертки, с информацией, поступающей на вторую группу входов с выходов ЗУ 7. В случае неравенства информации на обеих группах информационных входов блок 5 сравнения выдает сигнал запроса на вход пре- рьгеания ЭВМ 3 и сигнал останова на второй вход блока 9 управления. По этому сигналу на .выходе триггера 15 устанавливается логическая 1, что запрещает прохождение импульсов с делителя 6 частоты через элемент 20 на первый выход блока 9 управления, а также переключает мультиплексор 10 на передачу адреса, зафиксированного счетчико; 8 адреса, при котором про- несовпадение, на шину данных ЭВМ. Считывание этого адреса с выходов счетчика 8 адреса производится по сигналу В), во время действия которого на четвертом выходе блока 9 управления присутствует сигнал Вы- бор микросхемы, поступающий на соответствующий вход мультиплексора Ю.

Если за весь цикл контроля блоком 5 сравнения не выявлено неравенство информации, поступающей на обе группы его информационных входов, то ГС 1 автоматически останавливается по окончании цикла контроля.,

Затем с помощью ЭВМ 3, в которой хранится модель ОД, осуществляется диагностика дефекта по адресу, считанному со счетчика адреса в случае несовпадения.

И6

Формула изобретения

Устройство для контроля и диагностирования электронных узлов, содержащее генератор слов, элеткронно-вычис- лительный блок, запоминающий блок, причем первый и второй входы генератора слов соединены с шинами данных и управления электронно-вычислительного блока, соответственно, а выходы соединены с клеммами для подключения входов объекта диагностирования, о т- личающееся тем, что, с цель повышения достоверности за счет увеличения количества контролируемых точек объекта диагностирования, введены блок свертки, блок сравнения, делитель частоты, счетчик адреса, блок управления, мультиплексор, причем выход синхронизации генератора слов подключен к входу синхронизации блока свертки и входу делителя частоты, выход которого соединен с первым входом блока управления и входом cilHxpo- низации блока сравнения, первая группа информационных входов которого соединена с выходами блока свертки, вторая группа - с выходами запоминающего блока, а выход - соединен с входом прерывания электронно-вычислительного блока и вторым входом блока управления, первый и второй выходы которого соответственно соединены со счетным §ходом и входом сброса .T- чика адреса, выходы которого соединены с адресными входами запоминающего блока и с информационными входами мультиплексора, входы Направление передачи и Выбор микросхемы которого соединены соответственно с третьим и четвертым выходами блока управления, а выход - с входом данных за - поминающего блока, входы Выбор микросхемы и Разрешение записи которого соответственно соединены с пятым и шестым выходами блока управления, третий и четвертый входы которого соответственно соединены с шинами yn-f равления и адреса, а входы реверсивной передачи мультиплексора - с шиной данных электронно-вычислительного блока, информационные входы блока свертки соединены с клеммами для подключения выходов объекта диагностирования.

tPiie,2

иг.З

Авторы

Даты

1988-08-07—Публикация

1985-08-08—Подача