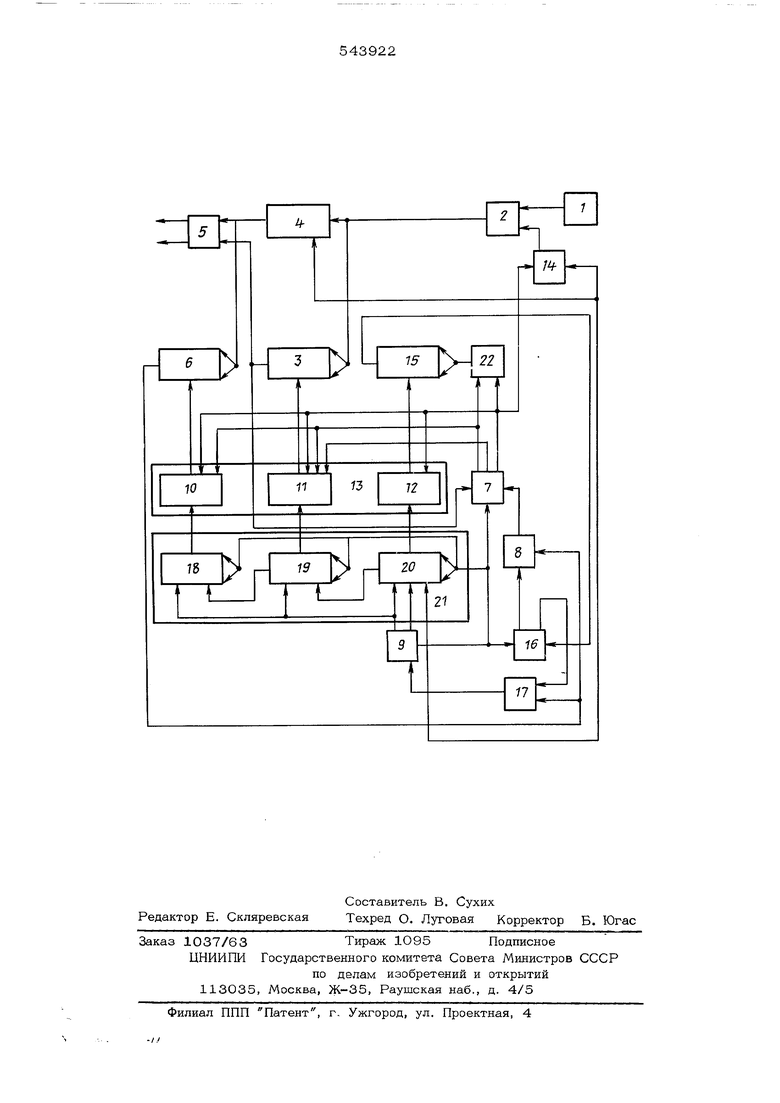

(54) ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР Он содержит генератор импульсов 1, третий элемент И 2, счетчик отношения координатных приращений 3, делитель частоты 4, коммутатор 5, счетчик большего координатного приращения 6, блок управления 7, второй элемент И 8, блок считывания программы 9, схемы переписи 10, 11, 12, образую щие блок перезаписи 13, управляющий триггер 14, счетчик повторения кадра 15, допол нительный триггер 16, первый элемент И 17 разряды 18, 19 и 20 регистра сдвига 21 и и элемент ИЛИ 22. Устройство работает следующим образом. Рабочие импульсы, вырабатываемые задающим генератором 1 с частотой следования ff,-a (где -Рп - частота исполнительного устройства, о - основание системы счисления приращений координат, К - максимально возможная разрядность цифровых эквивалентов приращений), подаются на вход элемента 2, который закрыт. Каждый цикл интерполяции начинается с ввода информации кадра блоком 9, начальный пуск которого осуществляется вручную, а затем запуск его при вводе каждого кадра происходит автоматически по сигналу с выхода элемента 17. В каждый кадр в двоично-десятичном коде входят значение большего приращения координат, поделенного на число повторений кадра, отношение большего приращения координат к меньшему и число повторений кадра. Если приращение координаты X больше или равно приращению координат Y , т.е , то в кадр будут входить приращение ДХ, поделенное на число повторений кадра ДХ отношение к приращению ЛУ т -ЛХ/д и число повторений кадраt7. Если ДХ-СДУ, то большим приращением будетДУ 3 бго отношение к меньшему прира- щениюЛХ будет равно № ;ЛУ/4Х,Пусть необходимо выполнить интерполяцию кадра , а число повторений кадра равно П . Ввод информации в интерполятор с кадра блоком 9 осуществляется в обратном двоично- десятичном коде в младшую тетраду разряда 20 регистра 21 со сдвигом по четыре разряда влево. При появлении сиг нала о конце ввода кадра блок 9 останавливается и в разряде 18, 19 и 20 регистра 21 будут соответственно находится в обратном коде значения большего из приращений координат, поделенного на число повторений кадра,АХ-- отношение большего из приращений к меньшему) число повторений данного кадра f) По сигналу с выхода блока 9 о конце вво да кадра к содержимому разрядов 18, 19 и 20 через счетные входы прибавляется единица, триггер 16 устанавливается в единичное состояние и запускается блок управления 7. По этому сигналу блок 7 формирует импульс на выходе, который подключен к схемам переписи 10, 11 и 12, к элементу ИЛИ 22 и к единичному входу триггера 14, По переднему фронту импульса происходит перепись содержимого разрядов 18, 19, и 20 соответственно в счетчики 6,3 и 15, а по его заднему фронту через элемент ИЛИ 22 по счетному входу в счетчик 15 прибав ляется единица и триггер 14 устанавливается в единичное состояние. При единичном состоянии триггера 14 открывается элемент 2 и импульсы с частотой следования f а поступают на делитель частоты 4 к на счетньш вход счетчика 3 отношений большего из приращений к меньшему. С выхода делителя частоты 4 импульсы с частотой следования f подаются на вход коммутатора 5 и на счетный вход счетчика 6 большего из приращений. При поступлении на вход счетчика 6 лу импульсов в количестве, равномДХ , он установится в нулевое состояние и на его выходе возникает импульс, который поступает на элементы 8 и 17. Так как триггер 16 находится в единичном состоянии, то открыт элемент 8 и через него по импульсу с выхода счетчика 6 запустится блок управления 7. По импульсу с элемента 8 на выходе блока 7, который подключен к схемам переписи 10 и 11, а также к элементу ИЛИ 22, возникает импульс. По переднему фрон- ту этого импульса в паузу между импульсами с частотой следования - С, осуществляется перепись содержимого разрядов 18 и 19 соответственно в счетчики 6 и 3, а по заднему фронту через элемент ИЛИ в счетчик 15 прибавляется единица, и работа электрической схемы интерполятора повторяется. После того, как работа интерполятора повто- рится (П - 1) раз счетчик 15 установится в в нулевое состояние и по сигналу с его выхода триггер 16 опрокинется в нулевое состояние. Следовательно, откроется элемент 17 и закроется элемент 8. В этот момент счетчик 6 начнет отрабатывать значение ЛХ-- -ный раз и по импульсу с его выхода через открытый элемент 17 установятся в нулевое состояние первая тетрада разряда 20, делитель частоты 4 и триггер 14. При установке триггера 14 в нулевое состояние закроется элемент 2. По этому же импульсу запускается блок считывания программы 9 и осуществляется ввод следующего кадра. Таким образом за период рассмотренного цикла работы интерполятора (время отработки одного кадра) по оси X с выхода коммутатора 5 в исполнительное устройство поступит количество импульсов, равное Л х-П. За это же время на вход счетчика 3 поступит импульсов в количестве, равном ДХО, -П

Счетчик 3 чмеет разрядность 2к, следовательно он Оудет устанавливаться в нулевое состояние при поступлении на его счетный вход импульсов в количестве т- . При установке счетчика 3 в нулевое состояние на его выходе возникает импульс, по которому запускается блок управления 7. Блок 7 формирует импульс на выходе, который соединен со схемой переписи 11, По этому импульсу в момент паузы между импульсами с частотой следования f, о, значение т снова перепишется из разряда 19 в счетчик 3. Перепись значения m из разряда 19 в счетчик 3 через количество импульсов, равное m-CJ, будет повторяться в течение всего цикла работы интерполятора. Таким образом, в период отработки кадра выполнится деление количества импульсов, равное 4ХС,П , на величину m-(f , а следовательно с выхода счетчика 3 на вход коммутатора 5 поступит импульсов в количестве ЛУ. Использование счетчика 3 с разрядностью в два раза большей, чем разрядность счетчика 6, а также последовательности импульсов, поступающих на вход счетчика 3, с частотой следования , позволяет выполнить деление большего из приращений координат на целые и дробные значения т

В случае, еслиЛХ ДУ , то работа интерполятора аналогична и отличается лишь коммутацией каналов X и У на выходе коммутатора 5. Если одно из приращений координат равно нулю, то приращение не равное нулю является большим, а т принимается равным нулю. При нулевом значении гп счетчик 3 не будет устанавливаться в нулевое состояние после поступления на его вход импульсов в количестве равном ДХ -О, , еслиду 0 Следовательно, за время отработки кадра с выхода счетчика 3 на вход коммутатора 5 импульсы поступать не будут.

Применение такого интерполятора позволит обеспечить высокое быстродействие в системах программного управления и обеспечить интерполяцию больших приращений координат при незначительном объеме информации в управляющей программе.

Формула изобретения

Линейный интерполятор, содержащий элемент ИЛИ, первый элемент И и последователно соединенные блок считывания программы, подключенный через регистр сдвига к блоку перезаписи, блок управления, один из входов которого соединен с выходом второго элемента И, управляющий триггер, третий элемент И, подключенный к генератору импульсов, счетчик отношения координатных приращений, соединенный с блоками перезаписи, и управления, и коммутатор, один из входов которого через делитель частоты подключен к выходу третьего элемента И и через счетчик большего координатного приращения- к блоку перезаписи, отли чающийся тем, что, с целью повышения быстродействия интерполятора, в него введены последовательно соединенные счетчик повторения кадра, входы которого подключены к блоку перезаписи и через элемент ИЛИ к выходам блока управления, и дополнительный триггер, один из входов которого соединен с блоком считывания прогаммы, а выходы -со входами первого -и второго элементов И, другие входы которых подключены к выходу счетчика большего координатного приращения, причем выход первого элемента И соединен со входами регистра сдвига, блока считывания программы, управляющего триггера и делителя частоты.

Источники информации, принятые во внимание при экспертизе изобретения:

1.Авторское свидетельство СССР №225571, М. Кл. Q 06 G 7/30, 1967

2.Авторское свидетельство СССР

№ 344415, М Кл.С 05 В 19/18, 1971

3.Авторское свидетельство СССР

№ 499555 М Кл, G 05 В 19/18, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор для цифровых двухкоординатных систем програмного управления | 1973 |

|

SU499555A1 |

| Линейный интерполятор | 1989 |

|

SU1695267A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Многоканальный интерполятор для программного управления многокоординатным станком | 1978 |

|

SU746429A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Функциональный интерполятор | 1986 |

|

SU1383301A1 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624406A1 |

| Функциональный интерполятор | 1984 |

|

SU1168900A1 |

| Линейно-круговой интерполятор | 1985 |

|

SU1259218A1 |

Авторы

Даты

1977-01-25—Публикация

1975-11-28—Подача