.А

(Л

00

со

00 00

Изобретение относится к авт() ке и вычислительтюй технике и может быть использовано в графических терминальных устройствах для построения отрезков прямых с приращениями &Х - О и N Y 0.

Цель изобретения - повышение точности интерполяции.

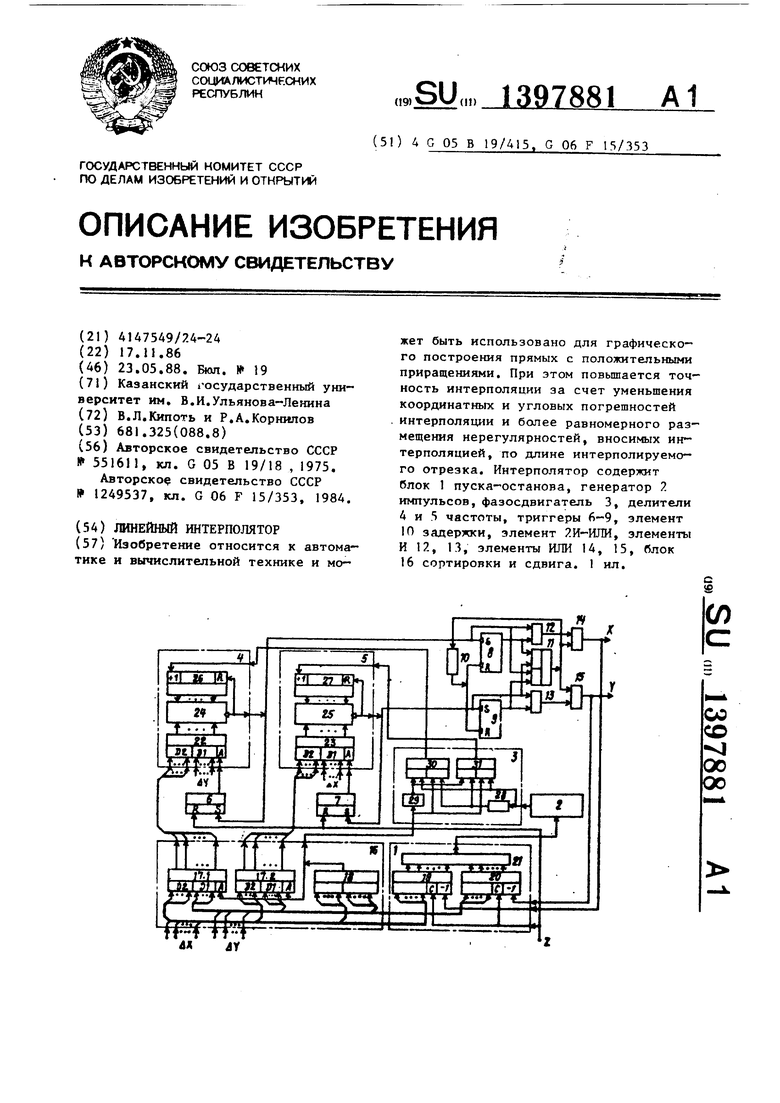

На чертеже приведена функциональ- ная схема интерполятора.

Интерполятор содержит блок 1 пуска-останова, генератор 2 импульсов, фазосдвигатель 3, делители 4 и 5 частоты, триггеры 6-9, элемент 0 задержки, элемент 1 -Ш1И 1 , элементы И 2 и 13, элементы ШТИ 14 и 15, блок 16 сортировки и сдвига чисел.

Блок 16 содержит два мультиплексора 17-1 и 17-2 и схему 18 сравне- ния,

Блок 1 содержит счетчики 19 и 20 и элемент И-НЕ 21.

Делители 4 и 5 содержат соответственно мультитглексоры 2.2 и 23, схемы 24 и 25 сравнения и счетчики 26 и 27

Фазосдвигатель 3 содержит элемент 28 задержки, элемент НЕ 29 и два элемента 2И-ИЛИ 30 и 31.

Линейный интерполятор работает следуюшим образом.Перед началом интерполяции счетчики 26 и 27 делителей 4 и 5, счетчики 19 и 20 блока 1 и триггеры 8 и 9 установлены в нулевое состояние, а на входы задания приращений выставлены двоичные коды & X О, 0. На выходе схемы 18 сравнения формируется единичный потенциал при условии X : ЛУ и нулавой - в противном слу- чае. Если на выходе схемы 18 единичный потенциал, то на выходах мультиплексора 17-1 выставлен код дХ/23, на выходах мультиплексора 17-2 - код дХ и в фазосдвигателе 3 разрешено пр хождение импульсов с генератора 2 через элемент 2И-ИЛИ 31, а импульсов с элемента 28 задержки - через элемент 2И-ИЛИ 30. В противном случае на выходах мультиплексора 17-1 код ЬУ, на выходах мультиплексора 17 - и в фазосдвигателе 3 разрешено прохождение импульсов с генератора 2 через элемент 2И-ИЛИ 30, а задержанных импульсов - через эле- мент 2И-ИЛИ 31.

Импульс, проходящий по входу 7, запуска устройства, заносит коды лХ, &Y в счетчики 19 и 20 блока 1 и

устаиав тиляет триггеры 6 и 7 я нулевое состоят ие . Нулевые мот енциалы с выходов триггеров 6 и 7 подключают к входам схем 24 и 25 сравнения делителей 4 и 5 частоты коды, поданные на вторые группы информационных вхо- доп мультиплексоров 22 и 23, связан- т.:е с выходами блока 16. Занесение не нуленых кодов приращений в счетчики 19 и 20 блока 1 приводит к формированию единичного потенциала на выходе элемента И-НЕ 21, который запускает генератор 2 импульсов. На тактовые входы делителей 4 и 5 частоты через фаэосдвигатель 3 начинают поступать серии импульсов с частотой Г, сдвинутые по фазе на половину периода. Первым формируется импульс с делителя частоты, на который подан код &Х/21 или У/2, этим определяется необходимый сдвиг фаз между выходными импульсными последовательностями. Этот импульс устанавливает триггер 6 или

7в единичное состояние, что приводит к подключению к входам схемы 24 или 25 сравнения соответствующего делителя 4 или 5 кода приращения

лУ или X и сбрасывает счетчик 26 или 27 делителя в нулевое состояние. Этот же импульс задним фронтом устанавливает в единичное состояние триггер 8 или 9. Если следующий по времени импульс формируется тем же делителем частоты, то он проходит через элемент И 12 или 13 и элемент ИЛИ 14 или 15, формируя импульс продвижения на соответствующем выходе интерполятора. Состояние триггеров

8и 9 при этом не изменяется.

В противном случае следующий импульс проходит через элемент 2И-ИЛИ 11 и оба элемента ШТИ 14 и 15, формируя импульсы продвижения на обоих выходах устройства одновременно, что приводит к диагональному перемещению исполнительного механизма (пишущего элемента). 1 1мпульс с выхода элемента 2И-Ш1И 11, задержанный на элементе 10 задержки, задним фронтом устанавливает триггеры 8 и 9 в нулевое состояние. Таким образом происходит сглаживание двух последовательных перемещений по разным координатам одним диагональным перемещением.

Следующий после сглаживания импульс с делителя частоты задним фронтом вновь устанавливает один из триггеров И, 9 в единичное состояние, и

дальнейшая ряботя ус1ппйствя л(ало гична описапио до тех пор, пока не будут обработаем приращения &Х, лУ. .пьсы с выходов X, У устройства поступают на входы блока 1 , где вычитаются из содержимого счетчиков 19 и 20, При оби лении счетчиков 19 и 20 на выходе элемента il -fiE 21 устанавливается нулевой потенциал, который прекращает работу генератора 2 импульсов. На этом интерполяция завершается.

Качество интерполяции предлагаемым устройстном повышается за счет уменьшения координатных погрешностей интерполяции, уменьшения угловых погрешностей интерполяции, а также однотипности и более равномерного размещения нерегулярностей, вносимых интерполяцией, по длине интерполируемого отрезка.

Формула изобретения

25 ка сортировки и сдвига чисел, выходы первого и второго делителей частоты подключены к входам установки первого и второго триггеров соответственно и к вторым входам второго и первоЛинейный интерполятор, содержащий генератор импульсов, два делителя частоты, блок пуска-останова, три триггера, два элемента И, элемент 2И-ИЛИ, два элемента КПИ, входы задания прира-ЗО го элементов И элемента 2И-ИЛИ, выход .щений первой и второй координат ин- элемента 2И-ИЛИ подключен к первому

7«,41

щрний перво и второй координат которого подключены к первому и второму входам признаков срабатывания блока пуска-останова, входы сброса первого и второго триггеров объединены, о т - л и ч 1 ю 01 и и с я тем, что, с целы повьгп1ения точности интерполяции, п него введены блок сортировки

)Q и сдвига чисел, четверть триггер, фаяосдвигатель и -элемент задержки, входы задания приратенш первой и второй координат интерполятора соединены с первым и вторым информацио1{-

15 ными-входами блока сортировки и сдвига чисел, первьм и второй выходы которого соединены с вторыми входами установки коэффициента деления первого и второго делителей частоты, так-

2Q TOBbie входы которых соединены с первым и вторым выходами фазосдвигателя, тактовый и управлякший входы которого соединены с выходом генератора импульсов и выходом признака сравнения бло-

25 ка сортировки и сдвига чисел, выходы первого и второго делителей частоты подключены к входам установки первого и второго триггеров соответственно и к вторым входам второго и первоЗО го элементов И элемента 2И-ИЛИ, выход элемента 2И-ИЛИ подключен к первому

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1986 |

|

SU1416940A1 |

| Линейный интерполятор | 1984 |

|

SU1249537A1 |

| Линейный интерполятор | 1989 |

|

SU1695267A1 |

| Интерполятор | 1985 |

|

SU1413600A1 |

| Цифровой интерполятор | 1985 |

|

SU1259217A1 |

| Устройство программного управления | 1984 |

|

SU1246055A1 |

| Устройство для программного управления | 1985 |

|

SU1249482A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для графического построения прямых с положительными приращениями. При этом повышается точность интерполяции за счет уменьшения координатных и угловых погрешностей интерполяции и более равномерного размещения нерегулярностей, вносимых интерполяцией, по длине интерполируемого отрезка. Интерполятор содержит блок 1 пуска-останова, генератор 2 импульсов, фазосдвигатель 3, делители 4 и 5 частоты, триггеры 6-9, элемент 10 задержки, элемент 2И-ИЛИ, элементы И 12, 13, элементы ИЛИ 14, 15, блок 16 сортировки и сдвига. 1 ил.

терполятора соединены с первым и вторым входами задания режима блока пуска-останова и с первыми входами установки коэффициента деления первого и второго делителей частоты соответственно, выходы которых соединены с первыми входами первого и второго элементов И, выходы первого и второго триггеров подключею) к первым входам первого и второго элементов И элемента 2И-ШШ, выход элемента 2И-ИЛИ соединен с первым входом первого элемента ИЛИ, вход запуска интерполятора

подключен к входу занесения признака 45 овки и выходы которых соединены с

режима блока пуска-останова, выход которого соединен с входом запуска генератора импульсов, выходы прира-

входу второго элемента ИЛИ и через элемент задержки - к объединенным входам сброса первого и второго триггеров, выходы которых подключены к вторым яходам первого и второго элементов И соответственно, выходы которых подключены к вторым входам первого и второго элементов ИЛИ, выходы

которых соединены с выходами приращений первой и второй координат интерполятора, вход запуска которого соединен с входами сброса третьего и четвертого триггеров, входы уставыходами и входами управления мультиплексированием коэффициентов деления первого и второго делителей частоты.

| Цифровой линейный интерполятор | 1975 |

|

SU551611A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Линейный интерполятор | 1984 |

|

SU1249537A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-23—Публикация

1986-11-17—Подача