(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Множительное устройство | 1981 |

|

SU1024909A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Множительное устройство | 1979 |

|

SU832554A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Последовательное множительное устройство | 1984 |

|

SU1233138A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение в вычислительных машинах и системах повьш1енной производительности. Цель изобретения повышение быстродействия. Устройство содержит два множительных блока 1 и 2, коммутатор 3 и элемент ИЛИ 4. Введенные элементы и связи позволяют организовать перекрестную подачу операндов на выходы блоков умножения, что в среднем на 10% повышает быстродействие устройства. 2 ил.

Фив,1

Изобретение относится к автомати- i ке и вычислительной технике и может найти применен1ие в вычислительных ма- шинах и системах повышенной произво- дительности.

Целью изобретения является повьпае- ние быстродействия устройства.

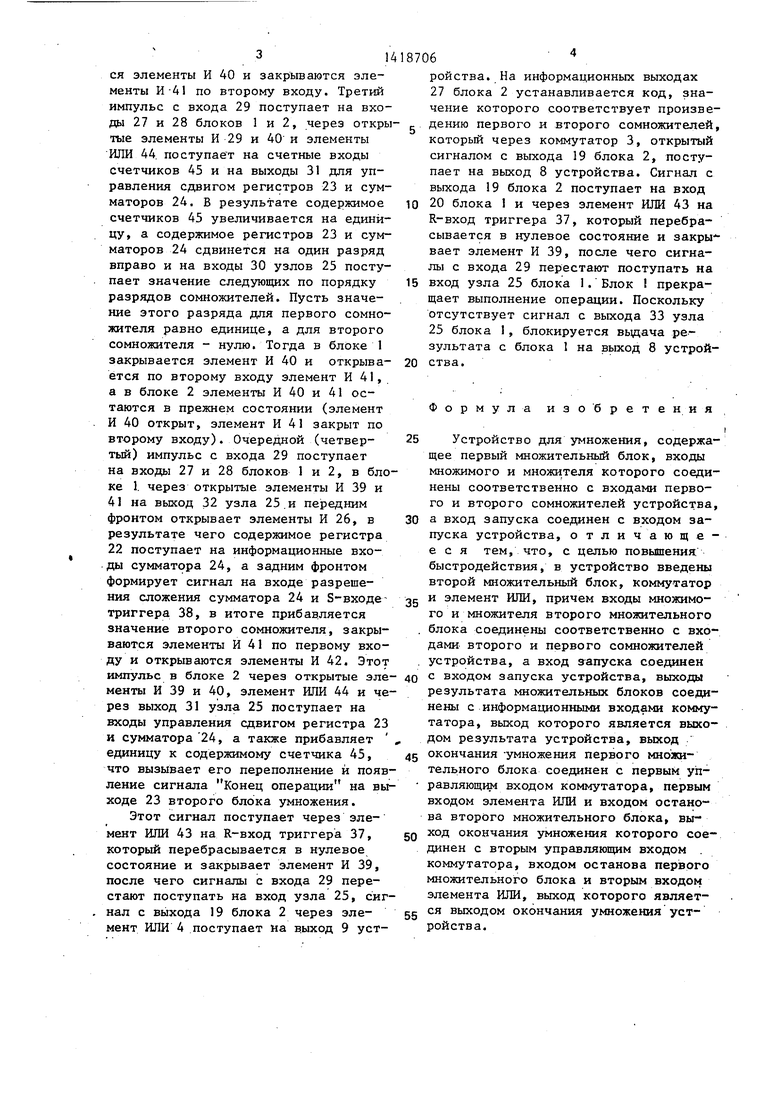

На фиг.1 представлена структурная схема предлагаемого устройства; на ФИГ.2 - функциональная схема узла уп- равления множительного блока. I Устройство для умножения (фиг.1) I содержит множительные -блоки 1 и 2, I коммутатор 3, элемент ИЛИ 4 входы 5 и 6 первого и второго сомножителей, I вход 7 запуска, выход 8 результата устройства и выход 9 окончания умно- ;жения..

I .Множительный блок 1.(2) имеет ВХОД 10 (11) множимого, вход 12 (13) {множителя, вход 14 ,(15) запуска, вы- |ход 16 (17) результата, выход 18 :(19) окончания умножения, вход 20 1(21) останова.

i На фиг.1 показан вариант выполне- |ния блока 1 (блок 2 выполнен анало- |гично). Этот блок содержит регист 22 {множимого, регистр 23 множителя, на- капливающий сумматор 24, узел 25 управления, группу элементов И 26, Кро- 1ме того, блок 1 имеет тактовый вход . ;27 (а блок 2 - соответственно.тактовый вход 28),, соединенный с тактовым входом 29 устройства.

Узел 4 блока 1 (фиг.2) имеет В5с6д 30, соединенный с выходом регистра 23, выход 31, соединенный с входами Управления сдвигом регистра 23 и. сумматора 24, выход 32, соединенный с входами стробирования элементов И 26 группы,и входом разрешения сложения . сумматора 24, выход 33, соединенный с выходом 18 блока 1, входы 34-36, соединенные соответственно с вxoдa IИ 27, 20 и 14 блока. 1., и содержащий триггеры 37 и 38, элементы И 39-42, элементы ИЛИ 43 и 44, счетчик 45 (узел управления блока 2 выполнен аналогично).

Устройство работает следующим образом.

В исходном состоянии в (п-1)-раз- 1 ыдных счетчиках 45 установлены значения - п, сумматоры 24 обнулены, в регистр 23 блока 1 через вход 12 и регистр 22 блока 2 через вход 11 занесен код первого сомножителя, в регистр 22 блока 1 Через и

i

. .

20

25

187062

регистр 23 блока 2 через вход 13 занесен код второго сомножителя. Триггеры 37 и 38 сброшены, элементы И 39 и 42 закрыты, элемент И 41 открыт по первому входу.

Запуск устройства осуществляется подачей импульса на вход 7, в результате, чего триггеры 37 перебрдсьшаютig ся в единичное состояние и открываются элементы И 39. Значение младшего разряда первого сомножителя поступает с регистра 23 через вход 30 узла 25 на инверсный вход элемента И 40 и

5 прямой вход элемента И 41 блока 1, а значение младшего разряда второго сомножителя - на аналогичные входы элементов И 40 и 41 блока 2. Вначале предположим, что значения .младших разрядов обоих сомножителей равны единице. Тогда элементы И 40 обоих блоков 1 и 2 закрыты, а элементы И 41 открыты по второму входу.

Первый импульс с входа 29 поступает на. входы 27 и 28 блоков 1 и .2 и через открытые элементы И 39 и 41 поступает на выходы 32 узла- 25 и передним фронтом открывает элементы И 26, в результате чего содержимое регистров 22 поступает на информационные входы сумматоров 24, а задним фронтом формирует сигнал на входе разрешения сложения сумматора 24 и S-входах триггеров 38. В итоге к нулевому содержимому сумматоров 24 блоков 1 и 2 прибавляется значение соответственно второго и первого сомножителей, закрываются элементы И 41 по первому входу и открьшаются элементы И 42. Второй импульс с входа 29 поступает на входы 27 и 28 блокод. 1 и 2 и через открытые элементы И 39 . и 42 своим передним фронтом посту- пают на R-входы триггеров 38, азад-;

дс ним - через элементы ИЛИ 44 - прибавляет единицу к содержимому счетчиков 45 и поступает на выходы 31 для управления сдвигом регистров 23 и сумматоров 24, в результате чего сдвигается на один разряд вправо содержимое регистров 23 и сумматоров 24, открываются элементы И 41 по первому входу, закрываются элементы И 42, на входы 30 узлов 25 блоков 1 и 2 поступает значение следующего разряда соответственно первого и второго сомножителей. Пусть теперь этр значение равно нулю для первого и второго сомножителя. Тогда открывают30

,35

40

50

55

ся элементы И 40 и закрьгеаются элементы И-41 по второму входу. Третий импульс с входа 29 поступает на входы 27 и 28 блоков 1 и 2, через откры тые элементы И 29 и 40 и элементы ИЛИ 44. поступае т на счетные входы счетчиков 45 и на выходы 31 для управления сдвигом регистров 23 и сумматоров 24. В результате содержимое счетчиков 45 увеличивается на единицу, а содержимое регистров 23 и сумматоров 24 сдвинется на один разряд вправо и на входы 30 узлов 25 поступает значение следующих по порядку разрядов сомножителей. Пусть значение этого разряда для первого сомножителя равно единице, а для второго сомножителя - нулю. Тогда в блоке 1 закрывается элемент И 40 и открыва- ется по второму входу элемент И 41, а в блоке 2 элементы И 40 и 41 остаются в прежнем состоянии (элемент И 40 открыт, элемент И 41 закрыт по второму входу). Очередной (четвер- тый) импульс с входа 29 поступает на входы 27 и 28 блоков 1 и 2, в блоке 1. через открытые элементы И 39 и 41 на выход 32 узла 25.и передним фронтом открывает элементы И 26, в результате чего содержимое регистра 22 поступает на информационные входы сумматора 24, а задним фронтом формирует сигнал на входе разрешения сложения сумматора 24 и S-входе- триггера 38, в итоге прибавляется значение второго сомножителя, закрываются элементы И 41 по первому входу и открываются элементы И 42. Этот импульс в блоке 2 через открытые эле менты И 39 и 40, элемент ИЛИ 44 и через выход 31 узла 25 поступает на входы управления сдвигом регистра 23 и сумматора 24, а также прибавляет единицу к содержимому счетчика 45, что вызывает его переполнение и появление сигнала Конец операции на выходе 23 второго блока умножения.

Этот сигнал поступает через элемент ИЛИ 43 на R-вход триггера 37, который перебрасывается в нулевое состояние и закрывает элемент И 39, после чего сигналы с входа 29 перестают поступать на вход узла 25, сигнал с выхода 19 блока 2 через эле- мент ИЛИ 4 поступает на выход 9 устройства. На информационных выходах 27 блока 2 устанавливается код, значение которого соответствует произведению первого и второго сомножителей, который через коммутатор 3, открытый сигналом с выхода 19 блока 2, поступает на выход 8 устройства. Сигнал с выхода 19 блока 2 поступает на вход 20 блока 1 и через элемент ИЛИ 43 на R-вход триггера 37, который перебрасывается в нулевое состояние и закры- вает элемент И 39, после чего сигналы с входа 29 перестают поступать на вход узла 25 блока 1. Блок 1 прекращает выполнение операции. Поскольку отсутствует сигнал с выхода 33 узла 25 блока I, блокируется выдача результата с блока 1 на выход 8 устройства.

Формула изобретения

Устройство для умножения, содержащее первый множительный блок, входы множимого и множителя которого соединены соответственно с входами первого и второго сомножителей устройства, а вход запуска соединен с входом запуска устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены второй множительный блок, коммутатор и элемент ИЛИ, причем входы множимого и множителя второго множительного блока соединены соответственно с входами второго и первого сомножителей устройства, а вход запуска соединен с входом запуска устройства, выходы результата множительных блоков соединены с информационными входами коммутатора, выход которого является выходом результата устройства, выход окончания -умножения первого мно жи- тельного блока соединен с первым уп- равляющ1Ф1 входом коммутатора, первым входом элемента ИЛИ и входом останова второго множительного блока, выход окончания умножения которого соединен с вторым управляющим входом . коммутатора, входом останова первого множительного блока и вторым входом элемента ИЛИ, выход которого является выходом окончания умножения устройства.

Составитель В.Березкин Редактор Г.Волкова Техред И. Верес i Корректор Г.Решетник

Заказ 4154/46

Тираж 704

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Преснухин Л.Н | |||

| и Нестеров П.В | |||

| Цифровые вычислительные машины | |||

| - М.: Высшая школа, 1974, с | |||

| Крутильно-намоточный аппарат | 1922 |

|

SU232A1 |

| Майоров С.А | |||

| и Новиков Г.И | |||

| Принципы организации цифровых машин | |||

| - Л.: Машиностроение, 1974, с | |||

| РАССЕИВАЮЩИЙ ТОПЛИВО МЕХАНИЗМ | 1920 |

|

SU298A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-08-23—Публикация

1987-02-09—Подача