(54) МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения десятич-НыХ чиСЕл | 1979 |

|

SU817704A1 |

| Устройство для умножения | 1978 |

|

SU771669A1 |

| Устройство для умножения десятичных чисел | 1976 |

|

SU652560A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Вычислительное устройство | 1986 |

|

SU1327118A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1973 |

|

SU409222A1 |

1

Изобретение относится к вычислительной технике и может быть исполь зовано при построении двоично-десятичных арифметических устройств.

Известно устройство умножения десятичных чисел,содержащее регистр множимого, блок последовательного накопления чисел, кратных множимому, блок сдвигаг блок суммирования ча.стичных произведений, регистр множителя , блок определения очередности цифр 11 .

Недостатком известного устройства является его сложность.

Наиболее близким техническим решением является устройство для умножения десятичных чисел, содержащее десятичный сумматор, регистр-преобразователь, информационный выход которого подключен к информационному входу сумматора, регистр операнда, информационный выход которого подк бочен к информаЦирнному входу старших десятичных разрядов регистра преобразователя, информационный выход младших десятичных разрядов которого подключен к информационному входу регистра операнда, регистр множителя и блок управления, выход сложения которого подключен к управляющему

входу сложения десятичного сумматора, выход преобразования блока управления подсоединен к первому управляющему входу регистра-преобразователя, второй управляющий вход которого соединен со входом сдвига регистра множителя и с выходом управления сдвигом блока управления, выход управления приемом в регистр операнда ко0торого подсоединен ко входу приема регистра операнда 2.

Недостаток устройства - большое время выполнения операции умножения десятичных чисел.

5

Цель изобретения - увеличение быстродействия известного устройства.

Поставленная цель достигается тем, что множительное устройство, содер0жащее десятичный сумматор, регистр удвоенного операнда, регистр операнда, информационный выход которого подключен к информационному входу мпадцоих десятичных разрядов регистра

5 удвоенногооперанда, регистр множителя и блок управления, выход сложения которого соединен с управляющим входом сложения десятичного сумматора, выход преобразования блока

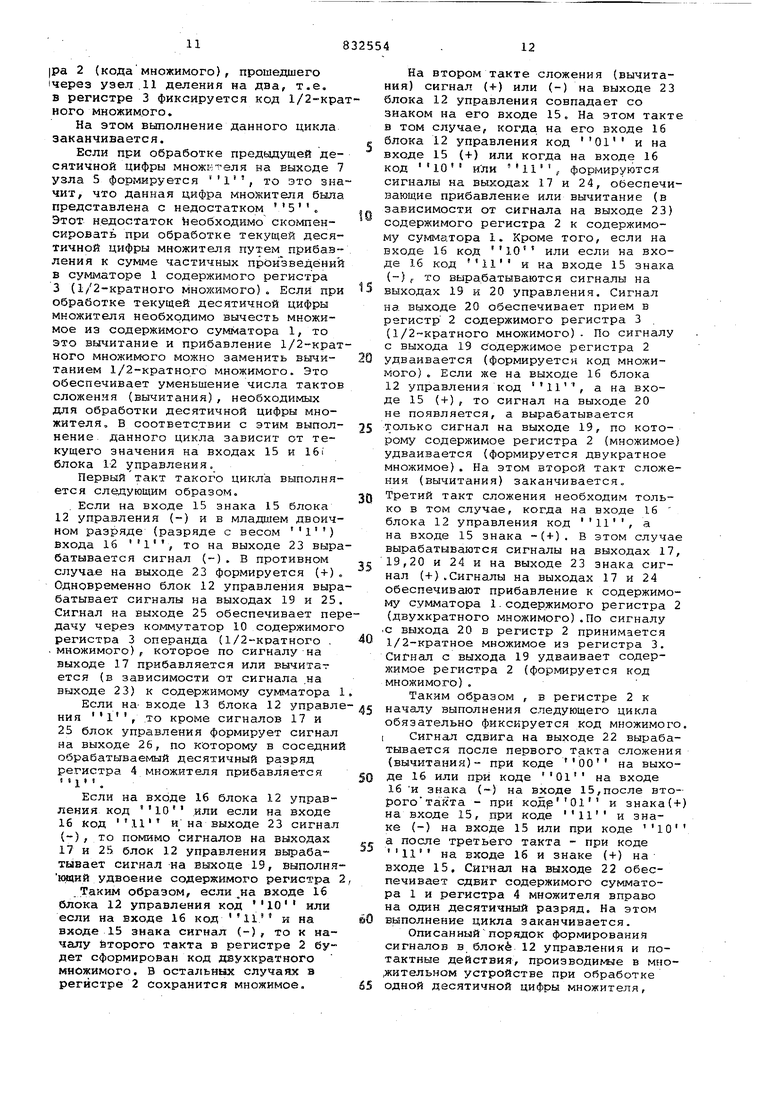

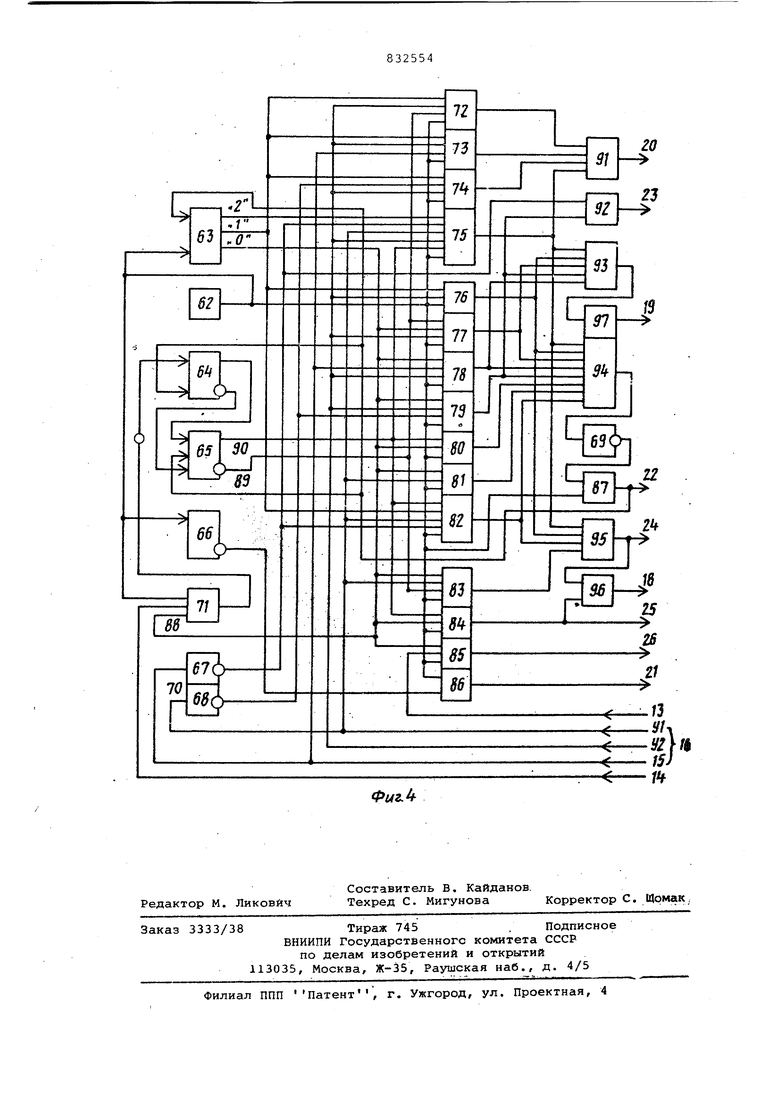

0 управления подключен к первому управляющему входу регистра удвоенного операнда, второй управляющий вход которого соединен с выходом управления приемом в регистр удвоенного операнда блока управления, выход управления приемом в регистр операнда которого подсоединен ко входу приема в регистр операнда, выход управления сдвигом блока управления подключен ко входам сдвига десятичного , сумматора и регистра множителя, дополнительно содержит KoiviMyraTop, узел деления на два и узел преобразо вания цифры, причем выход управления операцией блока управления подклю.чен ко входу управления операцией десятичного сумматора, информационный вход которого соедине-н с выходом кo лмyтaтopa, первый информационный вход которого подсоединен к выходу регистра удвоенного операнда и ко входу Узла Д1 еления на два, выкод которого подключен к информационному входу регистра операнда, выход которого соединен со вторым информационным входом коммутатора, первый и второй управляющие входы которого подключены соответственно к первому и второму выходам управле ния передачей в сумматор блока управления, первый и второй .управляющие входы которого соединены соот, ветственно с первым и вторым, управл ющими выходами узла преобразования цифры, выход знака которого подключен ко входу знака блока управления информационный вход которого с весами 1 и 2 подсоединен к двухразрядному с весами i и 2 информационному выходу узла преобра зования цифры, четырех-разрядный информационный вход которого с весоединен с выходом младшего десятич ного разряда регистра множителя, уп равляющий вход которого подключен к выходу прибавления единицы блока уп равления. Кроме того, узел преобразования, цифры содержит восемь элементов И, пять элементов ИЛИ и три элемента Н вход первого элемента НЕ под ключен к двоичному разряду с весом 1 информационного входа узла пр образования цифры и к первым входам первого и второго элементов И, выходы которых соединены соответствен но с первым и вторым входами первог элемента ИЛИ, третий вход которого соединен с выходом третьего элемента И, первый вход которого подключен к выходу первого элемента НЕ и к первому входу четвертого эле| 1ента И, выход которого подсоединен к пер вому входу второго элемента ИЛИ, вт рой вход которого подключен к ВЕЛХОду второго элемента И, второй вход которого соединен с двоичным разрядом о весом информационного входа узла преобразования цифры, со входом второго элемента НЕ и первым входом пятого элемента И, выход которого подключен к третьему входу торого элемента ИЛИ, а второй вход ко второму входу первого элемента И и выходу третьего элемента НЕ., вход которого соединен с .двоичным разрядом с весом М информационного входа узла преобразователя цифры, вторым входом третьего элемента И и первым входом шестого элемента И, второй вход которого подключен ко входу второго элемента НЕ, выход которого подсоединен к первьп-5 входам седьмого и восьмого элементов И, вторые входы которых соединены с первым входом шестого элемента И, третий ВХОД которого подключен ко входу первого элемента НЕ, выход которого подсоединен к третьему входу седьмого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И и первым входом четвертого элемента ИЛИf второй вход которого подключен к третьему входу третьего элемента ИЛИ; второму входу четвертого элемента Ник двоичному разряду с весом 8 информационного входа узла преобразования цифры, выход восьмого элемента И которого соединен с первым входом пятого элемента ИЛИ, второй вход которого подсоединен к третьему входу первого элемента ИЛИ выход которого соединен с двоичным разрядом с весом i информационного выхода узла преобразования цифры, двоичный разряд с,весом 2 которого подключен к выходу второго элемента ИЛИ, выходы третьего, четвертого и пятого элементов ИЛИ соединены соответственно с выходом знака и первым и вторым управляющими выходами узла преобразования цифры. При этом блок управления содержит генератор тактов, двухразрядный двоичный счетчик, три триггера, три эле.мента НЕ, семнадцать элементов И, шесть элементов ИЛИ и элемент задержки, причем первый и второй выходы первого триггера подсоединены к первому и второму входам второго триггера, третий вход которого соединен с установочным входом двоичного счетчика, счетный вход которого подключен ко входу третьего триггера, выходу генератора тактов и первым входом первого -. семнадцатого элементов И, йторой вход первого элемента И подключен к выходу О двоичного счетчика, выход первого разряда подсоединен ко вторым входам второго четвертого элшутеитов И, третий вход второго элемента И соединен с первым выходом второго триггера, второй выход которого подключен ко второму вкоду пятого элемента И, третий вход которого подсоединен к выходу двоичного счетчика, выход кото рого соединен со вторым входом шест го элемента И, третий вход которого подсоединен к четвертым входам втор го и пятого элементов И, третьим входам третьего и четвертого элемен тов И, вторым входам седьмого - дев того элементов Ник двоичному разр ду веса 2 информационного входа блока управления, разряд веса которого соединен с пятым входом пятого элемента И, шестой вход кото рого подключен к выходу первого эле мента ЕШ, вход которого подсоединен ко входу знака блока управления, че вертому входу третьего элемента И и к третьему входу восьмого элемента И, четвертый вход которого соединен с вь:. О двоичного счетчика, третьими входами седьмого и девятог элементов И и вторыми входами десятого и одиннадцатого элементов И, третий вход десятого элемента И подсоединен ко второму входу двенадцатого элемента И и ко второму ВЕз1ходу второго триггера, первый выход которого подключен к четвертому входу седьмого элемента И и второму входу тринадцатого элемента И, третий вход которого соединен со вторыми входами четырнадцатого и пятнадцатого элемен тов И и с третьим входом девятого элемента И, четвертый вход которого подсоединен к четвертому входу четвертого элемента И и к выходу второг элемента НЕ, вход которого соединен инфор с двоичным разрядом веса мационного двухразрядного входа блока управления, с третьим входом один надцатого элемента И, четвертым входом тринадцатого элемента И и третьим входом двенадцатого элемента И, второй вход которого подключен к третьему входу четырнадцатого элемента И, выход которого соединен со вторым выходом управления передачей в сумматор блока управления,первый управляющий вход которого подключен к третьему входу пятнадцатого элемента И, выход которого соединен с выходом прибавления единицы блока управления, второй управляющий вход которого соединен с третьим входом первого элемента И, выход KOTopoio подключен к первому входу первого триггера, выход третьего триггера соединен со вторым входом шестнадцатого элемента И, выход которого подключен к выходу управления приемом в регистр операнда блока управления, выход управления сдви гом которого подсоединен к выходу семнадцатого элемента И, второму входу первого триггера к установочнЪму йходу двоичного счетчика, выкоторого соединен с четвертым входом двенадцатого элемента И, пятый вход которого подключен к выходу первого элемента НЕ, первый четвертый входы первого элемента ИЛИ соединены соответственно с выходами второго - пятого элементов И, а - с выходом разрешения приема в регистр удвоенного операнда блока управления, выход управления операцией которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого элемента НЕ и девятого элемента И, первый пятый входы третьего элемента ИЛИ подключены к выходам пятого - девятого элементов И, первый - восьмой входы четвертого элемента ИЛИ соединены соответственно с выходами пятого - двенадцатого элементов И, а выход - через третий элемент НЕ со вторым входом Семнадцатого элемента И, первый - четвертый входы пятого элемента ИЛИ соединены соответственно с выходами пятого,шестого двенадцатого и тринадцатого элементов И,а выход- спервым выходом управления передачей в су лматор блока управления, выход сложения которого соединен с выходом шестого элемента ИЛИ, первый и второй входы которого подключены к выходам пятого элемента ИЛИ и четырнадцатого SjieMeHTa И, выход третьего элемента ИЛИ через элемент за- , держки соединен с выходом преобразования блока управления, - На фиг. 1 изображена структурная схема множительного устройства; на фиг. 2 - схема узла преобразования цифры; на фиг. 3 - схема одного десятичного разряда узла деления на два на фиг. 4 - схема блока управления. Множительное устройство выполняет операцию умножения двоично-.десятичных чисел, представленных .в коде 8-4-2-1, по варианту, при котором производится сдвиг частичных произведений при неподвижном множимом. Устройство включает десятичный сумматор 1, содержащий {2пч-1) десятичный разряд, где п - разрядность сомножителей; регистр 2 удвоенного операнда, содержащий (п+2) десятичных разрядов; регистр 3 операнда, содержащий (п+1) десятичный разряд, информационный выход которого подключен к информационному входу младших (n+l) десятичных разрядов регистра 2; регистр 4 множителя, содержащий (п+1) десятичный разряд, причем старшие разрядов выполнены десятичных счетчиков; узел 5 преобразо- . вания цифры, имеющий первый и второй управляющие выходы 6 и 7, выход 8 знака и двухразрядный информационный выход 9, четырехразрядный вход узла 5 подключен к выходу младшего десятичного разряда регистра множителя; комутатор 10, информационный выход которого соединен с информационными входами (п+1) старших десятичных

разрядов сумматора 1, первый и второй .информационные входы коммутатора, 10 соединены соответственно с выходами регистра 2 у-двоенного операнда и регистра 3; узел 11 деления на два, вход которого подключен к информационному выходу регистра 2 .удвоенного операнда, а вьцсод - к информационному входу регистра 3 операнда; блок 12 управления, первый и второй управляющие входы 13 и 14 которогс соединены соответственно с первым и вторым,управляющими выходами б и 7 узла 5 преобразования цифры, выход 8 знака которого подключен ко входу 15 знака блока 12 управления, информационный двухразрядный вход 16 которого подсоединен к информационному выходу 9 узла 5, выход 17 сложения блока управления подключен к управляющему входу 18 сложения сумматора 1, выход 19 преобразования блока 12 управления подключен к первому управляющему входу регистра 2 удвоенного операнда, второй управляющий вход которого соединен с выходом 20 управления приемом в регистр 2 удвоенного операнда блока 12 управления, выход 21 управления приемом в регистр oneранда которого подсоединен ко входу приема регистра 3 операнда, выход 22 управления сдвигом блока 12 управления подключен ко входам сдвига сумматора 1 и регистра 4 множителя,

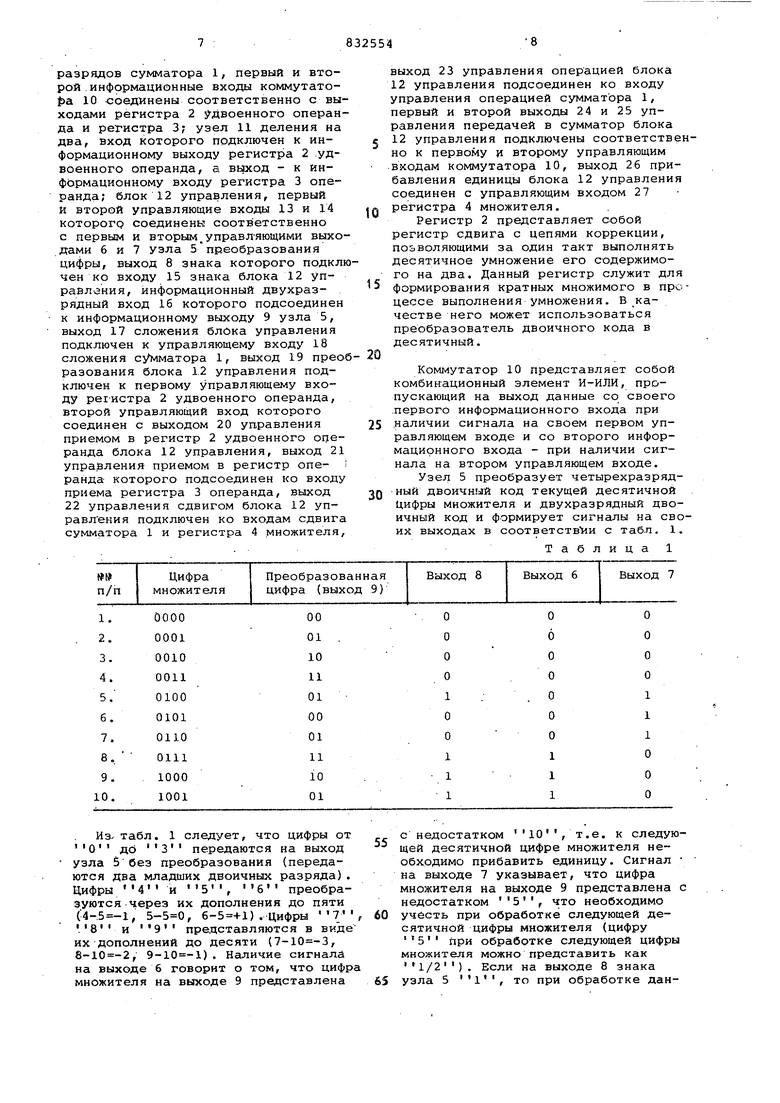

Изх табл. 1 следует, что цифры от О до 3 передаются на выход узла 5 без преобразования (передаются два младших двоичных разряда). Цифры 4 и 5 , 6 преобразуются-через их дополнения до пяти (-4-., , ) .Цифры 7

В

9

представляются в виде

и

их дополнений до десяти (, , ). Наличие сигнала на выходе 6 говорит о том, что цифр множителя на выходе 9 представлена

выход 23 управления операцией блока 12 управления подсоединен ко входу управления операцией сумматора 1, первый и второй выходы 24 и 25 управления передачей в сумматор блока 12 управления подключены соответствено к первому и второму управляющим входам коммутатора 10, выход 26 прибавления единицы блока 12 управления соединен с управляющим входом 27 регистра 4 множителя.

Регистр 2 представляет собой регистр сдвига с цепями коррекции, позволяющими за один такт выполнять десятичное умножение его содержимого на два. Данный регистр служит для формирования кратных множимого в процессе выполнения умножения. В качестве него может использоваться преобразователь двоичного кода в десятичный.

Коммутатор 10 представляет собой комбинационный элемент И-ИЛИ, пропускающий на выход данные со своего .первого информационного входа при .наличии сигнала на своем первом управляющем входе и со второго информационного входа - при наличии сигнала на втором управляющем входе.

Узел 5 преобразует четырехразрядный двоичный код текущей десятичной Цифры множителя и двухразрядный двоичный код и формирует сигналы на своих выходах в соответствии с таб.п. 1

Таблица

с недостатком 10,т.е. к следующей десятичной цифре множителя необходимо прибавить единицу. Сигнал на выходе 7 указывает, что цифра множителя на выходе 9 представлена с

что необходимо

недостатком

учесть при обработке следующей десятичной цифры множителя (цифру 5 при обработке следующей цифры множителя можно представить как 1/2 ) . Если на выходе 8 знака узла 5 , то при обработке данной десятичной цифры нужно выполни вычитания, О - сложен.ия. Множительное устройство работае следующим образом. В исходном состоянии в десятичны разряды (2-п) регистра 2 помещено множимое, в младшие п разрядов рег стра 4 - множитель. Операнды предс лены в коде 8-4-2-1. Старший и млад ший десятичные разряды регистра 2, старший десятичный разряд регистра сумматор.1 и регистр 3 установлены в нуль. Выполнение операции умножения ос ществляется за (п+1) цикл. На каждо цикле обрабатывается одна десятична цифра множителя, начиная с младшей каждый цикл выполняется за 0,1,2 ил 3 такта сложения (вычитания) в зависи ости от значения текущей десятичной цифры множителя и сигнала, сформированного на выходе 7 узла 5 при обработке пред,ыдущей десятичной цифры множителя. Если при 9бработке предыдущей десятичной цифры множителя на выходе узла 5 был сформирован О, то данный цикл выполняется следующим о разом. Узел 5 преобразования цифры анализирует текущую десятичную цифру множителя и в зависимости от ее значения в соответствии с табл. 1 формирует сигналы на своих выходах 6-9, поступающие на соответствующие входы 13-16 блока 12 управления. Блок 12 управления анализирует значение знака на своем входе 15 зн ка и,если знак положителен,формируе сигнал(+) на выходе 23,поступающий вход управления операцией сумматора 1 и обеспечивающий выполнение сложения в сумматоре. Если же знак на входе 15 отрицателен, то на выходе 23 блока управления вырабатывается сигнал (-) , поэтому в суммаюре 1 будет выполнено вычитание. Первый такт цикла выполняется в зависимости от кода/ поступившего на информационный вход 16 блока 12 управления. Если на входе 16 код 01, то на первом такте блок управления фор мирует сигналы на выходах 17 и 24. Сигнал на выходе 24 обеспечивает пе редачу через коммутатор 10 на вход сумматора 1 содержимого регистра 2 (кода множимого). По сигналу с выхо да 17 выполняется сложение или вычи тание (в зависимости от сигнала на выходе 23 блока 12 управления) кода с выхода коммутаторГа с содержимым сумматора. Если на входе 16 блока 12 управл ния код 11, то кроме сигналов на входах 17 и 24 вырабатывается Ъще Сигнал на выходе 19 блока управ ления. Сигнал на выходе 19 формируе ся с задержкой, равной времени -npfiема кода в регистр 2. Данный сигнал поступает на первый управляющий вход регистра 2 и обеспечивает удвоение его содержимого (в регистре-преобразователе формируется код двухкратного множимого). Если на входе 16 Спока 12 управления код 10 , то блок 12 управления формирует лишь сигнал на выходе 19, же на выходах 17 и 24 не вырабатываются. Одновременно, если на входе 13 блока 12 управления присутствует , то блок управления формируют сигнал на выходе 26. Сигнал с выхода 26 поступает на управляющий вход регистра 4 множителя и обеспечивает прибавление в соседний с обрабатываемым десятичный разряд множителя. На первом такте первого цикла кроме вышеназванных сигналов блок 12 управления формирует сигнал на выходе 21. Этот сигнал поступает на вход приема регистра 3 операнда и обеспечивает прием в регистр 3 содержимого регистра 2 (кода множимого), прошедшего через узел 11 депения на два.° Таким образом в регистре 3 фик-. сируется код 1/2-кратного множимого, Второй такт сложения-вычитания выполняется в том случае, если старшая двоичная цифра (цифра с весом 2) на входе 16 блока 12 управле. В этом случае блок ния равна 12 управления формирует сигналы на выходах 17,19,20,24. Сигналы на выходах 17 и 24 выполняют действия, описанные выше для первого такта (к содержимому сумматора 1 прибавляется или вычитается в зависимости от сигнала на выходе 23 двукратное множимое). Сигнал на выходе 20 обеспечивает прием в регистр 2 содержимого регистра 3 операнда (1/2-кратного множимого). Сигнал на выходе 19 формируется через время, достаточное для приема кода в регистр 2 и обеспечивает удвоение его содержимого.. Таким образом, к началу обработки следующей десятичной цифры множителя в регистре 2 будет зафиксирован код множимого. Сигнал сдвига на выходе 22 блок 12 управления формирует вместо первого такта сложения (вычитания) - при коде ,00 насвоем информационном входе 16, после первого такта сложения (вычитания) - при коде 01 на входе 16, после второго такта 11 .. Сигнал при кодах на выходе 22 обеспечивает сдвиг вправо на один десятичный разряд содержимого сумматора 1 и регистра 4. Если при выполнении первого цикла на входе 16 блока 12 управления присутствует код 00, то одновременно с сигналом на выходе 22 блок 12 управления вырабатывает сигнал на выходе 21. Этот сигнал обеспечивает прием в регистр 3 содержимого регнст|ра 2 (кода множимого), прошедшего |череэ узел .11 деления на два, т.е. в регистре 3 фиксируется код 1/2-кра ного множимого. На этом вьшолнение данного цикла заканчивается. Если при обработке предыдущей десятичной цифры множителя на выходе узла 5 формируется , то это зна чит, что данная цифра множителя была представлена с недостатком 5. Этот недостаток Необходимо скомпенсировать при обработке текущей десятичной цифры множителя пут-ем прибаз ления к сумме частичных прОизведённ в сумматоре 1 содержимого регистра 3 (1/2-кратного множимого). Если при обработке текущей десятичной цифры множителя необходимо вычесть множимое из содержимого сумматора 1, то это вычитание и прибавление ного множимого можно заменить вычитанием 1/2-кратного множимого. Это обеспечивает уменьшение числа такто сложения (вычитания), необходимых для обработки десятичной цифры множителя, В соответствии с этим выпол нение . данного цикла зависит от текущего значения на входах 15 и 161 блока 1-2 управления. Первый такт такого цикла выполня ется следующим образом. Если на входе 15 знака 15 блока 12 управления (-) и в младшем двоич ном разряде (разряде с весом ) входа 16 , то на выходе 23 выр батывается сигнал (-). В противном случа.е на выходе 23 формируется ( + ) Одновременно блок 12 управления выр батывает сигналы на выходах 19 и 25 Сигнал на выходе 25 обеспечивает пе дачу через коммутатор 10 содержимог регистра 3 операнда (1/2-кратного . . множимого), которое по сигналу на выходе 17 прибавляе тся или вычитат ется (в зависимости от сигнала ,на выходе 23) к содержимому сумматора Если на- входе 13 блока 12 управл ния , то кроме сигналов 17 и 25 блок управления формирует сигнал на выходе 26, по которому в соседни обрабатываемый десятичный разряд регистра 4 множителя прибавляется Если на входе 1б блока 12 управили если на входе ления код 16код 11 и на выходе 23 сигнал (-), то помимо сигналов на выходах 17и 25 блок 12 управления вырабатывает сигнал на выходе 19, выполня нкций удвоение содержимого регистра Таким образом, если на входе 16 блока 12 управления код 10 или если на входе 16 код 11 и на входе 15 знака сигнал (-), то к началу второго такта в регистре 2 будет сформирован код двухкратного множимого. В остальных случаах в регистре 2 сохранится множимое. На втором такте сложения (вычитания) сигнал (Ч-) или (-) на выходе 23 блока 12 управления совпадает со знаком на его входе 15. На этом такте в том случае, когда на его входе 16 блока 12 управления код 01 и на входе 15 (+) или когда на входе 16 формируются сигналы на выходах 17 и 24, обеспечивающие прибавление или вычитание (в зависимости от сигнала на выходе 23) содержимого регистра 2 к содержимому сумматора 1. Кроме того, если на входе 16 код 10 или если на входе 16 код 11 и на входе 15 знака (-)f то вырабатываются сигналы на выходах 19 и 20 управления. Сигнал на выходе 20 обеспечивает прием в регистр 2 содержимого регистра 3 . (1/2--кратного множимого). По сигналу с выхода 19 содержимое регистра 2 удваивается (формируется код множимого) . Если же на выходе 16 блока 12 управления код 11, а на входе 15 (+), то сигнал на выходе 20 не появляется, а вырабатывается только сигнал на выходе 19, по которому содержимое регистра 2 (множимое) удваивается (формируется двукратное множимое). На этом второй такт сложения (вычитания) заканчивается. Третий такт сложения необходим только в том случае, когда на входе 16 блока 12 управления код 11, а на входе 15 знака -(+). В этом случае вырабатываются сигналы на выходах 17, 19,20 и 24 и на выходе 23 знака сигнал (+.Сигналы на выходах 17 и 24 обеспечивают прибавление к содержимому сумматора 1.содержимого регистра 2 (двухкратного множимого).По сигналу с выхода 20 в регистр 2 принимается 1/2-кратное множимое из регистра 3. Сигнал с выхода 19 удваивает содержимое регистра 2 (формируется код множимого). Таким образом , в регистре 2 к началу выполнения следующего цикла обязательно фиксируется код множимого. I Сигнал сдвига на выходе 22 вырабатывается после первого такта сложения (вычитания)- при коде 00 на выхоДб 16 или при коде на входе 16 И знака (-) на входе 15,после второго такта - при кодр01 и знака(+) на входе 15, при коде 11 и знаке (-) на входе 15 или при коде lOV а после третьего такта - при коде 11 на входе 16 и знаке (+) на входе 15, Сигнал на выходе 22 обеспечивает сдвиг содержимого сумматора 1 и регистра 4 множителя вправо на один десятичный разряд. На этом выполнение цикла заканчивается. Описанный порядок формирования сигналов в блок4 12 управления и потактные действия, производи «е в мноркительном устройстве при обработке одной десятичной цифры множителя.

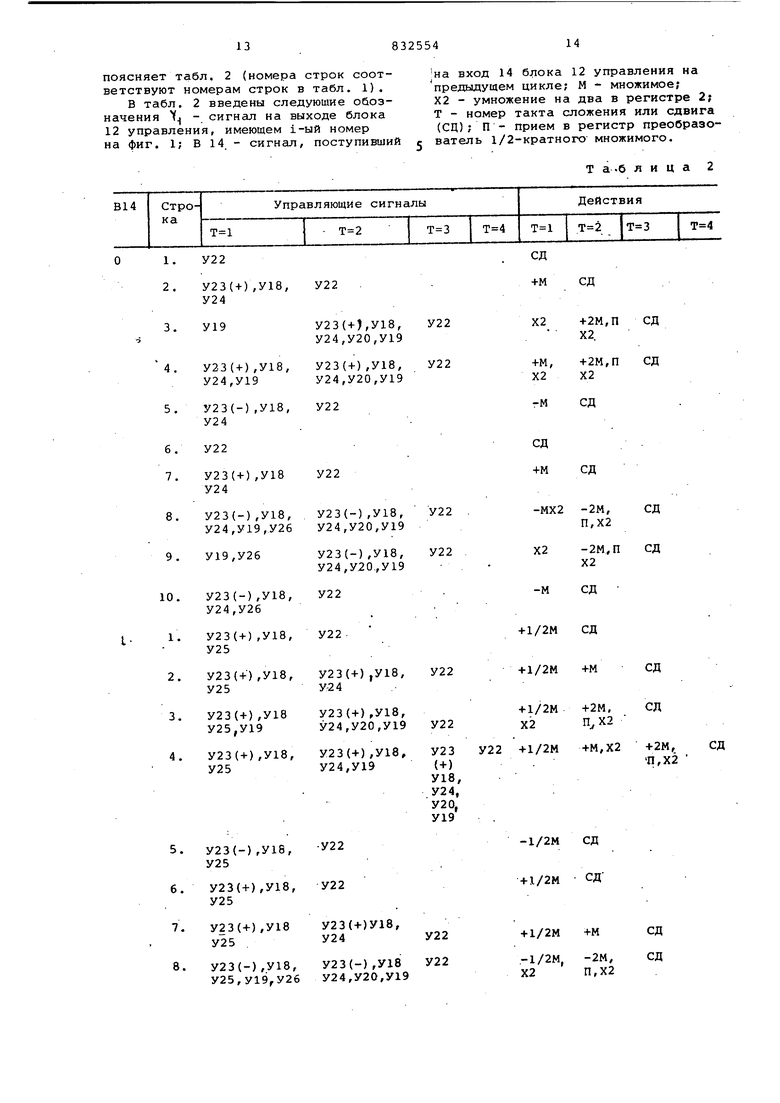

поясняет табл. 2 (номера строк соответствуют номерам строк в табл. 1).

В табл. 2 введены следующие обозначения - сигнал на выходе блока 12 управления, имеющем i-ый номер на фиг. 1; В 14 - сигнал, поступивший

У22

У23(+),У18,

У22 У24

У23(+),У18,

У19 У24,У20,У19

У23(+),У18,

У2.3( + ) ,У18, У24,У20,У19 У24,У19

У22

У23(-),У18, У24

б,

У22

У22

У23(+),У18

7, У24

У23(-),У18,

У23{-),У18, У24,У20,У19 У24,У19,У26

У23(-),У18,

У19,У26 У24,У20.,У19

У22

У23(-),У18,

0, У24,У2б

У22

У23(+),У18, У25

У23(+).У18,

У23{+) ,У18, У-24 У25

У23(+),У18,

У23(+),У18 У24,У20,У19 У25,У19

У23(+),У18,

У23(+),У18, У24,У19 У25

У22

У23(-),У18, У25

У22

У23(+),У18, У25

У23(+)У18,

У23(+),У18

У24 У22 У25

У23(-),У18 У22

У23(-),У18, У24,У20,У19 У25,У19,У26

на вход 14 блока 12 управления на предыдущем цикле; М - множимое; Х2 - умножение на два в регистре 2; Т - номер такта сложения или сдвига (СЦ); П - прием в регистр преобразователь 1/2-кратного множимого.

Т а-б л и ц а 2

СД

СД +М

+2М,П

Х2

22

СД Х2.

+2М,П

СД

22

+М, Х2 Х2

СД

-М

СД

+М СД

-МХ2 -2М,

СД СД

П,Х2

Х2 -2М,П Х2

СД

-М

+1/2М СД

СД

+1/2М +М

У22

+ 1/2М

+2М,

СД Х2

СД

+2М,

У22 +1/2М +М,Х2 П,Х2

СД

СДСД СД

+М

-2М,

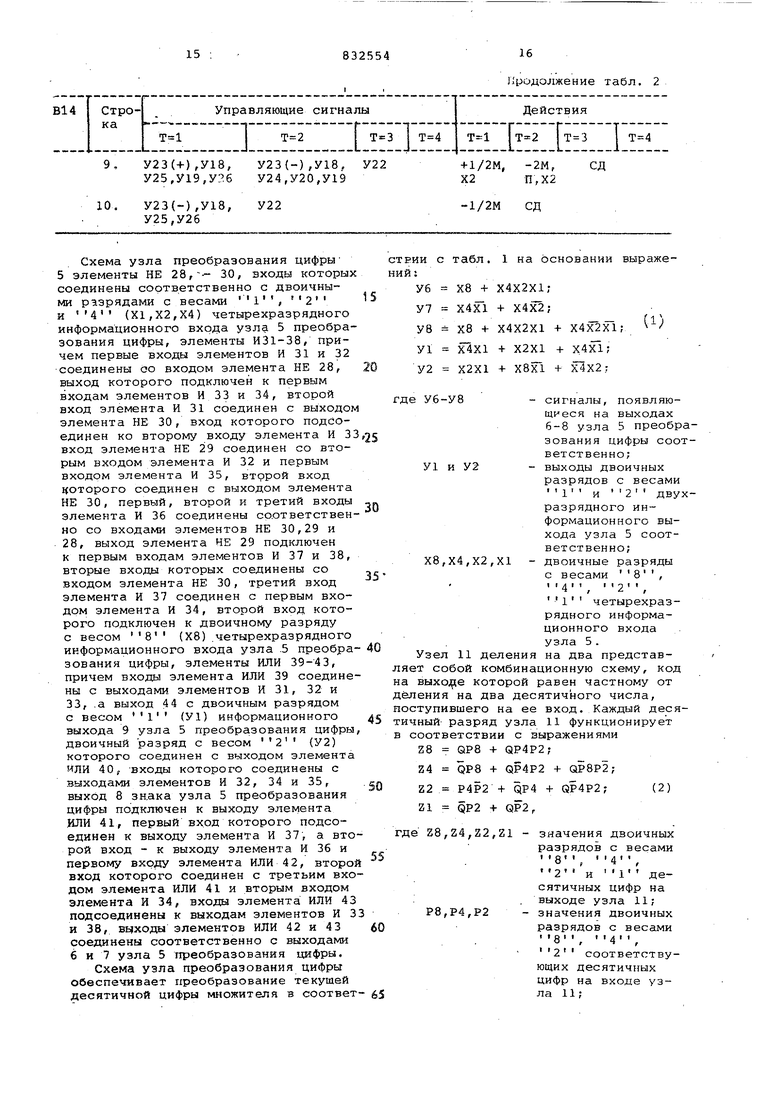

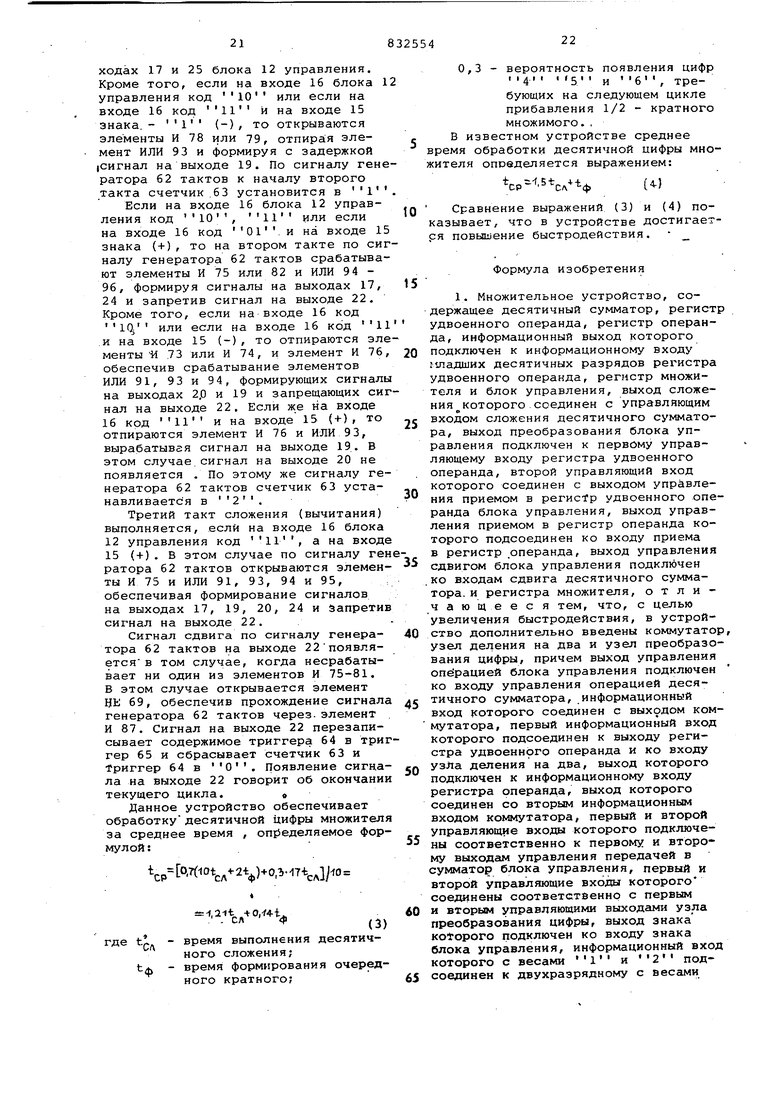

П,Х2 Схема узла преобразования цифры 5 элементы НЕ 28,-- 30, входы которых соединены соответственно с двоичны(Х1,Х2,Х4) четырехразрядного информационного входа узла 5 преобра зования цифры, элементы И31-38, причем первые входы элементов И 31 и 32 соединены оо входом элемента НЕ 28, выход которого подключен к первым входам элементов И 33 и 34, второй вход элемента И 31 соединен с выходом элемента НЕ 30, вход которого подсоединен ко второму входу элемента И 3 вход элемента НЕ 29 соединен со вторым входом элемента И 32 и первым входом элемента И 35, втррой вход ifOTOporo соединен с выходом элемента НЕ 30, первый, второй и третий входы элемента И 36 соединены соответствен но со входами элементов НЕ 30,29 и 28, выход элемента НЕ 29 подключен к первым входам элементов И 37 и 38, вторые входы которых соединены со входом элемента НЕ 30, третий вход элемента И 37 соединен с первым входом элемента И 34, второй вход которого подключен к двоичному разряду с весом 8 (Х8) .четырехразрядного информационного входа узла .5 преобра зования цифры, элементы ИЛИ 39-43, причем входы элемента ИЛИ 39 соедине ны с выходами элементов И 31, 32 и 33, .а выход 44 с двоичным разрядом с весом (У1) информационного выхода 9 узла 5 преобразования цифры двоичный разряд с весом которого соединен с выходом элемента ИЛИ 40, ВХОДЫ которого соединены с выходами элементов И 32, 34 и 35, выход 8 зн.ака узла 5 преобразования цифры подключен к выходу элемента ИЛИ 41, первый вход которого подсоединен к выходу элемента И 37, а вто рой вход - к выходу элемента И 36 и первому входу элемента ИЛИ 42, второ вход которого соединен с третьим вхо дом элемента ИЛИ 41 и вторым входом элемента И 34, входы элемента ИЛИ 43 подсоединены к выходам элементов И 3 и 38, выходы элементов ИЛИ 42 и 43 соединены соответственно с выходами 6 и 7 узла 5 преобразования цифры. Схема узла преобразования цифры обеспечивает преобразование текущей десятичной цифры множителя в соответ

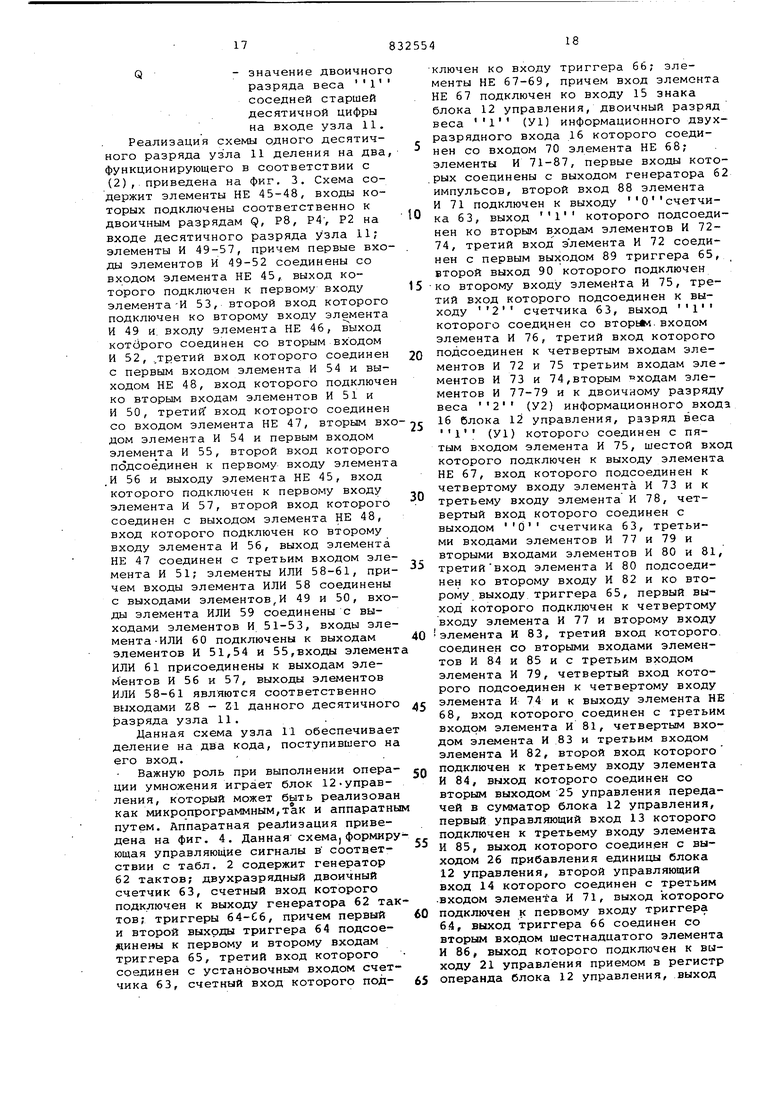

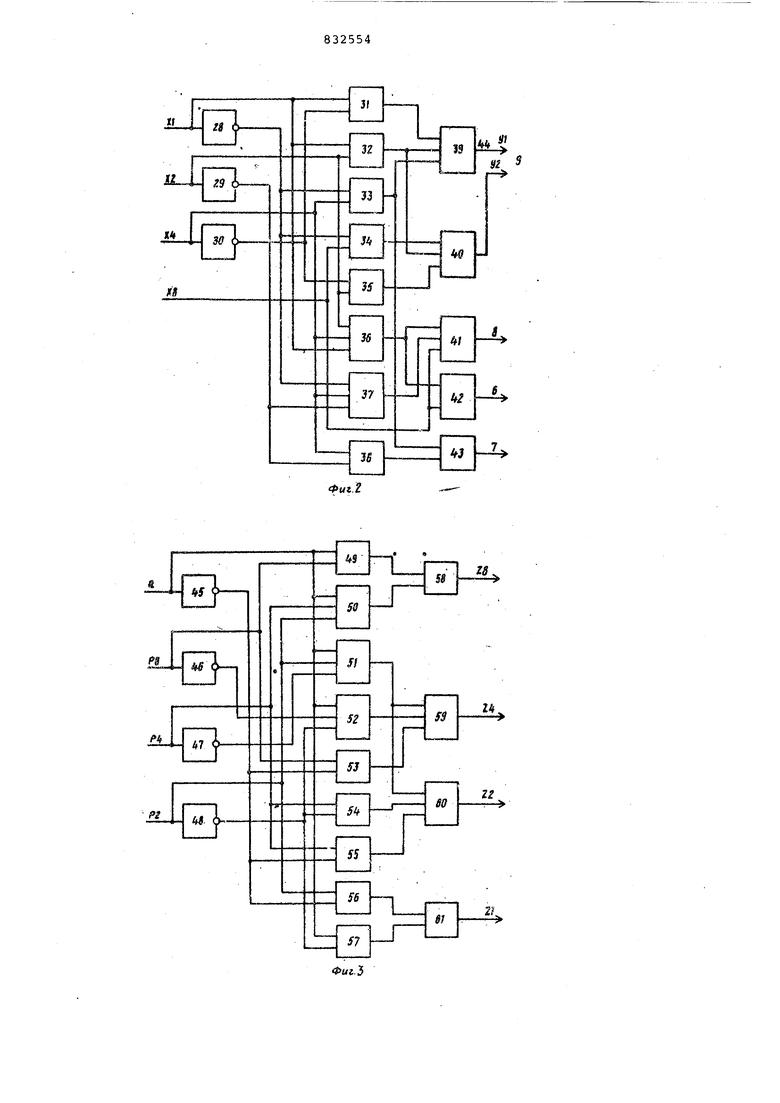

Продолжение табл. 2 абл. 1 на основании выраже8 + Х4Х2Х1; 4Х1 + Х4Х2; «Xl: -) 8 + Х4Х2Х1 + Х4Х2Х1; 4Х1 + Х2Х1 + Х4Х1; 2Х1 + Х8Х1 + Х4Х2: - сигналы, появляющиеся на выходах 6-8 узла 5 преобразования цифры соответственно;У2 выходы двоичных разрядов с весами Ч и 2 двухразрядного информационного выхода узла 5 соответственно;,Х2,Х1 двоичные разряды с весами 8, 11411 I I т I I ч , , 1 четырехразрядного информационного входа узла 5. 1 деления на два представй комбинационную схему, код которой равен частному от а два десятичного числа, его на ее вход. Каждый десязряд узла 11 функционирует ствии с выражениями P8 + QP4P2; P8 + QP4P2 + QP8P2; 4Р2 + QP4 + QP4P2 P2 + QP2, ,Z2,Z1 значения двоичных разрядов с весами 8 , 4, 2 и десятичных цифр на . выходе узла 11; ,Р2 - значения двоичных разрядов с весами 8 , 4, 2 соответствующих десятичных цифр на входе узла 11; Q- значение двоичног разряда веса i соседней старшей десятичной цифры на входе узла 11. Реализация схемы одного десятичного разряда узла 11 деления на два функционирующего в соответствии с (2), приведена на фиг, 3. Схема содержит элементы НЕ 45-48, входы которых подключены соответственно к двоичным разрядам Q, Р8, Р4, Р2 на входе десятичного разряда узла 11; элементы И 49-57, причем первые вхо ды элементов И 49-52 соединены со входом элемента НЕ 45, выход которого подключен к первому входу элемента-И 53, второй вход которого подключен ко второму входу элемента И 49 и. входу элемента НЕ 46, выход котброго соединен со вторым входом И 52, дретий вход которого соединен с первым входом элемента И 54 и выходом НЕ 48, вход которого подключе ко вторым входам элементов И 51 и И 50, третий вход которого соединен со входом элемента НЕ 47, вторым вх дом элемента И 54 и первым входом элемента И 55, второй вход которого подсоединен к первому входу элемент .И 56 и выходу элемента НЕ 45, вход которого подключен к первому входу элемента И 57, второй вход которого соединен с выходом элемента НЕ 48, вход которого подключен ко второму входу элемента И 56, выход элемента НЕ 47 соединен с третьим входом эле мента И 51; элементы ИЛИ 58-61, при чем входы элемента ИЛИ 58 соединены с выходами элементов,И 49 и 50, вхо ды элемента ИЛИ 59 соединены с выходами элементов И 51-53, входы эле мента -ИЛИ 60 подключены к выходам элементов И 51,54 и 55,входы элемен ИЛИ 61 присоединены к выходам элементов И 56 и 57, выходы элементов ИЛИ 58-61 являются соответственно выходами Z8 - Z1 данного десятичного разряда узла 11. Данная схема узла 11 обеспечивает деление на два кода, поступившего на его вход. Важную роль при выполнении операции умножения играет блок 12.управления, который может быть реализован как микропрограммным,так и аппаратны путем. Аппаратная реализация приведена на фиг. 4. Данная схема,формиру ющая управляющие сигналы в соответствии с табл. 2 содержит генератор 62 тактов; двухраэрядный двоичный счетчик 63, счетный вход которого подключен к выходу генератора 62 так тов; триггеры 64-С6, причем первый и второй выходы триггера 64 подсоединены к первому и второму входам триггера 65, третий вход которого соединен с установочным входом счетчика 63, счетный вход которого подключен ко входу триггера 66; элементы НЕ 67-69, причем вход элемента НЕ 67 подключен ко входу 15 знака блока 12 управления, двоичный разряд веса (У1) информационного двухразрядного входа 16 которого соединен со входом 70 элемента НЕ 68; элементы И 71-87, первые входы которых соединены с выходом генератора 62 импульсов, второй вход 88 элемента И 71 подключен к выходу Осчетчика 63, выход которого подсоединен ко вторым входс1М элементов И 7274, третий вход элемента И 72 соединен с первым выходом 89 триггера 65, второй выход 90 которого подключен ко второму входу элемента И 75, третий вход которого подсоединен к выходу 2 счетчика 63, выход которого соединен со вторьи входом элемента И 76, третий вход которого подсоединен к четвертым входам элементов И 72 и 75 третьим входам элементов И 73 и 74,вторым ходам элементов И 77-79 и к двоичному разряду веса 2 (У2) информационного входа 16 блока 12 управления, разряд веса (У1) которого соединен с пятым входом элемента И 75, шестой вход которого подключен к выходу элемента НЕ 67, вход которого подсоединен к четвертому входу элемента И 73 и к третьему входу элемента И 78, четвертый вход которого соединен с счетчика 63, третьивыходомми входами элементов И 77 и 79 и вторыми входами элементов И 80 и 81, третийвход элемента И 80 подсоединен ко второму входу И 82 и ко второму выходу триггера 65, первый выход которого подключен к четвертому входу элемента И 77 и второму входу элемента И 83, третий вход которого, соединен со вторыми входами элементов И 84 и 85 и с третьим входом элемента И 79, четвертый вход которого подсоединен к четвертому входу элемента И 74 и к выходу элемента НЕ 68, вход которого соединен с третьим входом элемента И 81, четвертым входом элемента И 83 и третьим входом элемента И 82, второй вход которого подключен к третьему входу элемента И 84, выход которого соединен со вторым выходом 25 управления передачей в сумматор блока 12 управления, первый управляющий вход 13 которого подключен к третьему входу элемента И 85, выход которого соединен с выходом 26 прибавления единицы блока 12 управления, второй управляющий вход 14 которого соединен с третьим ХОДОМ элемента И 71, выход которого одключен к первому входу триггера 4, выход триггера 66 соединен со торым входом шестнадцатого элемента 86, выход которого подключен к выоду 21 управления приемом в регистр перанда блока 12 управления, выход 22управления, сдвигом которого подсоединен к выходу элемента И 87, вто рому входу триггера 64 и к установоч ному входу счетчика 63, выход которого соединен с четвертым входом элемента И 82, пятый вход которого подключен ко входу элемента НЕ 67 элементы ИЛИ 91-96, гричем входы элемента ИЛИ 91 соединены с выходами элементов И 72-75, а выход - с выходом 20 разрешения приема в регистр 2 блока 12 управления, выход 23управления операцией которого сое динен с выходом элементов ИЛИ 92 выходы которого соединены с выходами элементов НЕ 67 и И 79, входы эле мента ИЛИ 93 подключены к выходам элементов И 75-79, входы элемента ИЛИ 94 соединены с выходами элементо И 75-82, а выход - через элемент НЕ 69 со вторым входом элемента И 87, входы элемента ИЛИ 95 соединены с .выходами элементов И 75, 76, 82 и 83, а выход - с первым выходом 24 управления передачей в сумматор блока 12 управления, выход 18 сложения которого соединен с выходом элемента ИЛИ 96, входы которого подключены к выходам элементов ИЛИ 95 и И 84; элемент 97 задержки, подсоединенный между выходом элемента ИЛИ 93 и выхо дом 19 преобразования блока 12 управ ления. Блок 12 управления (фиг, 4) форми рует управляющие сигналы в соответствии с табл, 2 и работает сл едующим образом. первому такту первого цикла соответствует нулевое состоЯние триггеров 64-66 и счетчика 63 (сигнал на выходе О счетчика). Поэтому по сигналу генератора 62 тактов открывается элемент И 86, формируя сигн.ал на выходе 21 блока 12 управления. Кроме того, если на входе 14 блока 12 управления , то срабатывает элемент И 71 установив триггер 64 в (это указывает :, что текущая преобразованная цифра множителя представлена с недостатком 5 ) . Если на входе 13 блока 12 управл то открывается элемент И 85, обеспечив формирование сигнала на выходе 26 блока 12 управления. Одновременно, если на входе 15 знак блока 12 управления OV (+) или если на информационном входе 16 код 40 (что открывает элемент. И 79) то срабатывает элемент ИЛИ 92, выра батывая сигнал (+) на выходе 23 бло 12 управления. Отсутствие сигнала н выходе 23 рассматривается как (-). Кроме того, если разряд с весом Ч информационного входа 16 в единице, то открывсцотся элементы и 83 и ИЛИ 95 и 96, обеспечивая формирование сигналов на выходах 17 и 24 блока 1 управления, В это время, если Ьвоич (У2).инфор ный разряд с весом ационного входа 16 в единице, сраатывают элементы И 77 и ИЛИ 93, беспечив формирование сигнала, коорый, задержавшись на элементе 97 адержки, появляется на выходе 19 лока 12 управления. Кроме того, рабатывают элементы ИЛИ 94 и НЕ 69, акрывая элемент И 87 и запрещая повление на выходе 22. В это .же время сигнал генератора 62 тактов поступает на счетный вход счетчика 63, обеспечив к началу второго такта установку счетчика в единицу (потенциал на выходе счетчика) . Кроме того, сигнал генератора 62 тактов устанавливает в единицу триггер 66, запирая элемент И 86. Второй такт сложения (вычитания) выполняется тогда, когда двоичный информационного разряд веса входа 16 установлен в единицу. В этом случае открываются элементыИ 72, 76 и ИЛИ 91, 93, 94, 95 и 96, обеспечив формирование сигналов на выходах 17, 20, 24 и задержанного сигнала на выходе 19 и запретив появление сигнала на выходе 22. Сигнал на выходе 23 блока 12 управления формируется аналогично описанному выше для первого такта. Сигнал на выходе 22 по сигналу генератора 62.тактов появится в том случае, если не откроется ни один из элементов И 75-81. в этом случае сработает элемент НЕ 69, обеспечив отпирание элемента И 87, установку в нуль счетчика 63, запись в триггер 65 содержимого триггера 64 и сброс последнего в нуль. Таким образом, в триггер 65 запоминается тот факт, что предыдущая преобразованная десятичная цифра множителя была представлена с недостатком 5. На этом выполнение первого цикла заканчивается. Второй и все последующие циклы выполняются в зависимости от состояния триггера 65. Если триггер 65 установлен в О, то данный цикл выполняется аналогично первому (за исключением сигнала на выходе 21 блока управления, который формируется только на.первом цикле). Если триггер 65 установлен на , то сигналы блока управления формируются следующим образом. Сигналы на выходах 23 и 26 вырабатываются аналогично описанному выше для первого цикла. Первому такту цикла соответствует нулевое состояние счетчика 63. Поэтому, если на входе 14 , срабатывает элемент И 71, обеспечив по сигналу генератЬра 62 тактов, установку триггера 64 в 1 Одновременно срабатывают элементы И 84 и ИЛИ 96, формируя сигналы на выходах 17 и 25 блока 12 управления. Кроме того, если на входе 16 блока управления код 10 или если на входе 16 код 11 и на входе 15 знака,- (-), то открываются элементы И 78 или 79, отпирая элемент ИЛИ 93 и формируя с задержкой (Сигнал на выходе 19. По сигналу ген ратора 62 тактов к началу второго такта счетчик .63 установится в Если на входе 16 блока 12 управления код 10, 11 или если на входе 16 код 01. и на входе 1 знака {+), то на втором такте по си налу генератора 62 тактов срабатыва ют элементы И 75 или 82 и ИЛИ 94 96, формируя сигналы на выходах 17, 24 и запретив сигнал на выходе 22. Кроме того, если на входе 16 код 1( или если на входе 16 код 1 и на входе 15 (-), то отпираются эл менты .73 или И 74, и элемент И 76 обеспечив срабатывание элементов ИЛИ 91, 93 и 94, формирующих сигнал на выходах 2,0 и 19 и запрещающих си нал на выходе 22. Если же на входе 16 код 11 и на входе 15 ( + ), то отпираются элемент И 76 и ИЛИ 93, вырабатывая сигнал на выходе 19. В этом случае.сигнал на выходе 20 не появляется . По этому же сигналу ге нератора 62 тактов счетчик 63 устанавливается в Третий такт сложения (вычитания) выполняется, если на входе 16 блока 12 управления код 11 а на вход 15 (+). В этом случае по сигналу ге ратора 62 тактов открываются элемен ты И 75 и ИЛИ 91, 93, 94 и 95, обеспечивая формирование сигналов на выходах 17, 19, 20, 24 и Запрети сигнал на выходе 22. Сигнал сдвига по сигналу генератора 62 тактов на выходе 22появляется в том случае, когда несрабатывает ни один из элементов И 75-81. В этом случае открывается элемент НЕ 69, обеспечив прохождение сигнал генератора 62 тактов через- элемент И 87. Сигнал на выходе 22 перезаписывает содержимое триггера 64 в триг гер 65 и сбрасывает счетчик 63 и Триггер 64 в Появление сигнала на выходе 22 говорит об окончании текущего цикла. Данное устройство обеспечивает обработку десятичной цифры множителя за среднее время , оп{5еделяемое формулойVCo,T()+0,4Tt, :-,,,Y4t время выполнения десятичного сложения; время формирования очередного кратного; 0,3 - вероятность появления цифр 4 5 и 6 , требующих на следующем цикле прибавления 1/2 - кратного множимого., В известном устройстве среднее время обработки десятичной цифры множителя определяется выражением: . Сравнение выражений (3) и (4) показывает, что в устройстве достигается повышение быстродействия. Формула изобретения 1. Множительное устройство, содержащее десятичный сумматор, регистр удвоенного операнда, регистр операнда, информационный выход которого подключен к информационно «5у входу младших десятичных разрядов регистра удвоенного операнда, регистр множителя и блок управления, выход сложения которого соединен с управляющим входом сложения десятичного сумматора, выход преобразования блока управления подключен к первому управляющему входу регистра удвоенного операнда, второй управляющий вход которого соединен с выходом управления приемом в регистр удвоенного операнда блока управления, выход управления приемом в регистр операнда которого подсоединен ко входу приема в регистр .операнда, выход управления сдвигом блока управления подключен ко входам сдвига десятичного сумматора, и регистра множителя, отличающееся тем, что, с целью увеличения быстродействия, в устройство дополнительно введены коммутатор, узел деления на два и узел преобразования цифры, причем выход управления операцией блока управления подключен ко входу управления операцией десятичного сумматора, информационный вход которого соединен с выходом коммутатора, первый информационный вход которого подсоединен к выходу регистра удвоеннрго операнда и ко входу узла деления на два, выход которого подключен к информационному входу регистра рперанда, выход которого соединен со вторым информационным входом коммутатора, первый и второй управляющие входа которого подключены соответственно к первому и второму выходам управления передачей в умматор блока управления, первый и второй управляющие входы которого соединены соответственно с первым и вторым управляющими выходами узла преобразования цифры, выход знака которого подключен ко входу знака блока управления, информационный вход которого с весами i и 2 подсоединен к двухразрядному с весами 1 и 2 информационному выходу узла преобразования цифры четырехразрядный информационный вход которого с весами 1 и 2, 4 и 8 соединен с выходом младшего десятичного разряда регистра множителя, управляющий вход которого подключен к выходу прибавления единицы блока управления, 2. Устройство поп. 1, ОТЛИ fi а ю щ е е с я тем, что узел преобразования цифры содержит восемь элементов И, пятьэлементов ИЛИ и три элемента НЕ, причем вход первого эле мента НЕ подключен к двоичному разря информационного вхо ду с весом да узла преобразования цифры и к пер вым входам первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, третий . вход которого соединен с выходом третьего элемента И, первый вход которого подключен к выходу, первого элемента НЕ и к первому входу четвертогоэлемента Ир выход которого подсоединен к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, второй вход которого соединен с двоичным разрядом с весом 2 информационного входа узла преобразова ния цифры, со входом второго элемента НЕ и первым входом пятого элемента И, выход которого подключен к третьему входу второго элемента ИЛИ, а второй вход - ко второму входу пер вого элемента И и выходу третьего элемента НЕ, вход которого соединен с двоичным разрядом с весом 4 ин формационного входа узла преобразова ния цифры,вторым входом третьего эле мента И. и первым входом шестого элемента И,второй вход которого подключен ко входу второго элемента НК,выйод которого подсоединен к первым вх дам седьмого и восьмого элементов И, вторые входу которых соединены с пер вым- входом шестого элемента И,третий вход которого подключен ко входу пер вого элемента НЕ, выход которого под соединен к третьему входу седьмого элемента И, выход которого подключен к первому входу третьего элемента ИЛ второй вход которого соединен с выходом шестого элемента И и первым вх дом четвертого элемента ИЛИ, второй вход которого подключен к третьему входу третьего элемента ИЛИ, второму входу четвертого элемента И и к двоичному разряду с весом 8 информа ционного входа узла преобразования цифры, выход восьмого элемента И которого соединен с первым входом пятого элемента ИЛИ, второй вход которого подсоединен ктретьему входу первого элемента ИЛИ, выход которого соединен с двоичным разрядом с весом 1 информационного выхода узла преобразования цифры, двоичный разряд с весом 2 которого подключен к выходу второго элемента ИЛИ, выходы третьего, четвертого и пятого элементов ИЛИ соединены соответственно с выходом знака и первым и вторым управляющими выходами узла преобразования цифры. 3, Устройство по п. 1, отличающееся тем, что блок управления содержит генератор тактов, двухразрядный двоичный счетчик, три триггера, три элемента НЕ, семнадцать элементов И,, шесть элементов ИЛИ и элемент задержки, причем первый и второй выходы первого триггера подсоединены к первому и второму входам второго триггера, третий вход которого соединен с установочным входом двоичного счетчика, счетный вход которого подключен ко входу третьего триггера, выходу генератора тактов и первым входом первого - семнадцатого элементов И, второй вход первого элемента И подключен к выходу О двоичного счетчика, выход 1 первого разряда подсоединен ко вторым входам второго-четвертого элементов И, третий вход второго элемента И соединен спервым выходом второго триггера, второй выход которого подключен ко второму входу пятого элемента И, третий вход которого подсоединен к выходу О двоичного счетчика , выход которого соединен со вторым входом шестого элемента И, третий Вход которого подсоединен к четвертым входам второго и пятого элементов И, третьим входам третьего и четвертого элементов И,вторым входам седьмого-девятого элементов И и к двоичному разряду веса 2 информационного входа блока управления, разряд веса i которого соединен с пятым входом пятого элемента И, шестой вход которого подключен к выходу первого элемента НЕ, вход которого подсоединен ко входу знака блока управления, четвертому входу третьего элемента И и к третьему входу восьмого элемента И, четвертый вход которого соединен с выходом О двоичного счетчика, третьими входами седьмого и девятого элементов И и вторыми входами десятого и одиннадцатого элементов И, третий вход десятого элемента И подсоединен ко второму входу двенадцатого элемента И и ко второму выходу второго триггера, первый выход которого подключен к четвертому входу седьмого элемента И и второму входу тринадцатого элемента И, третий вход которого соединен со вторыми входами четырнадцатого и пятнадцатого элементов И и с третьим входом девятого элемента И, четвертый вход которого подсоединен к четвертому входу четвертого элемента И и к выходу второго элемента НЕ, вход которого соединен с двоичным разрядом веса 1 информационного двухразрядного входа блока управления, с третьим входом одиннадцатого элемента И, четвертым входом тринадцатого элемента И и третьим входом двенадцатого элемента И, второй вход которого под,ключен к третьему входу четырнадцатого элемента И, выход которого соединен со вторым выходом управления передачей в сумматор блока управления , первый управляющий вход которого подключен к третьему входу пятнадцатого элемента И, выход которого соединен с выходом прибавления единицы блока управления, второй управляющий вход которого соединен с третьим входом первого элемента И, выход которо О подключен к первому входу первого триггера, выход третьего триггера соединен со вторым входом шестнадцатого элемента И, выход которого подключен, к выходу управления приемом в регистр операнда блока управления, выход управления сдвигом которого подсоединен к выходу семнадцатого элемента И,.второму входу первого триггера и уст новочному входу двоичного счетчика, выход которого соединен с четвертым входом двенадцатого элемента И, пятый вход которого подключен к выходу первого элемента НЕ, первый-четвертый входы первого элемента ИЛИ соединены соответственно с выходом второго-пятого элементов И, а выход - с выходом разрешения приема в регистр удвоенного операнда блока управления, выход управления операцией которого соединен с выходом второго элемента ИЛИ, пер- вый и второй входы которого соединены соответственно с выходами первого элемента НЕ и девятого элемента И, первый - пятый входы третьего элемента ИЛИ подключены к выходам пятого- девятого элементов И, первый восьмой входы четвертого элемента ИЛИ

0 соединены соответственно с выходами пятого-двенадцатого элементов И, а выход - через третий элемент НЕ со вторым входом семнадцатого элемента И, первый - четвертый входы пятого эле5мента ИЛИ соединены соответственно с выходами пятого, шестого, двенадцатого и тринадцатого элементов И, а выход - с первым выходом управления передачей в сумматор блока управле0ния, выход сложения которого соединен с выходом шестого элемента ИЛИ, первый и второй входы которого подключены к выходам пятого элемента ИЛИ и четырнадцатого элемента И, выход третьего элемента ИЛИ через элемент .

5 задержки соединен с выходом преобразования блока управления.

Источники информации, принятые во внимание при экспертизе .

0

кл. G 06 F 7/39, 1976 (прототип).

S

tt

гг

1-

1L.

1

Х4

ал А

(JV J

а

М

Фиг.5

У1Л

y/f/i

ISJ

Фиг.

Авторы

Даты

1981-05-23—Публикация

1979-07-27—Подача