СП

i150

Изобретение относится к цифровой вычислительной технике и может быть использовано в высокопроизводительны цифровых вычислительных процессорах, прежде всего специализированных, предназначенных для цифровой обработки сигналов.

Целью изобретения является сокращение аппаратурных затрат.

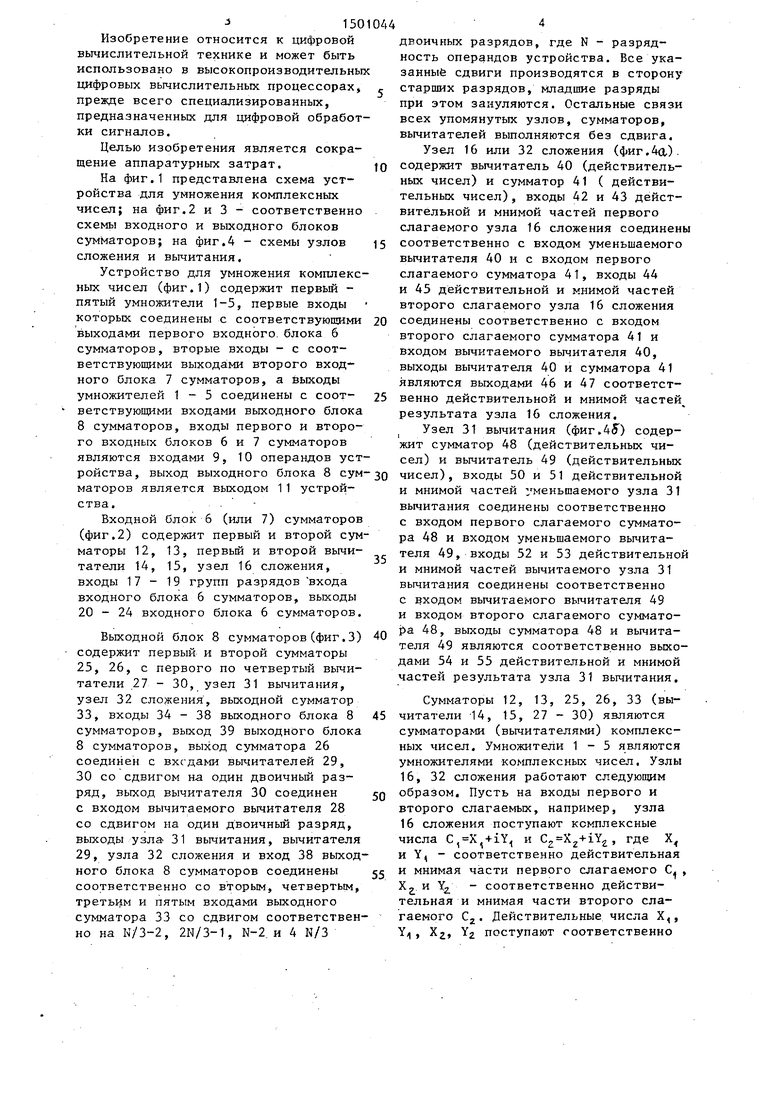

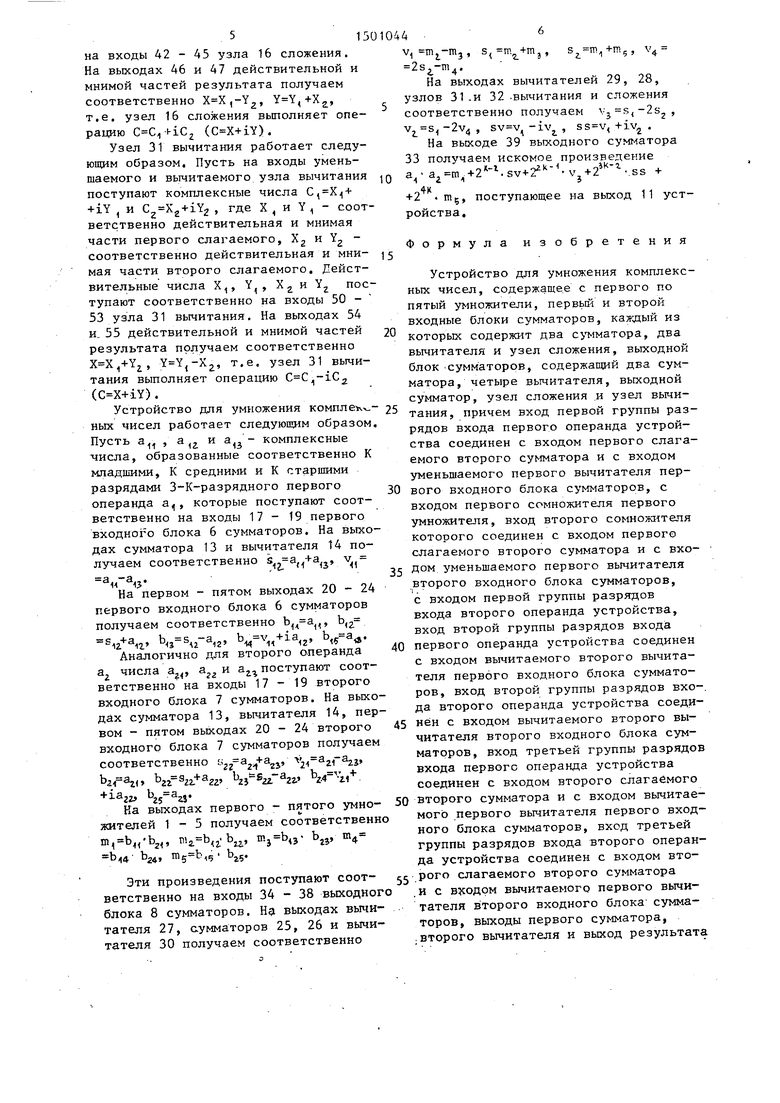

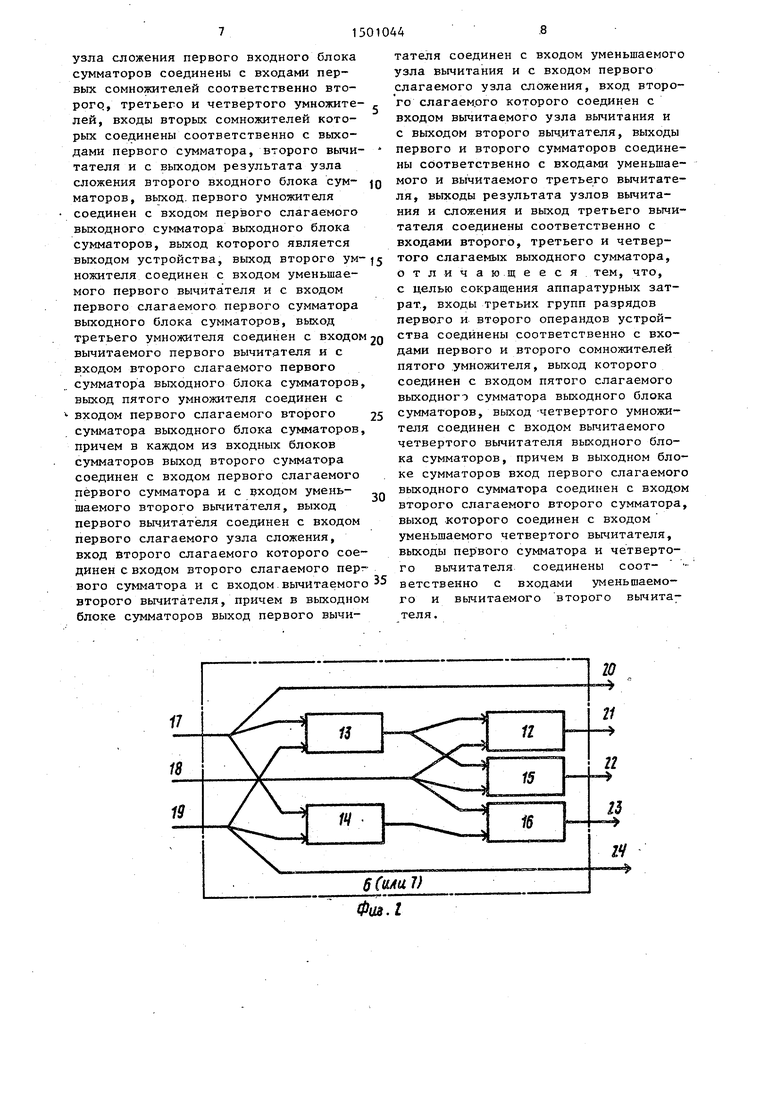

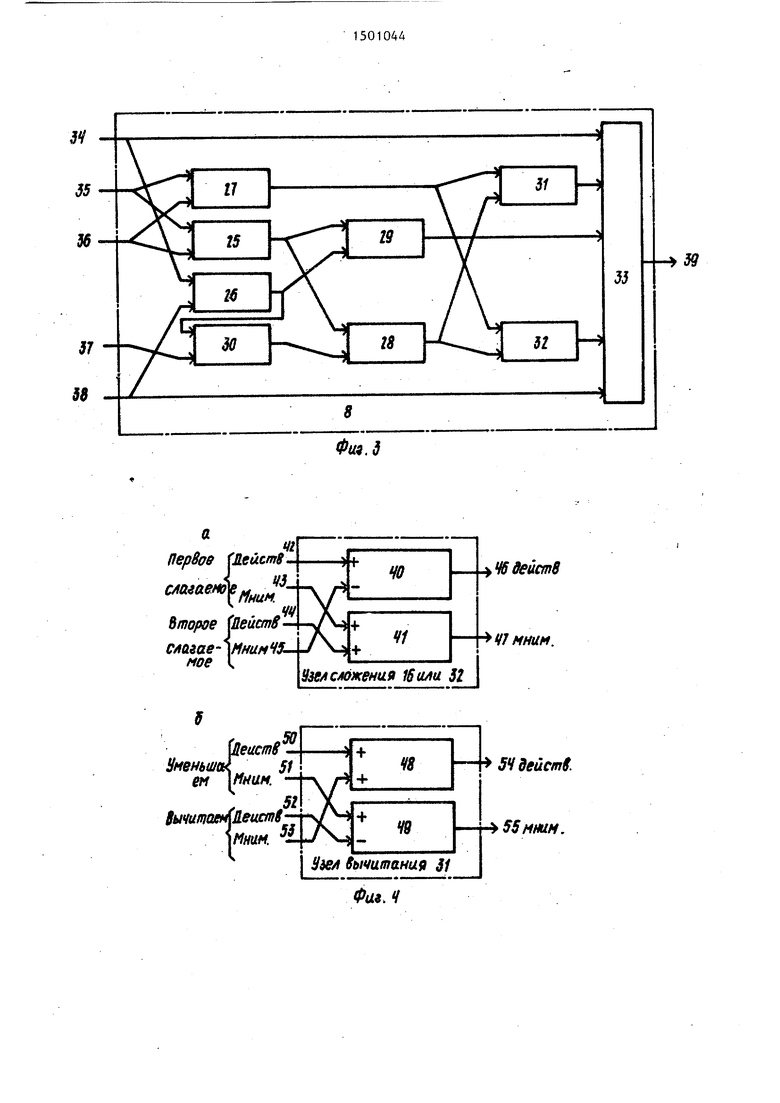

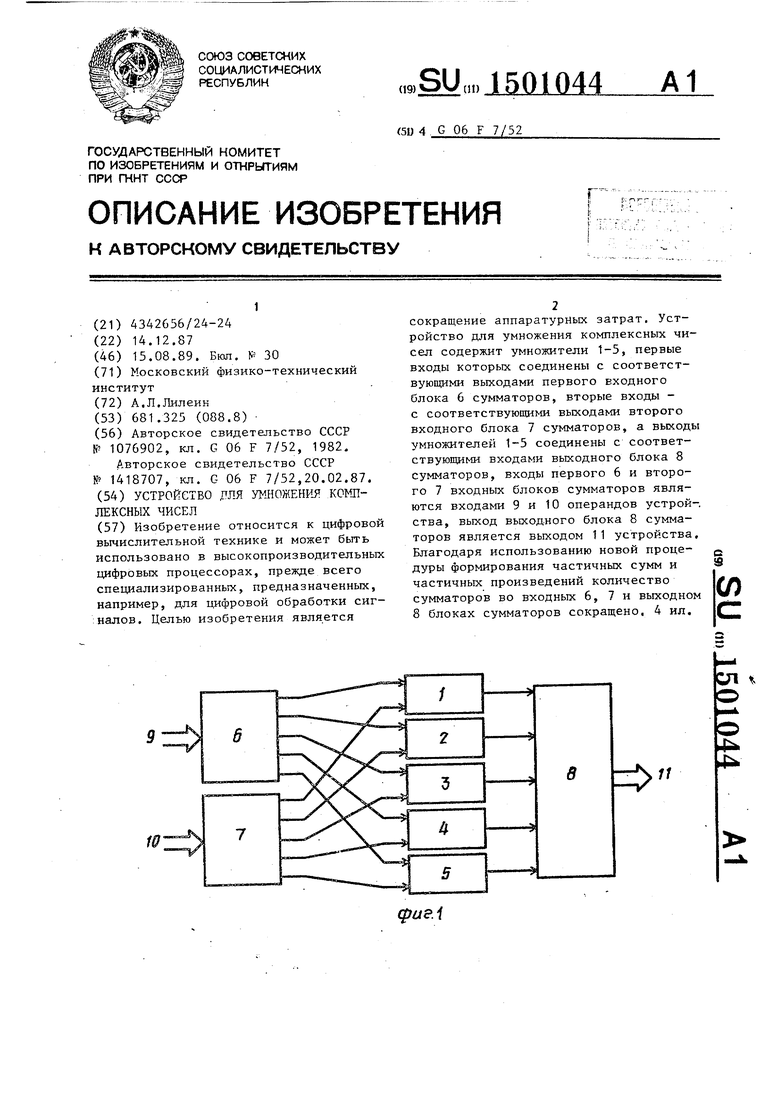

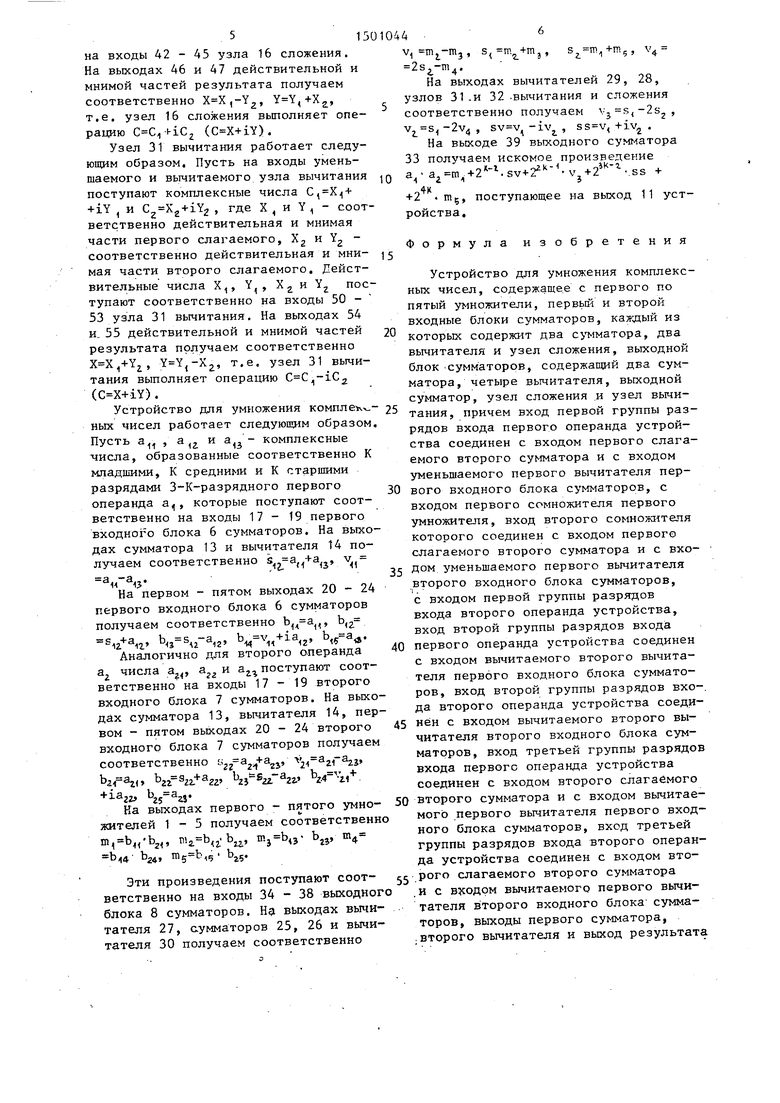

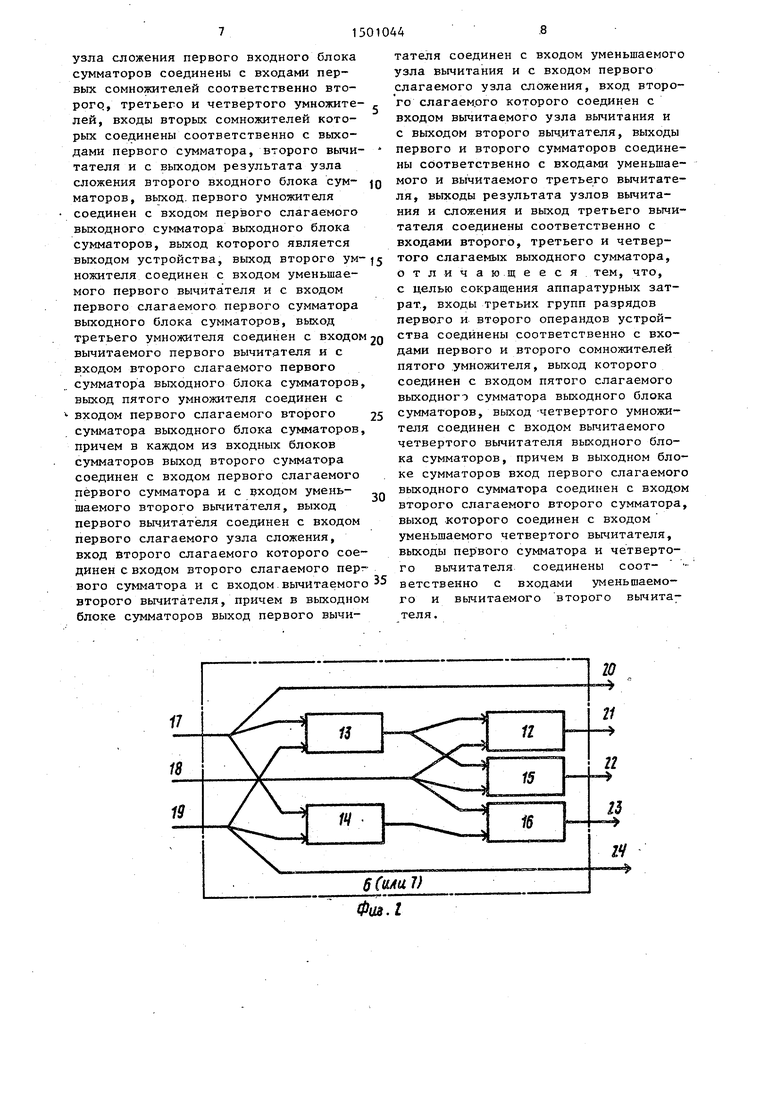

На фиг.1 представлена схема устройства для умножения комплексных чисел; на фиг.2 и 3 - соответственно схемы входного и выходного блоков сумматоров; на фиг.4 - схемы узлов сложения и вычитания.

Устройство для умножения комплексных чисел (фиг.1) содержит первьй - пятый умножители 1-5, первые входы которых соединены с соответствующими выходами первого входного, блока б сумматоров, вторые входы - с соответствующими выхода ми второго входного блока 7 сумматоров, а выходы умножителей 1 - 5 соединены с соот- ветствующими входами выходного блока 8 сумматоров, входы первого и второго входных блоков 6 и 7 сумматоров являются входами 9, 10 операндов устройства, выход выходного блока 8 сум маторов является выходом 11 устройства..

Входной блок 6 (или 7) сумматоров (фиг.2) содержит первый и второй сумматоры 12, 13, первый и второй вычи- татели 14, 15, узел 16 сложения, входы 17-19 групп разрядов входа входного блока 6 сумматоров, выходы 20 - 24 входного блока 6 сумматоров.

Выходной блок 8 сумматоров(фиг.3) содержит первый и второй сумматоры 25, 26, с первого по четвертый вычи- татели 27 - 30, узел 31 вычитания, узел 32 сложения, выходной сумматор 33, входы 34 - 38 выходного блока 8 сумматоров, выход 39 выходного блока 8 сумматоров, выход сумматора 26 соединен с вхсдами вьиитателей 29, 30 со сдвигом на один двоичный разряд, выход вычитателя 30 соединен с входом вычитаемого вычитателя 28 со сдвигом на один двоичный разряд, выходы узла 31 вычитания, вьмитателя 29, узла 32 сложения и вход 38 выходного блока 8 сумматоров соединены соответственно со вторым, четвертым, третьим и пятым входами выходного сумматора 33 со сдвигом соответственно на N/3-2, 2N/3-1, N-2. и 4 К/3

Q

5

0 5 о

0 5 0 5

5

двоичных разрядов, где N - разрядность операндов устройства. Все указанные сдвиги производятся в сторону старших разрядов, младшие разряды при этом зануляются. Остальные связи всех упомянутых узлов, сумматоров, вычитателей выполняются без сдвига.

Узел 16 или 32 сложения (фиг.4а). содержит вьгчитатель 40 (действительных чисел) и сумматор 41 ( действительных чисел), входы 42 и 43 действительной и мнимой частей первого слагаемого узла 16 сложения соединены соответственно с входом уменьшаемого вычитателя 40 и с входом первого слагаемого сумматора 41, входы 44 и 45 действительной и мнимой частей второго слагаемого узла 16 сложения соединены соответственно с входом второго слагаемого сумматора 41 и входом вычитаемого вычитателя 40, выходы вычитателя 40 и сумматора 41 являются выходами 46 и 47 соответственно действительной и мнимой частей, результата узла 16 сложения.

Узел 31 вычитания (фиг.45) содержит сумматор 48 (действительных чисел) и вычитатель 49 (действительных чисел), входы 50 и 51 действительной и мнимой частей уменьшаемого узла 31 вычитания соединены соответственно с входом первого слагаемого сумматора 48 и входом уменьшаемого вычитателя 49, входы 52 и 53 действительной и мнимой частей вычитаемого узла 31 вычитания соединены соответственно с входом вычитаемого вычитателя 49 и входом второго слагаемого сумматора 48, выходы сумматора 48 и вычитателя 49 являются соответственно выходами 54 и 55 действительной и мнимой частей результата узла 31 вьгаитания.

Сумматоры 12, 13, 25, 26, 33 (вы- читатели -14, 15, 27 - 30) являются сумматорами (вычитателями) комплексных чисел. Умножители 1 - 5 являются умножителями комплексных чисел. Узлы 16, 32 сложения работают следующим образом. Пусть на входы первого и второго слагаемых, например, узла 16 сложения поступают комплексные числа C,X, + iY и ., где Х и Y, - соответственно действительная и мнимая части первого слагаемого С , Х и Yj, - соответственно действительная и мнимая части второго слагаемого Cj. Действительные числа X,, YI, Х, Y поступают соответственно

51501044

на входы 42 - 45 узла 16 сложения. На выходах 46 и 47 действительной и мнимой частей результата получаем

v

соответственно ,-Y2, ,+X2,

Ha выходах вычитателей 29, 28, узлов 31.и 32 .вычитания и сложения

,-2s,

20

„4К, .

+Z . т, поступающее на выход 11 устройства.

Формула изобретения

Устройство для умножения комплексных чисел, содержаще.е с первого по пятый умножители, первьгй и второй входные блоки сумматоров, каждый из которых содержит два с т-матора, два вычитателя и узел сложения, выходной блок -сумматоров, содержащий два сумматора, четыре вычитателя, выходной

I г ч 2. с т.е. узел 16 сложения выполняет one- соответственно получаем

рацию ().v , , s

Узел 31 вычитания работает следу- На выходе 39 выходного сумматора ющим образом. Пусть на входы умень- 33 получаем искомое произведение шаемого и вычитаемого узла вычитания Q а . .ss + поступают комплексные числа С, + iY и . + ГД X 1 и Y , - соответственно действительная и мнимая части первого слагаемого, Xj и Y- - соответственно действительная и мни- 15 мая части второго слагаемого. Действительные числа X,, Y, Xg и Yj поступают соответственно на входы 50 - 53 узла 31 вычитания. На выходах 54 и. 55 действительной и мнимой частей результата получаем соответственно ,+Y2, , т.е. узел 31 вычитания выполняет операцию ,-iC2

().

,. „сумматор, узел сложения и узел вычиУстроиство для умножения компле.-

,„,,„„ ол„„-,. .. тания, причем вход первой группы разрядов входа первого операнда устройства соединен с входом первого слагаемого второго сумматора и с входом уменьшаемого первого вычитателя пер- 30 вого входного блока сумматоров, с входом первого сомножителя первого умножителя, вход второго сомножителя которого соединен с входом первого слагаемого второго сумматора и с вхо- 35 дом уменьшаемого первого вычитателя второго входного блока сумматоров, с входом первой группы разрядов входа второго операнда устройства, вход второй группы разрядов входа 40 первого операнда устройства соединен с входом вычитаемого второго вычитателя первого входного блока суммато-

входного блока 7 сумматоров. На выхо- РОВ. вход второй группы разрядов вхо-. дах сумматора 13, вычитателя 14, пер- Да второго операнда устройства соеди- вом - пятом выходах 20-24 второго 45 ней с входом вычитаемого второго вычитателя второго входного блока сумматоров, вход третьей группы разрядов входа первого операнда устройства соединен с входом второго слагаемого

vTa в ьгход ах первого - пятого умно- 50 второго сумматора и с входом вычитае- жителей 1 - 5 получаем соответственно первого вычитателя первого вход- , b2,, mj.b,j.b, ,3- b,, m ч

ных чисел работает следующим образом. Пусть а (2. 13 комплексные числа, образованные соответственно К младшими, К средними и К старшими разрядами 3-К-разрядного первого операнда а, которые поступают соответственно на входы 17 - 19 первого входного блока 6 сумматоров. На выходах сумматора 13 и вычитателя 14 получаем соответственно %(

На первом - пятом выходах 20-24 первого входного блока 6 сумматоров получаем соответственно , Ь,2

Аналогично для второго операнда а числа а, а и а поступают соответственно на входы 17 - 19 второго

входного блока 7 сумматоров получаем соответственно ,, ,

+1агг, а..

-Ьци Ь, ,5 bj5.

ного блока сумматоров, вход третьей группы разрядов входа второго операнда устройства соединен с входом вто- Эти произведения поступают соот- 5 Р° слагаемого второго сумматора ветственно на входы 34 - 38 выходного .и с вводом вычитаемого первого вычи- блока 8 сумматоров. На выходах вычи- тателя второго входного блока сумма- тателя 27, сумматоров 25, 26 и вычи- торов, выходы первого сумматора, тателя 30 получаем соответственно ,второго вычитателя и выход результата

v, , s,, 2s.,-m.

, v

Ha выходах вычитателей 29, 28, узлов 31.и 32 .вычитания и сложения

соответственно получаем

,-2s,

„4К, .

+Z . т, поступающее на выход 11 устройства.

Формула изобретения

Устройство для умножения комплексных чисел, содержаще.е с первого по пятый умножители, первьгй и второй входные блоки сумматоров, каждый из которых содержит два с т-матора, два вычитателя и узел сложения, выходной блок -сумматоров, содержащий два сумматора, четыре вычитателя, выходной

На выходе 39 выходного сумматора 33 получаем искомое произведение а . .ss +

узла сложения первого входного блока сумматоров соединены с входами первых сомножителей соответственно второго, третьего и четвертого умножителей, входы вторых сомножителей которых соединены соответственно с выходами первого сумматора, второго вычи- тателя и с выходом результата узла сложения второго входного блока сум- маторов, вьрсод. первого умножителя соединен с входом первого слагаемого выходного сумматора выходного блока сумматоров, выход которого является выходом устройства, выход второго умножителя соединен с входом уменьшаемого первого вычитателя и с входом первого слагаемого первого сумматора выходного блока сумматоров, выход третьего умножителя соединен с входом вычитаемого первого вычитателя и с входом второго слагаемого первого сумматора выходного блока сумматоров, выход пятого умножителя соединен с входом первого слагаемого второго сумматора выходного блока сумматоров, причем в каждом из входных блоков сумматоров выход второго сумматора соединен с входом первого слагаемого первого сумматора и с входом уменьшаемого второго вычитателя, выход первого вычитателя соединен с входом первого слагаемого узла сложения, вход Второго слагаемого которого соединен с входом второго слагаемого первого сумматора и с входом.вычитаемого второго вычитателя, причем в выходном блоке сумматоров выход первого вычи

Q J5 n 5 5

0

тателя соединен с входом уменьшаемого узла вычитания и с входом первого слагаемого узла сложения, вход второго слагаемого которого соединен с входом вычитаемого узла вычитания и с выходом второго вьгч.итателя, выходы первого и второго сумматоров соединены соответственно с входами уменьшаемого и вычитаемого третьего вычитателя, выходы результата узлов вычитания и сложения и выход третьего вычитателя соединены соответственно с входами второго, третьего и четвертого слагаемых выходного сумматора, отличающееся тем, что, с целью сокращения аппаратурных затрат., входы третьих групп разрядов первого и второго операндов устройства соединены соответственно с входами первого и второго сомножителей пятого умножителя, выход которого соединен с входом пятого слагаемого выходного сумматора выходного блока сумматоров, выход -четвертого умножителя соединен с входом вычитаемого четвертого вычитателя вьсходного блока сумматоров, причем в выходном блоке сумматоров вход первого слагаемого выходного сумматора соединен с входом второго слагаемого второго сумматора, выход которого соединен с входом уменьшаемого четвертого вычитателя, выходы первого сумматора и четвертого вычитателя соединены соот- ветственно с входами уменьшаемого и вьнитаемого второго вычитателя .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел | 1987 |

|

SU1418707A1 |

| Устройство для умножения двоичных комплексных чисел | 1987 |

|

SU1424015A1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1982 |

|

SU1019458A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Последовательный сумматор-вычитатель | 1986 |

|

SU1363191A1 |

| Устройство для реализации быстрого преобразования фурье | 1977 |

|

SU734707A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в высокопроизводительных цифровых процессорах, прежде всего специализированных, предназначенных, например, для цифровой обработки сигналов. Целью изобретения является сокращение аппаратурных затрат. Устройство для умножения комплексных чисел содержит умножители 1-5, первые входы которых соединены с соответствующими выходами первого входного блока 6 сумматоров, вторые входы - с соответствующими выходами второго входного блока 7 сумматоров, а выходы умножителей 1-5 соединены с соответствующими входами выходного блока 8 сумматоров, входы первого 6 и второго 7 входных блоков сумматоров являются входами 9 и 10 операндов устройства, выход выходного блока 8 сумматоров является выходом 11 устройства. Благодаря использованию новой процедуры формирования частичных сумм и частичных произведений количество сумматоров во входных 6, 7 и выходном 8 блоках сумматоров сокращено. 4 ил.

Фиа.1

Фи9.д

Пер8об (Лейст9 VJ.

41

Ч

Мним.

Второе (йеиапб

c/iuiae MHUfifi мое

.

чfS

49

де/1 ьи/итания J/ Фи9. 4

46 действ

41 мним.

fS

и

54 действ.

49

S5MHUH,

| Матричное устройство для умножения | 1982 |

|

SU1076902A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения комплексных чисел | 1987 |

|

SU1418707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-14—Подача