Изобретение отпоентся к иычие.|;1те,;1ык)й технике и может бьи ь Hcno.aixiOBalio в lui- |)a.i;ie, ii)iibix В1 1чиелите. 1ьи1-,1л системах :: оП- шим управ.аением и с: ociioisinjii амитвю, состоящей из иеско.1ьких neaans-iciiMo алре- cycMBix б.локов.

Цель изобретеш .и ii()Bbiiiic:ii:e ,ic : |5()- действия,

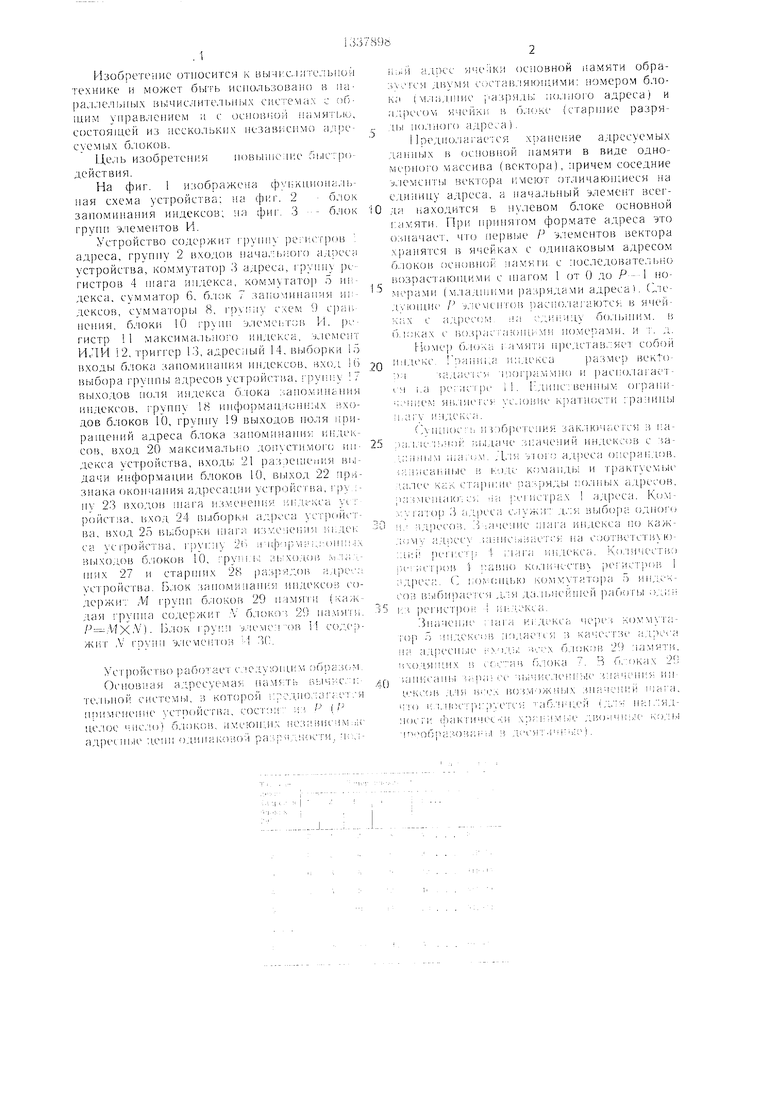

На фиг. 1 изображена ф;/|;кциоии.-|ь- ная схема устройства: на (|)i;r. 2 - блок запоминания индексов; на фи1 . 3 - блок элементов И.

Устройство соде)жит -pyiiii - ре Л1стр(Н адреса, группу 2 входов пача. п.нгя О ад1.)еса устройства, коммутатор 3 адреса, rpviniy регистров 4 niara индекса, коммутатч р о HI:- декса, сумматор 6. б;к;к 7 зат1иминан:-1я дексов, сумматор1Л 8, I fixini v схем 9 срав нения, блоки 10 rpyiui bi;ieMChi ;;ii И, |):, - гистр И максимального нндекса, члемент ИЛИ 12,триг1 ер 13, адресный 14. 15В1борки io входы б,ока за1юмина1п;я индексов, вход ( выбора rpynniii адресов устройс-тва, rpviiiiy 7 ввгкодов индекса б,тока :-;анОлЛ1НсПни (Ч)в, rpvnriy Н инфО()мап,И(.;нн:,1х i .xo- дов 10, групну 19 выходов ноля нри- ращений адреса блока заноминаник щ.деи,- , вход 20 максима,, 1В|10 дон ст11мого индекса устройства, входв; 21 pa:i.)eHieiii;s выдачи информации блоков К), 22 признака окончания адрес адни устройства, гр :- HV 23 входов Hiai a изменении ин;|.екса у г )ойства, г;ход 24 1 В1борки х стройст- 1за, вход 25 )ки Hiai ; ; нзуенения HI,дек

Са ЧЛ р(.)ЙСТВа, I pyiniV i/ii и иЬмрм; :,:-ОНН:-1л выходов б,1ОКОВ 10, rpyiUi,; ()Л,OB ;- :Н1ИХ 27 и старпшх 28 |)азрядо|% нл.рсс:: устройства. x:ioK .чапоминанг;; Н1 дексо 5 со- дсржн ; М I pyiHi б, 1оков 29 намя 1 {ка/к- дая группа е(;держиг .V блокоз 29 . /- .. V). 13лок племен ч)в И со;:.е;)- жит Л rovHH э, 1еме Г1()з -1 3(7

Ус 1 ройсгво рабо ает с..ед ;-оп1,нм о(п)аз(;-г Основная адресуемая -.ыч-ч . л; те,1вной системы, з кг)Т()|)ой 1:: сл,но, :;и-; ст. я П)нменен1 е устройст ;, сост;;; ич нелое 4iic, M) бл;Нх()в, нмеюнлх .л;- адресные ;,енн ).динакоз()л ра-;;;зд -;(1сти, н;. адосс яче-iKH основной iiawHTH обра- з..м-си ДВУМЯ соста15. як;ицими: номером бло- а |м.-|ал1нис ; а:) но,1ного адреса) и ад1нч-ом ячейки в б,:|(. Ке (старшие разря- - л.в 11о, адре.-а ).

i редно, агае ;ся xuaneiiHe адресуемых . laHHBix в оеновн()й намяти в виде одно- MejHioro маеси а (вектора), причем соседние з:1емснты вектора имеют отличающиеся на ед)пгицу адрееа, а нача;1ьный элеме|гг веег0 . |,а. 11аходится в |улевом блоке основной гал яти. При пргп1ятом формате адреса это означает, что первые Р 7,1 ем ен то в вектора хр;а11Я 1 ся 15 ячейках с одииаковым адресом 6.:iOK(jB ос1кни1()й чамяги с носледовате. илк) возрастакощимн с шагом 1 от О до Я- 1 но- McinsMn (м, разрядами адреса). (7ie- ;|.чо11.1ие / э. кчкнтов пасно, 1агак)тсн в ячейках с ад|)ес1;м iia здинчду бо,1Ь1ПИМ. i блзках с возрас гак) номерами, и ;. д. Hi)Mep 6,i(jxa i амитн представ, :ие еобой

0 индекс. I JHiiHua н;цекса })азме;) векТо- :)чia.iac i c:.i чзограммно и paci:o, iai acTгя i.a pe iicipc il. дннс; lieHHBiM огранн- ;.мji;e ; яв,1Я1Мч я ус.юане кратнос ч :рачины пз гу | чдекса.

CVIUHOC:) н обретения :jaK, iio4;ie|-ся з :а5 за, i. К 1ьч;)1 ввгдаче значений индекс1;в с ча- ;;;м;П,м Hjaii..A. Д, 1Я :;ior;; oneria н.чов. ;Ил;;сан1П)1С к ко.че KOMaiLUii и трактх слЛме ui, U e к;;;-; старите па;-,ряды полных ал,ресов, ;ia iMeniaio : ;. на рсч Hi Tpax 1 адрееа, КОМ- УЗ,л ато) 3 a. ipcca c. iv/tiH : д, :я выбора одного

i- :i. :HT ieco3. -) ;ачение aiaixi индекса но каж- .;;;му а.Ч;К су ;aiiHCbi3ae i ; ; на сзсшкл ств ю- зиЛ рег13. t 3iara iH.i.eKca. Ко.-;нчестг(о ;3 ч;сгров 1 ;авно Kij, iH4v-c i4i регистров 1 здреса. С, коммх татора 5 инд.сч- соз вз бнраек я д,-;я да.1ьнсЙ ней раб;)гы од1Л J гч peiTicTpcHi iiH. i3Kca.

5начсн,1е ;iai3 и1Д1Ччса чере-; коммх та- гор 5 зндексо15 нздас 1.я з качестве а.чзсеа i3 a;i H eHijie г.чз.з; -ic;.x б. 29 чамятн, зходяншх в блока . В б,-оках 29

Q ;аннсаны араич- зычн(.-..е чначс1п:я нн и. ксов .T. Ui Bi c.s BO4M 3 i Hbix .Н1ачс п:и 1ча;з1, ciii 1- ;. ni;c j H ;r, стся ..ей (д, : -- на1. :яд- HiiciH (Ьак ГИЧ1.-С-Hi х:) двоичн;-:е ко. )61 ачоiia(:;1 ; . зчзг;-РЧ- зЧ .

При подаче сигнала разрешения на входы разрешения считывания всех блоков 29 памяти, на выходах младших разрядов блоков 29 с номерами с 0-го по Р-1-й будут параллельно считаны Р значений индексов, взятые по modP. Одновременно с этим, на выходах остальных разрядов блоков 29 памяти будут параллельно считаны Р приращений адресов ячеек основной адресуемой памяти. Указанная ситуация соответствует крайнему случаю, когда блок 7 содержит единственную группу блоков 29 памяти (.1, ). Следует учитывать, что количество сумматоров 8 и схем 9 сравнения равно количеству одновременно считываемых индексов, т. е. количеству блоков 29 памяти, на которые подается сигнал разрешения считывания в одном такте.

Структура предлагаемого устройства позволяет варьировать значения М и ,V, оставляя .V постоянным. При увеличении М и соответствующем уменьшении .V количество блоков 8 и 9 уменьшается, однако количество тактов (импульсов разрешения считывания), которое требуется для индексирования всех блоков основной памяти, растет, т. е. быстродействие устройства уменьшается, достигая в пределе (при , ) быстродействия последовательного формирователя адресов.

Пример параллельного формирования адресов устройством.

Предположим, что , , шаг индекса 3, регистр адреса - четырехразрядный, начальное значение адреса основной памяти 0010, верхняя граница индекса 39. В первом такте (по первому сигналу разрешения считывания) на четырех индексных группах 17 выходов блока 7 формируются следуюнхие 4-х битовые коды. ГруппыГIIIII IV

0000 ООП ОНО 1001

Одновременно, на четырех адресных группах 49 19 выходов блока 7 формируются коды приращений адреса

0000

0000

0000

0000

Поскольку граница индекса еще не до- ст-игнута, на выходах схем 9 сравнения сохраняются значения потенциалов, разрешающих по входам 21 прохождение сформированных кодов с информационных групп 18 входов на информационные группы 26 выходов блоков 10. В результате на группах выхо- дов 27 и 28 устройства формируются следующие адреса основной памяти

00100000 00100011 00100110 00101001

Обращение происходит к элементам вектора данных, расположенным во вторых ячейках нулевого, третьего, luecToro и девятого блоков основной памяти.

Во втором такте на индексных группах выходов 17 блока 7 формируются следующие коды (по mod 16)

100 111

0010 0101,

а на соответствующих адресных группах 19 выходов - коды

0000 0000 0001 0001

Поскольку граница не достигнута, то на группах выходов 27 и 28 устройства формируются адреса

15

00101100 00101

00110010 00110101.

что соответствует элементам вектора данных, расположенных во вторых ячейках двенадцатого и пятнадцатого блоков основной памяти и в третьих ячейках второго и пятого блоков основной памяти.

В третьем такте параллельно формируются следующие адреса

00111000 00111011 00111110 01000001,

25

а в четвертом 01000100 010001

01001010 01001101

9

0

5

5 0

5

В четвертом такте во втором блоке 9 происходит совпадение с содержимым регистра границы. Разрешающий потенциал на входах групп элементов И 30 блоков 10, начиная с 3-й группы, снимается. Выдаются только адреса на 1-й и 2-й группах выходов 27 и 28 устройства, т. е. 01000100 и 01000111.

Одновременно сигнал сравнения через элемент ИЛИ 12 устанавливает триггер 13 и на выходе 22 устройства появляется сигнал индикации окончания работы, что приводит к прекращению дальнейщей подачи сигналов выбора групп на входы 16 устройства.

Таким образом, применение предлагаемого устройства позволяет одновременно формировать Л адресов элементов обрабатываемого вектора, что в .-V раз повыщает быстродействие по сравнению с применением последовате,1ьно работающего узла вычисления индексов.

Формула изобретения

1. Устройство для параллельного формирования адресов, содержащее группу регистров адреса, группу регистров шага индекса, коммутатор адреса, коммутатор индекса и сумматор, причем информационный вход Я-го регистра адреса подключен к К -му входу начального адреса устройства (К,Н, где Н - количество начальных адресов), выход /(-го регистра адреса подключен к /(-му информационному входу коммутатора адреса, выход которого подключен к первому входу

первого сумматора, выход регистра тага индекса подключен к ннформаци он- ному входу коммутатора индексов, (R.Q, где Q -- количество шагов изменения индексов), отличающееся тем, что, с целью повышения быстродействия, в него введены два блока групп элементов И, блок запоминания индексов . Л -1 сумматор (где Л - количество параллельно формируемых адресов), группа схем сравнения, элемент ИЛИ, триггер и регистр максимального индекса, причем вход максимально допустимого индекса устройства подключен к информационному входу регистра максимального индекса, вь1ход которого подключен к первым входам схем сравнения грунпы, выходы которых подключены к входам элемента ИЛИ, выход которого подключен к входу установки в « триггера, выход которого подключен к вь1хо- ду признака окончания адресации устройства, управляющий вход и выход коммутатора индекса подключены соответственно к входу выборки Hiara изменен1-п1 индекса устройства и к адресному входу блока запоминания индекса, выход коммутатора адреса подключен к первым входам сумматоров с второго по (Л ---1)-й, /-Й вход разрешения считывапня которого подключен к /-му входу jB y6opa групны адресов устройства (,;М, где/И - количество тактов адресации массива), п-й выход поля индекса блока запоминания индексов и выход п-го сумматора подключены к п-м информацион- н ым входам соответстве 1но нервогд у второго блоков групп элементов И, (.Л ), л-пые информационные выходы которых подключены к п-м выходам соответствешю младших и стар1них разрядов адреса устройст

5

0

5

0

ва, п-к выход схемы сравнения грунпы подключен к п-щ- входу разре1нения выдачи информации первого и втооого блоков групп элементов И, п-й выход ноля индекса и п-н выход ноля приран1епия адреса блока чапоминапия индексов подключены к второму lixoiv л-й схемы сравнения групны, п-й выход ноля приращения блока запоминания ин- и-кч-а подключен к второму входу п-го сумматора, информационный вход ре- шага индекса грунны подключен к входу niara измене1 ия индекса груп- 1П,1 устройства.

2. Устройство по п. I, отличающееся тем, что блок запоминания индексов содержит Л-1 груип блоков памяти, причем адресные входь блоков памяти групп подключены к адресному входу блока, входы разрец ения считывания блоков памяти /-и гругшы юд- ключены к /-му входу разрен енпя считывания блока, выход младпшх разрядов и выход старп1их разрядов п-го блока намяти /-Й группы подключены соответствепно к .f(-My в ыходу поля индекса и п-му выходу ноля приращения адреса групп выходов

б.юка.

3. Устройство по п. 1, отличающееся тем. что блок групп элементов И содержит Л |-)у;1п элемен тов И, причем выходы элементов И п-й группы подключены к п-му информационному выходу блока, т-й инфор- мацион1Ц 1Й вход которого подключен к первым входам элемоггов И гг-й блока, г«-й вход разреп1ения выдачи информации бюка подключен к (т-Г)-м входам элементов И групп с (№-П-й но .V-ную б.юка. г« 1 .. V 1.

Г ае:4 f B

/3

5 фиг2

Редактор И. Касарла Заказ 4132, 47

ВНИИПИ Государствеиного комитета СССР по делам изобретений и открытии

И3035, .Москва. Ж -35. Раушская наб.. д, 4;5 Производствеино-полиграфическое предприятие, г. Ужгород, ул. Проектная. 4

фие.З

Составитель М. Силин

Техред И. ВересКорректор И. .Муска

Тираж 672Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного формирования адресов | 1987 |

|

SU1418711A1 |

| Устройство для параллельного формирования адресов | 1990 |

|

SU1734097A1 |

| Устройство для параллельного формирования адресов | 1988 |

|

SU1575181A2 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения абонентов с ЦВМ | 1985 |

|

SU1278863A1 |

Изобретение относится к вычислительной технике и может быть использовано в параллельных вычислительных систе.мах с общим управлением и с основной памятью. f4/ff фиг.1 состоящей из нескольких независимо адресуемых блоков. Целью изобретения является повышение быстродействия. Устройство св- держит группу регистров 1 адреса, коммутатор 3 адреса, группу регистров 4 шага индекса, коммутатор 5 индекса, сумматор 6, блок 7 запоминания индексов, сумматоры 8, группу схем 9 сравнения, блоки 10 групп элементов И, регистр 1 1 максимального индекса, элемент ИЛИ 12, триггер 13, входы и выходы устройства. Устройство позволяет одновременно формировать ,V адресов элементов обрабатываемого вектора, что в N раз повышает быстродействие по сравнению с применением последовательно работающего узла вычисления индексов. 2 з.п.ф-,1ы. 3 и,-1. со 00 00 со оо

| Формирователь адреса | 1982 |

|

SU1062703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адреса | 1979 |

|

SU826350A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-15—Публикация

1985-01-16—Подача