чального адреса ячейки. С выходов запоминания и сдвига индексов, а 1-й

маторов 12 значения адресов ячеек памяти поступают через блоки элементов И с номерами с 13.1 по 13.N на группу выходов 20 устройства. С выходов блоков элементов К с номерами с 13.(N+1) по 13.2N значения индексов (номер блока) поступают на группу выходов 21 устройства. В результате сформируется N адресов. По второму сигналу выбора группы адресов устройство сформирует еще N адресов. В случае, если при очередном формировании n-й сформированный адрес превысил значение границы массива, которое записано на регистре 4 максимального индекса, n-я схема 9 сравнения переключает через элемент ИЛИ 10 триггер 11, в результате чего на выходе 22 устройства сформируется признак окончания адресации. Кроме того, с n-й схемы 9 сравнения снимется разрешающий сигнал с блоков И 13 с номерами п и (N+n), т.е. произойдет запрещение формирования n-го адреса. Все последующие формируемые адреса также превысят значения границы массива. По сигналу окончания адресации устройство заканчивает работу,

15

20

вход начального номера блока устройства подключен к i-му входу регистра номера блока (где ,,.,,К).

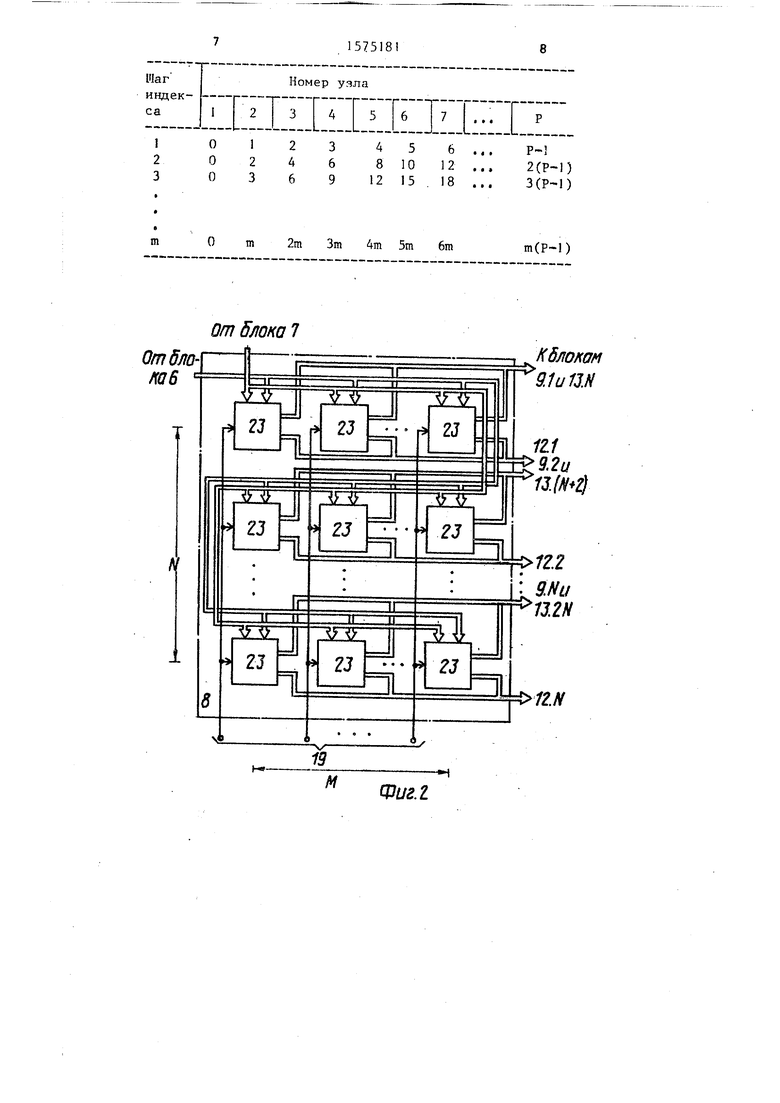

2. Устройство по п. отличающееся тем, что блок запоминания и сдвига индексов содержит М групп узлов запоминания и сдвига индексов (где М - количество тактов адресации массива), причем адресные входы и входы сдвига узлов запоминания и сдвига индексов подключены к адресному входу и входу сдвига блока соответственно, а входы разрешения считывания узлов запоминания и сдвига

25 индексов 1-й группы (где ,.,.,М) подключены к 1-му входу разрешения считывания блока, выходы младших и старших разрядов n-го узла запоминания и сдвига индексов (...,Nl где

30 N - количество параллельно формируемых адресов) 1-й группы подключены к n-му выходу поля индекса и n-му выходу поля приращения адреса групп выходов блока соответственно.

35

3. Устройство по п. 2, отличающееся тем, что узел запоминания и сдвига индексов содержит блок памяти и сумматор, причем адресный вход и вход разрешения считывания блока памяти являются соответственно одноименными входами узла формирования индексов, информационный выход блока памяти соединен с первым входом сумматора, выходы младших и старших разрядов которого являются соответственно одноименными . выходами узла формирования индексов, второй вход сумматора является входом сдвига этого узла.

прекращается подача на вход лов выбора группы адресов.

19 сигнаФормула изобретения

1. Устройство для параллельного формирования адресов по авт.св. № 1337898, отличающееся тем, что, с целью увеличения информационной емкости оперативной памяти за счет ее рационального заполнения, в него введены К регистров номера бло

0

вход начального номера блока устройства подключен к i-му входу регистра номера блока (где ,,.,,К).

2. Устройство по п. отличающееся тем, что блок запоминания и сдвига индексов содержит М групп узлов запоминания и сдвига индексов (где М - количество тактов адресации массива), причем адресные входы и входы сдвига узлов запоминания и сдвига индексов подключены к адресному входу и входу сдвига блока соответственно, а входы разрешения считывания узлов запоминания и сдвига

5 индексов 1-й группы (где ,.,.,М) подключены к 1-му входу разрешения считывания блока, выходы младших и старших разрядов n-го узла запоминания и сдвига индексов (...,Nl где

0 N - количество параллельно формируемых адресов) 1-й группы подключены к n-му выходу поля индекса и n-му выходу поля приращения адреса групп выходов блока соответственно.

3. Устройство по п. 2, отличающееся тем, что узел запоминания и сдвига индексов содержит блок памяти и сумматор, причем адресный вход и вход разрешения считывания блока памяти являются соответственно одноименными входами узла формирования индексов, информационный выход блока памяти соединен с первым входом сумматора, выходы младших и старших разрядов которого являются соответственно одноименными . выходами узла формирования индексов, второй вход сумматора является входом сдвига этого узла.

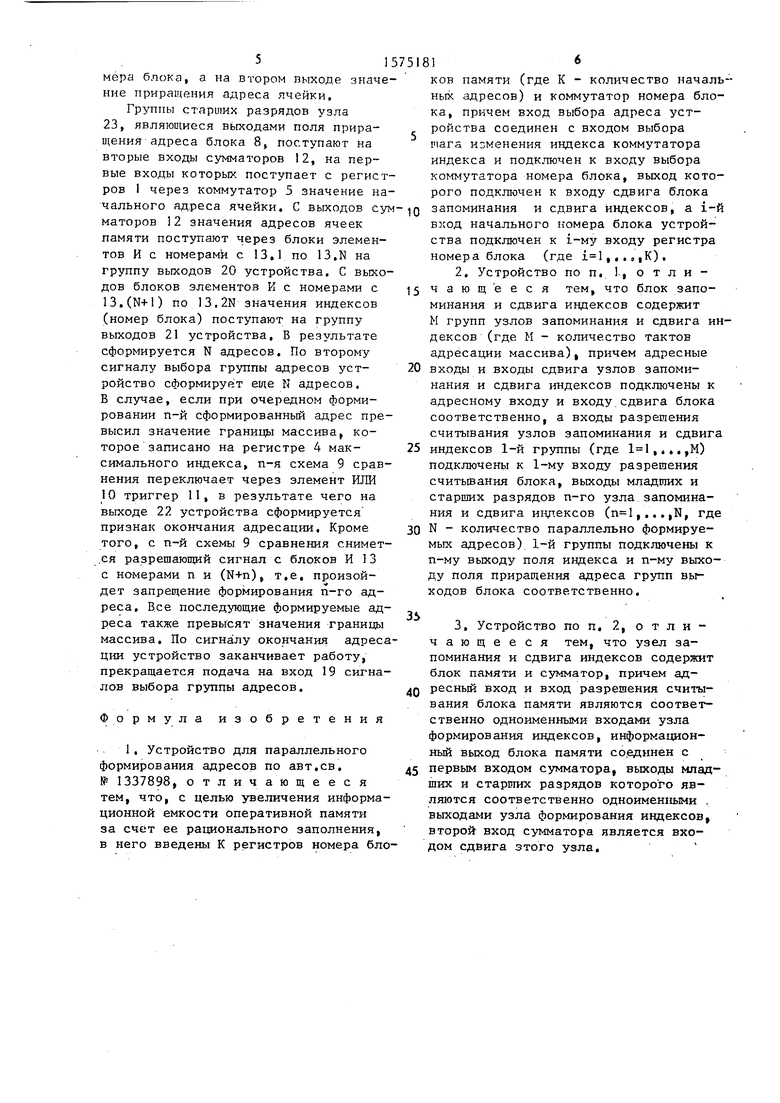

О 1

О 2 О 3

2

4 6

3 6

9

5

10

15

6 12 18

2(РН) 3()

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного формирования адресов | 1990 |

|

SU1734097A1 |

| Устройство для параллельного формирования адресов | 1985 |

|

SU1337898A1 |

| Устройство для параллельного формирования адресов | 1987 |

|

SU1418711A1 |

| Устройство адресации памяти | 1988 |

|

SU1575188A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

Изобретение относится к вычислительной технике и может быть использовано в параллельных вычислительных системах с общим управлением и с основной памятью, состоящей из нескольких независимо адресуемых блоков. Цель изобретения - увеличение информационной емкости оперативной памяти за счет ее рационального заполнения. Устройство содержит группу регистров 1.1-1.K адреса, группу регистров 2.1-2.K номера блока, группу регистров 3.1-3.K шага индекса, регистр 4 максимального индекса, коммутатор 5 адреса, коммутатор 6 номера блока, коммутатор 7 индекса, блок 8 запоминания и сдвига индексов, группу схем 9.1-9.N сравнения, элемент ИЛИ 10, триггер 11, сумматоры 12.1-12.N, блоки 13.1-13.2N групп элементов И, входы и выходы. Устройство позволяет формировать одновременно N адресов обрабатываемого вектора, причем начало вектора может находиться в любом блоке памяти, что позволяет рационально заполнять информационную емкость оперативной памяти. 2 з.п. ф-лы, 3 ил., 1 табл.

m

От 2т Зт 4т 5т 6т

от 5локо 7

Отдло№6

19

М

т()

Кблокам

-и

Фиг. I

Составитель А.Петров Редактор Л.Пчголинская Техред Л.Сердкжова Корректор Т.Палий

Заказ 1785

Тираж 572

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ C(JCP 113035, Москза, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Формирователь адреса | 1982 |

|

SU1062703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для параллельного формирования адресов | 1985 |

|

SU1337898A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1990-06-30—Публикация

1988-09-29—Подача