00 Ч

ю

сд

Изобретение относится к вычислительной технике и может быть использовано для обработки передаваемых данных в системе их сбора,, обработ- ки и передачи, а также в вычислительных сетях.

Цель изобретения - повьшшние производительности о

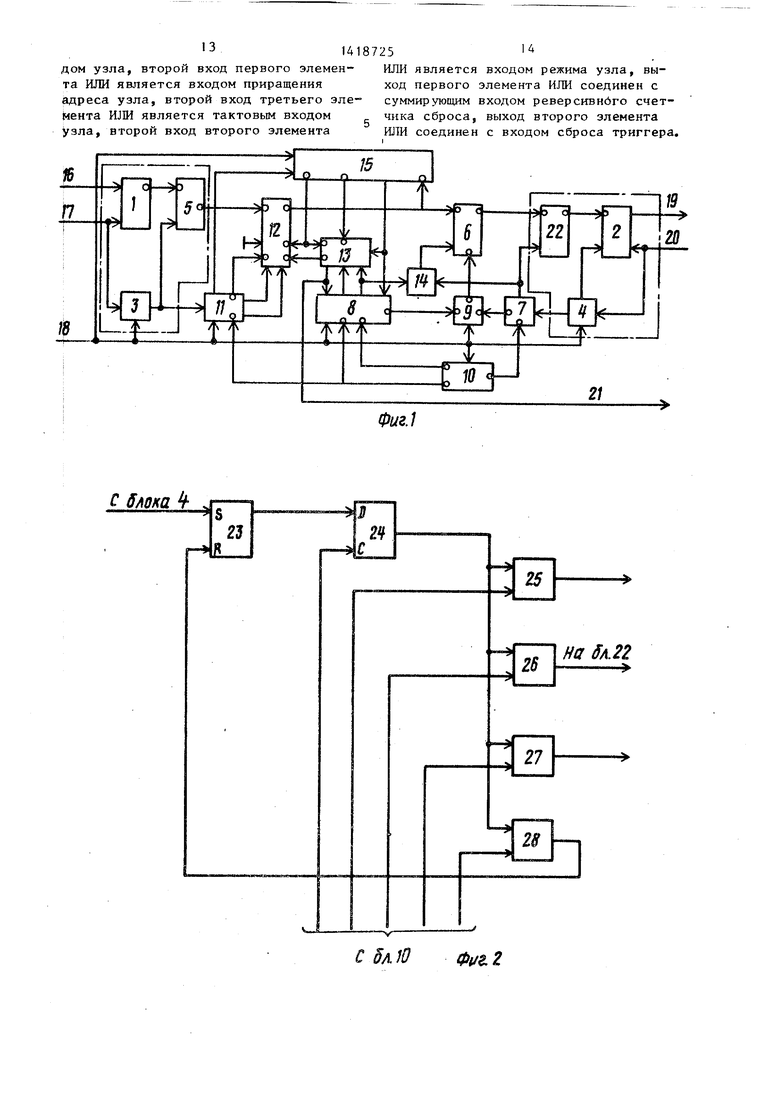

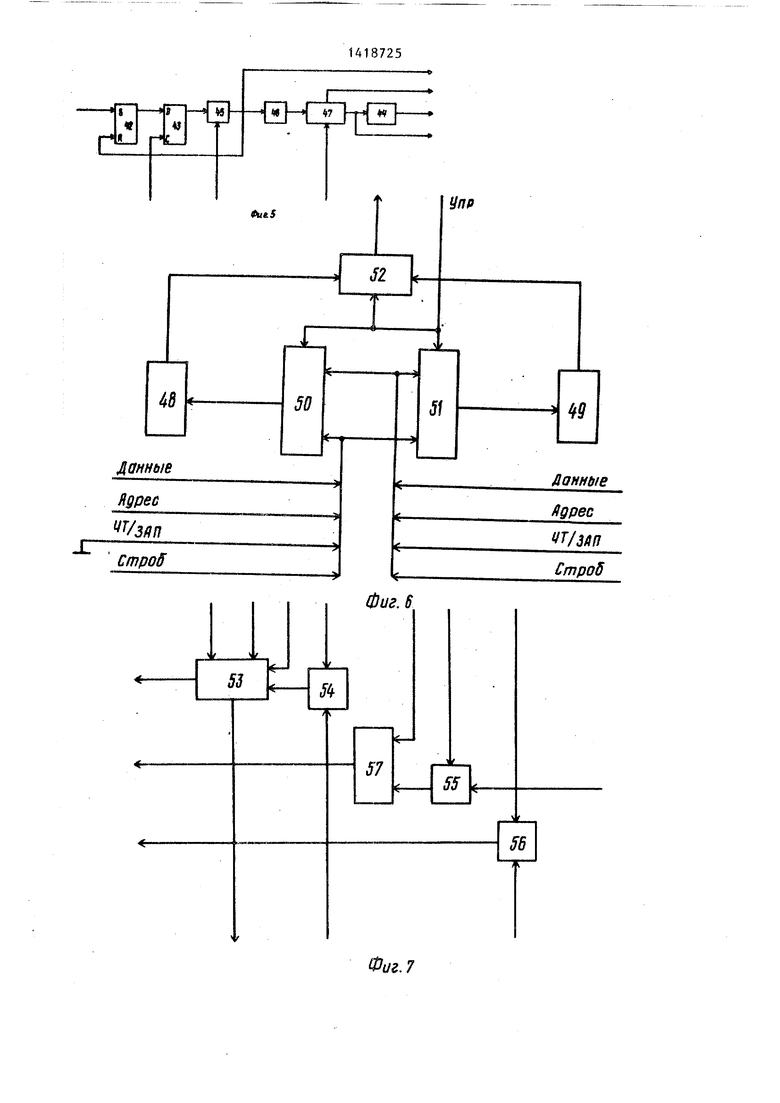

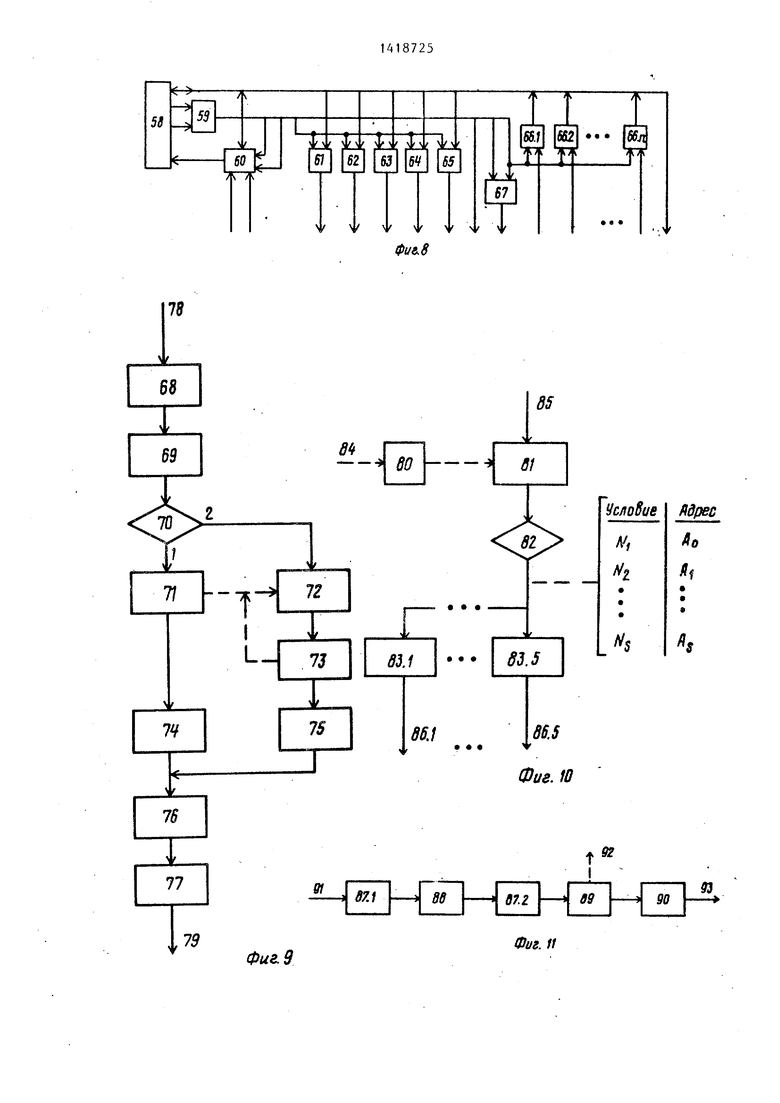

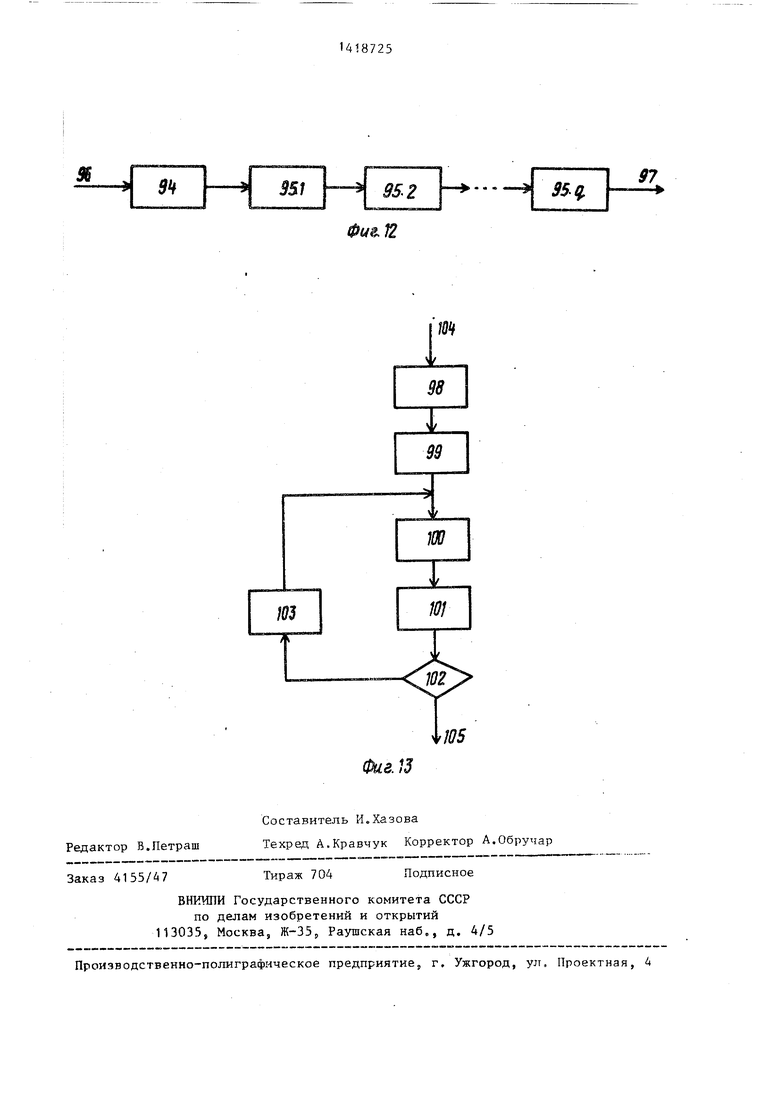

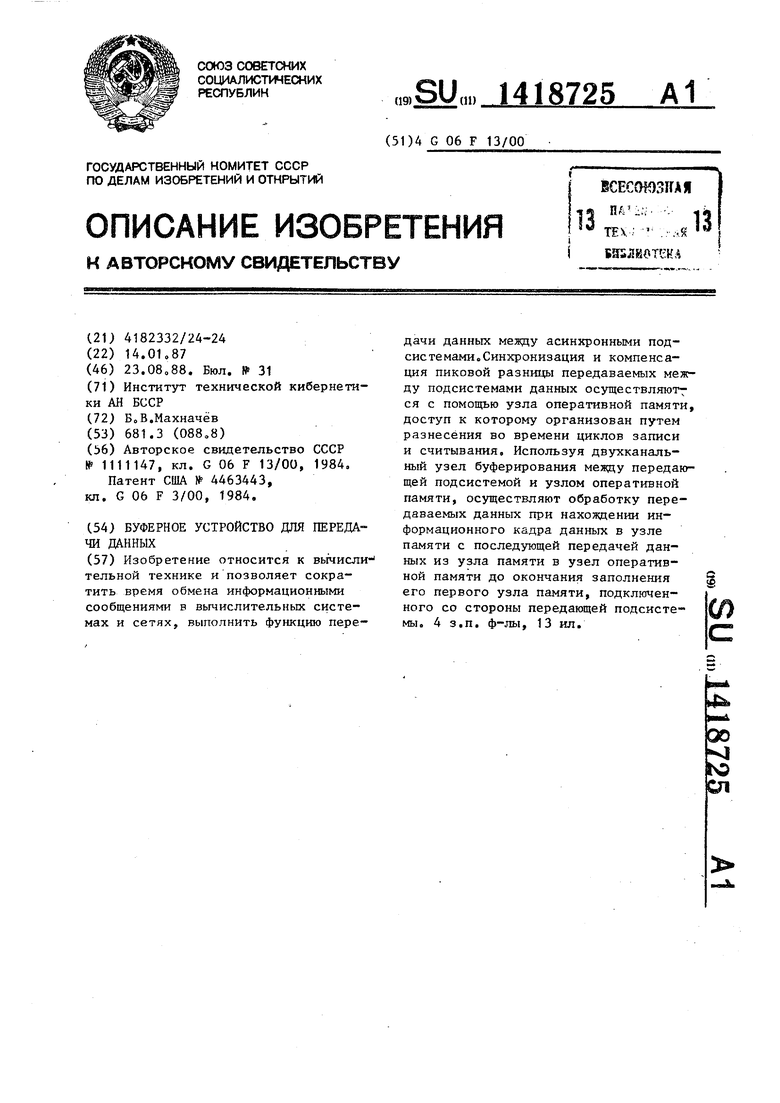

На фиг,1 приведена схема устройст за; на фиг.2 - структурная схема узла управления считыванием; на фиг,3 структурная схема узла управления записью; на - структурная схема узла адресации оперативной памяти; на фиг о 5 - структурная схема узла управления буферированием; на фиг,6 - структурная схема двухканаль ного блока буферирования; на фиг - структурная схема узла доступа к памяти; на - структурная схема узла обработки кадра; на фиг,9 - блок-схема алгоритма работы операционного блока; на - блок- схема алгоритма работы блока определения программ обработки кадров данных; на - блок-схема алгоритма работы блока обработки кадра данных; на фиго12 - блок-схема алгоритма работы группы операторов прие™ ма-вьщачи данных; на - блок- схема, алгоритма работы блоков чтениязаписи массива данныхо

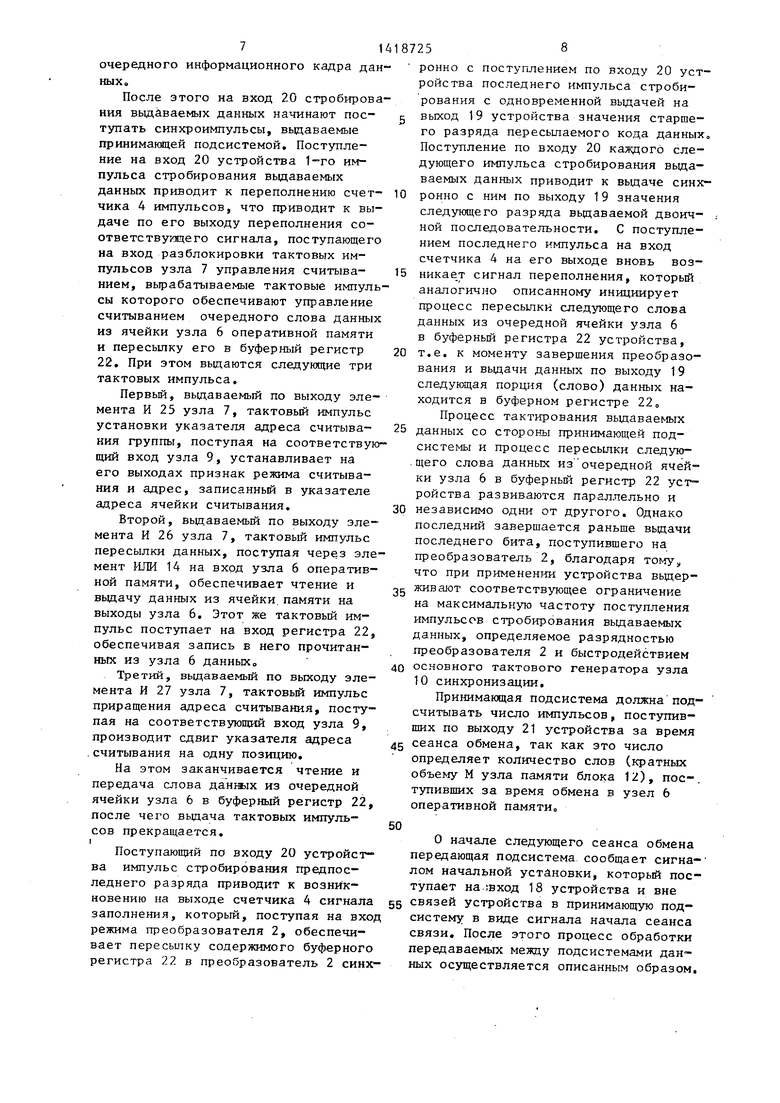

Устройство содержит преобразователь 1 последовательного кода в параллельный, преобразователь 2 параллельного кода в последовательный, счетчик 3 импульсов, счетчик 4 импульсов, буферный регистр 5, узел 6 оперативной памяти, узел 7 управления считьшанием, узел 8 управления записью, узел 9 адресации оперативной памяти, узел 10 синхронизации, узел 11 управления б;5лферированием, двухканальный блок 12 буферирования узел 13 доступа к памяти, элемент ШШ 14, узел 15 обработки кадра, вхо 16 данных, вход 17 стробирования принимаемых данных, вход 18 начальной установки, выход 19 данных, вход 20 стробирования выдаваемых данных и выход 21 сигнала сопровождения данных, буферный регистр 22,

Преобразователь 1, счетчик 3 и буферный регистр 5 образуют блок преобразования последовательного кода в параллельный, а преобразователь 2, счетчик 4 и буферный регистр 22 5

0

5

0

5

0

5

0

5

блок преобразования параллельного кода в последовательньй о

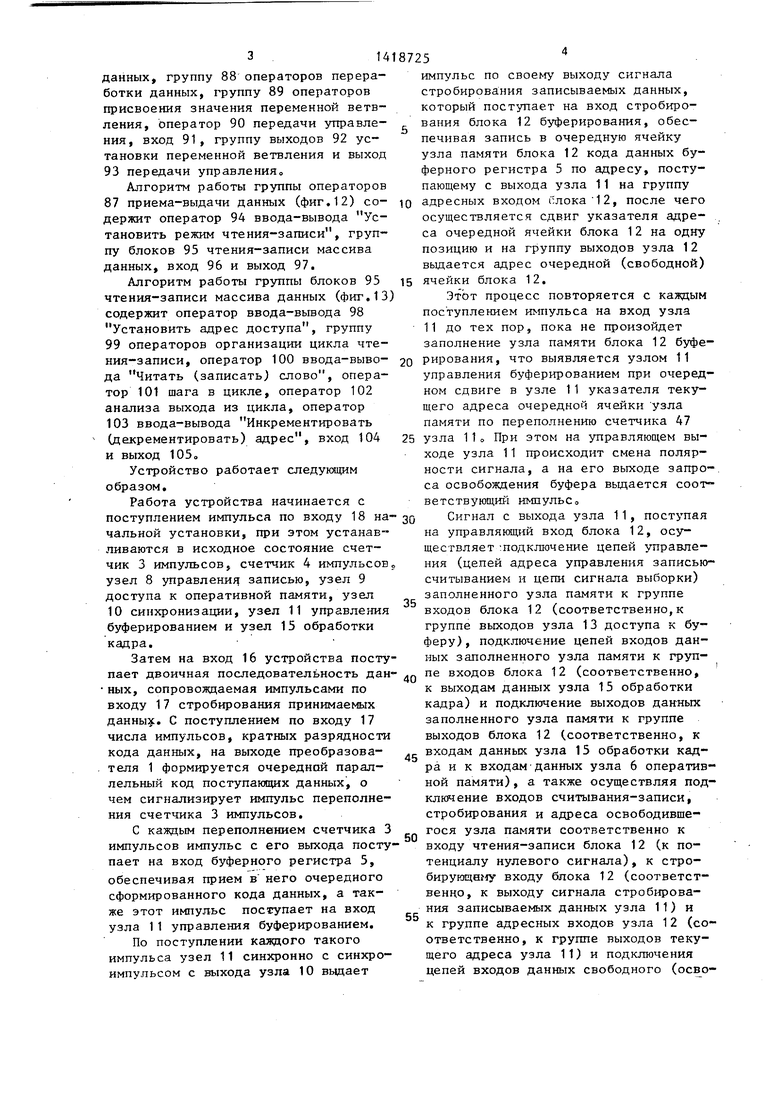

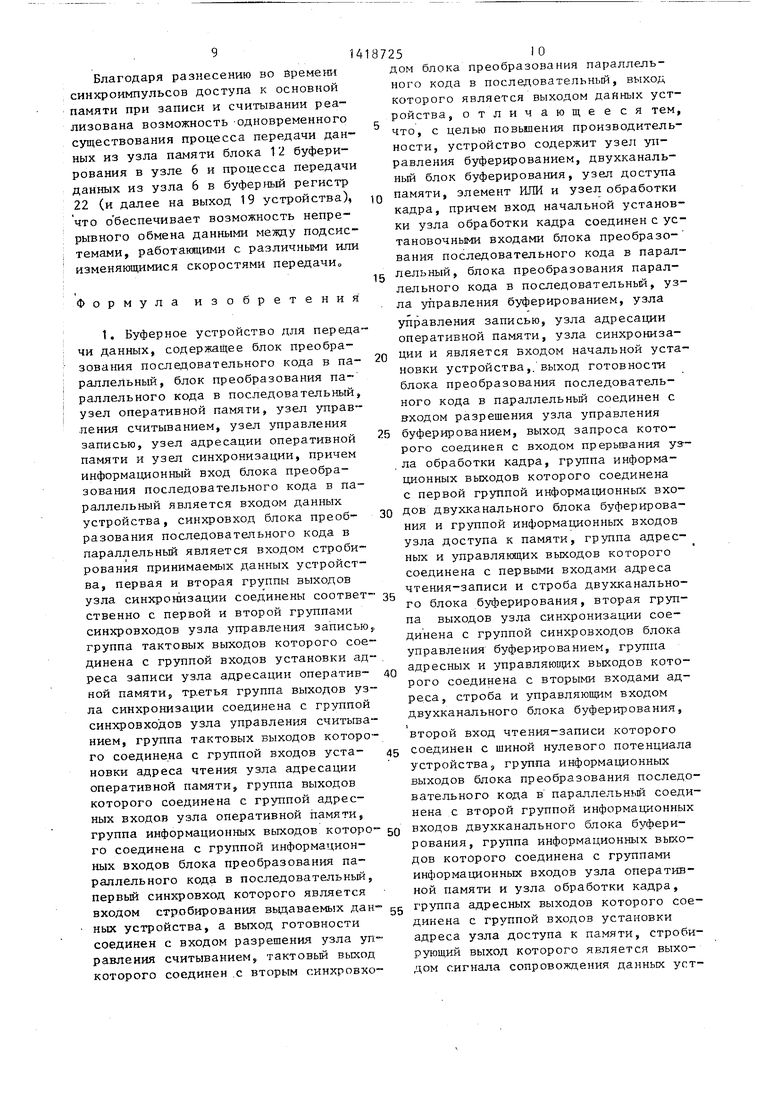

Узел 7 управления считыванием (фиг,2) содержит триггеры 23 и 24 и элементы И 25-28о

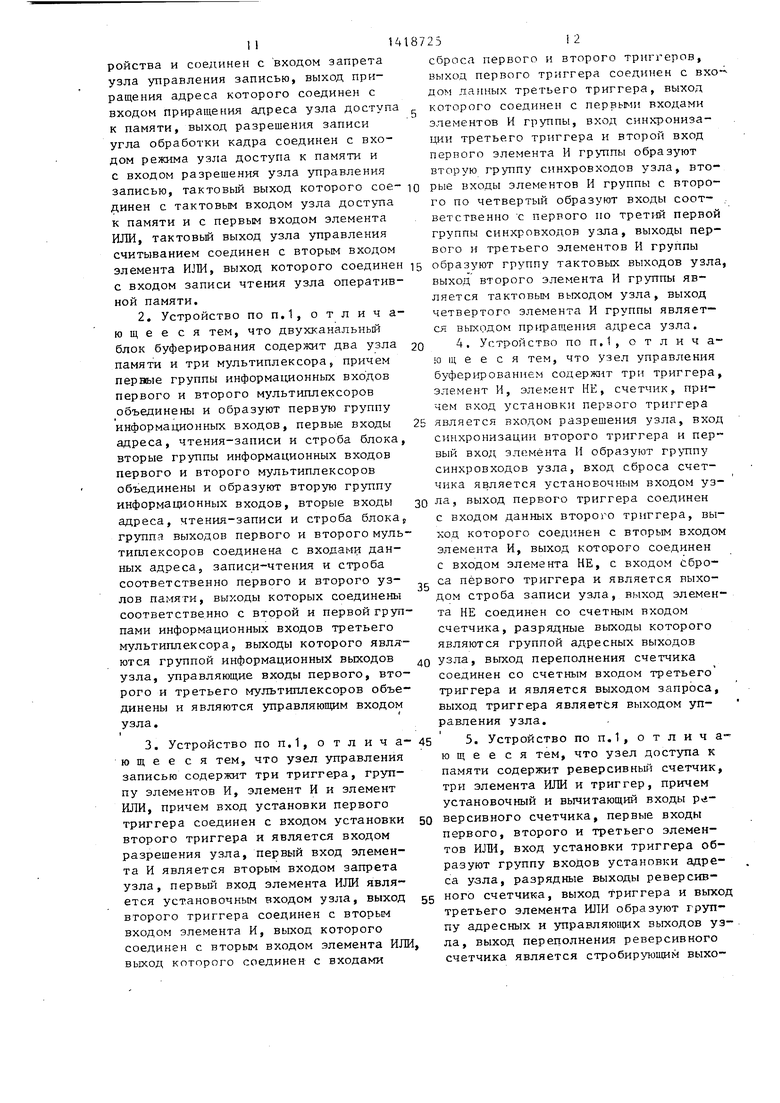

Узел 8 управления записью (фиг.З) содержит триггеры 29-31, элементы И 32-36 и элемент ИЛИ 37.

Узел 9 адресации оперативной памяти (фиг,4) содержит триггер 38, мультиплексор 39 и счетчики 40 и 41.

Узел 11 управления буферированием (фиго 5)содержит триггеры 42-44, элемент И 45, элемент НЕ 46 и счетчик 47«

Двухканальный узел 12 буферирования (фиг.6) содержит узлы 48 и 49 памяти и мультиплексоры 50-52

Узел 13 доступа памяти (фиг,7) содержит реверсивный счетчик 33, элементы ИЛИ 54-56 и триггер 57.

Узел 15 обработки кадра (фиг„8) содержит оперативный блок 58, селектор 59 сигналов выборки, блок 60 прерывания, элементы И 61-65, группу элементов И 66 и элемент ИЛИ 67„

В качестве блока 58 может быть использован программируемый периферийный контроллер

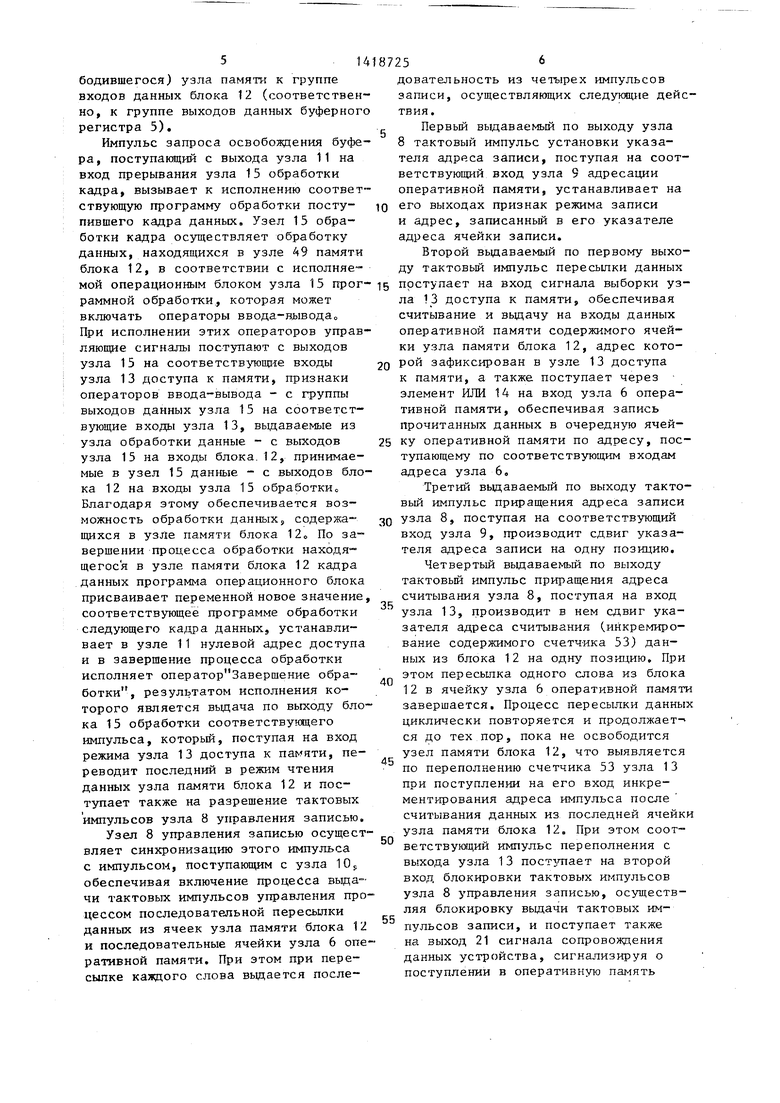

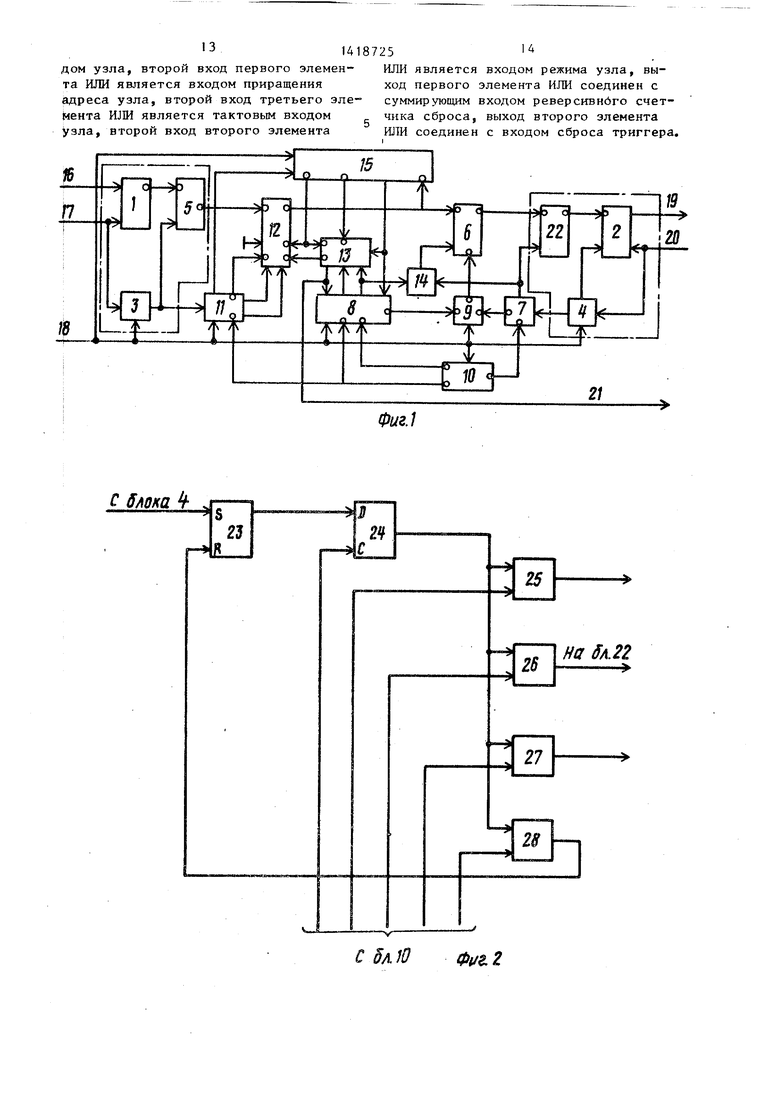

Алгоритм работы операционного блока (фиг,9) содержит группу 68 операторов обработки прерывания, оператор 69 ввода-вывода Чтение прерывания, группу 70 операторов анализа причины прерывания, группу 71 операторов начальной установки параметра ветвления, блок 72 определения программ обработки кадров данных, блок 73 обработки кадра данных, оператор 74 ввода-вывода ГашенИе 1-го флага прерывания, оператор 75 ввода-вывода Гашение 2-го флага прерывания, оператор 76 ввода- вывода Завершение обработки, группу 77 операторов выхода из прерывания, вход 78 прерывания и выход 79 прерывания.

Алгоритм работы блока 72 определения программ обработки кадров данных (фиг. 10). содержит переменную 80 ветвления, оператор 81 чтения переменной ветвления, оператор 82 анализа условия ветвления, группу операторов 83 передачи управления, группу входом 84 установки переменной ветвления, вход 85 и группу выходов 86 передачи управления.

Алгоритм работы блока 73 обработки кадра данных (фиг.11) содержит группу операторов 87 приема-выдачи

10

15

20

25

31418725

анных, группу 88 операторов перераотки данных, группу 89 операторов рисвоения значения переменной ветвения, оператор 90 передачи управлеия, вход 91, группу выходов 92 установки переменной ветвления и выход 93 передачи управления

Алгоритм работы группы операторов 87 приема-выдачи данных (фиг.12) соержит оператор 94 ввода-вывода Установить режим чтения-записи, группу блоков 95 чтения-записи массива анных, вход 96 и выход 97.

Алгоритм работы группы блоков 95 тения-записи массива данных (фиг.13) содержит оператор ввода-вывода 98 Установить адрес доступа, группу 99 операторов организации цикла чтения-записи, оператор 100 ввода-вывоа Читать (записать) слово, оператор 101 шага в цикле, оператор 102 нализа выхода из цикла, оператор 103 ввода-вывода Инкрементировать (декрементировать) адрес, вход 104 и выход 105о

Устройство работает следукяцим бразом.

Работа устройства начинается с поступлением иьшульса по входу 18 на зо чальной установки, при этом устанавиваются в исходное состояние счетик 3 импульсов, счетчик 4 импульсов с зел 8 управления записью, узел 9 оступа к оперативной памяти, узел 10 синхронизации, узел 11 управления буферированием и узел 15 обработки кадра.

Затем на вход 16 устройства поступает двоичная последовательность дан- ных, сопроволщаемая импульсами по входу 17 стробирования принимаемых анны. С поступлением по входу 17 числа импульсов, кратных разрядности кода данных, на выходе преобразователя 1 формируется очередной параллельный код поступающих данных, о чем сигнализирует импульс переполнения счетчика 3 импульсов.

С каждым переполнением счетчика 3 импульсов импульс с его выхода поступает на вход буферного регистра 5, обеспечивая прием в него очередного сформированного кода данных, а также этот импульс посагупает на вход узла 11 управления буферированием.

По поступлении каядого такого импульса узел 11 синхронно с синхроимпульсом с выхода узла 10 выдает

им ст ко ва пе уз па ад ос са по вь яч

по за ри уп но ще п уз хо но са ве

на ще ни сч за вх гр ны пе к ка за вы ,f. вх ра но кл ст го вх т ве ни к от ще це

35

40

50

55

0

5

0

25

зо

импульс по своему выходу сигнала стробирования записываемых данных, который поступает на вход стробирования блока 12 буферирования, обеспечивая запись в очередную ячейку узла памяти блока 12 кода данных буферного регистра 5 по адресу, поступающему с выхода узла 11 на группу адресных входом С:лока 12, после чего осуществляется сдвиг указателя адреса очередной ячейки блока 12 на одну позицию и на группу выходов узла 12 вьщается адрес очередной (свободной) ячейки блока 12.

Этот процесс повторяется с каждым поступлением и тульса на вход узла 11 до тех пор, пока не произойдет заполнение узла памяти блока 12 буферирования, что выявляется узлом 11 управления буферированием при очередном сдвиге в узле 11 указателя текущего адреса очередной ячейки узла памяти по переполнению счетчика 47 узла 11 о При этом на управляющем выходе узла 11 происходит смена полярности сигнала, а на его выходе запро-. са освобождения буфера вьщается соот ветствующий импульс о

Сигнал с выхода узла 11, поступая на управляющий вход блока 12, осуществляет :подклк1чение цепей управления (цепей адреса управления записью- считыванием и цепи сигнала выборки) заполненного узла памяти к группе входов блока 12 (соответственно,к группе выходов узла 13 доступа к буферу) , подключение цепей входов данных заполненного узла памяти к группе входов блока 12 (соответственно, к выходам данных узла 15 обработки кадра) и подключение выходов данных заполненного узла памяти к группе выходов блока 12 (соответственно, к ,f. входам данных узла 15 обработки кадра и к входамданных узла 6 оперативной памяти), а также осуществляя подключение входов считывания-записи, стробирования и адреса освободившегося узла памяти соответственно к входу чтения-записи блока 12 (к потенциалу нулевого сигнала), к стро- бируюцему входу блока 12 (соответственно, к выходу сигнала стробирования записываемых данных узла 11) и к группе адресных входов узла 12 (соответственно, к группе выходов текущего адреса узла 11) и подключения цепей входов данных свободного (осво35

40

50

55

бодившегося) узла памятт: к группе входов данных блока 12 (соответственно, к группе выходов данных буферного регистра 5),

Импульс запроса освобождения буфера , поступающий с выхода узла 11 на вход прерывания узла 15 обработки кадра, вызывает к исполнению соответ™ ствующую программу обработки поступившего кадра данных. Узел 15 обработки кадра осуществляет обработку данных, находящихся в узле 49 памяти блока 12, в соответствии с исполняе

87256

довательность из четырех импульсов записи, осуществляющих следующие действия.

„ Первьм выдаваемый по выходу узла 8 тактовый импульс установки указателя адреса записи, поступая на соответствующий вход узла 9 адресации оперативной памяти, устанавливает на 10 его выходах признак режима записи и адрес, записанньй в его указателе адреса ячейки записи.

Второй вьщаваемый по первому выходу тактовый импульс пересылки данных

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок буферной памяти для терминального устройства | 1989 |

|

SU1633454A1 |

| УСТРОЙСТВО ВВОДА И ХРАНЕНИЯ КЛЮЧЕВОЙ ИНФОРМАЦИИ | 2000 |

|

RU2175775C1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИЗОБРАЖЕНИЯ В ЭВМ | 2000 |

|

RU2166790C1 |

| Логический анализатор | 1986 |

|

SU1410033A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1709328A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

Изобретение относится к вьгчисли- тельной технике и позволяет сократить время обмена информационными сообщениями в вычислительных системах и сетях, выполнить функцию передачи данных между асинхронными подсистемами. Синхронизация и компенсация пиковой разницы передаваемых между подсистемами данных осуществляют ся с помощью узла оперативной памяти, доступ к которому организован путем разнесения во времени циклов записи и считывания. Используя двухканаль- ный узел буферирования между передающей подсистемой и узлом оперативной памяти, осуществляют обработку передаваемых данных при нахождении информационного кадра данных в узле памяти с последующей передачей данных из узла памяти в узел оперативной памяти до окончания заполнения его первого узла памяти, подключенного со стороны передающей подсистемы. 4 3. п. ф-лы, 13 ил.

мой операционным блоком узла 15 прог-ig поступает на вход сигнала выборки уз- раммной обработки, которая может ла 13 доступа к памяти, обеспечивая включать операторы ввода-вывода При исполнении этих операторов управляющие сигналы поступают с выходов

20

узла 15 на соответствуюи ие входы узла 13 доступа к памяти, признаки операторов ввода-вывода - с группы выходов данных узла 15 на соответствующие входы узла 13, выдаваемые из узла обработки данные - с выходов узла 15 на входы блока.12, принимаемые в узел 15 данные - с выходов блока 12 на входы узла 15 обработкио Благодаря этому обеспечивается возможность обработки данных, содержа™ щихся в узЛе памяти блока 12 По за- верщении процесса обработки находящегося в узле памяти блока 12 кадра данных программа операционного блока присваивает переменной новое значение, соответствующее программе обработки следующего кадра данных, устанавливает в узле 11 нулевой адрес доступа и в завершение процесса обработки исполняет оператор 3авершение обработки, результатом исполнения которого является выдача по выходу блока 15 обработки соответствунщего импульса, который, поступая на вход режима узла 13 доступа к памяти, переводит последний в режим чтения данных узла памяти блока 12 и поступает также на разрешение тактовых импульсов узла 8 управления записью,

Узел 8 управления записью осуществляет синхронизацию этого импульса с импульсом, поступающим с узла Ю обеспечивая включение процесса вьща- чи тактовых импульсов управления процессом последовательной пересылки данных из ячеек узла памяти блока 12 и последовательные ячейки узла 6 оперативной памяти. При этом при пересыпке каждого слова вьщается послесчитывание и вьздачу на входы данных оперативной памяти содержимого ячейки узла памяти блока 12, адрес которой зафиксирован в узле 13 доступа

30

35

К памяти, а также поступает через элемент ИЛИ 14 на вход узла 6 оперативной памяти, обеспечивая запись прочитанных данных в очередную ячей- 25 ку оперативной памяти по адресу, поступающему по соответствующим входам адреса узла 6,

Третий выдаваемый по выходу тактовый импульс приращения адреса записи узла 8, поступая на соответствующий вход узла 9, производит сдвиг указателя адреса записи на одну позицию,

Четвертьш вьщаваемый по выходу тактовьй импульс приращения адреса считывания узла 8, поступая на вход узла 13, производит в нем сдвиг указателя адреса считывания (инкремиро- вание содержимого счетчика 53) данных из блока 12 на одну позицию. При этом пересылка одного слова из блока 12 в ячейку узла 6 оперативной памяти завершается. Процесс пересылки данных циклически повторяется и продолжает- ся до тех пор, пока не освободится узел памяти блока 12, что выявляется по переполнению счетчика 53 узла 13 при поступлении на его вход инкре- ментирования адреса импульса после считывания данных из последней ячейки узла памяти блока 12, При этом соот- ветствукидий импульс переполнения с выхода узла 13 поступает на второй вход блокировки тактовых импульсов узла 8 управления записью, осуществляя блокировку вьщачи тактовых импульсов записи, и поступает также на выход 21 сигнала сопровождения данных устройства, сигнализируя о поступлении в оперативную память

40

45

50

55

поступает на вход сигнала выборки уз- ла 13 доступа к памяти, обеспечивая

считывание и вьздачу на входы данных оперативной памяти содержимого ячейки узла памяти блока 12, адрес которой зафиксирован в узле 13 доступа

0

5

К памяти, а также поступает через элемент ИЛИ 14 на вход узла 6 оперативной памяти, обеспечивая запись прочитанных данных в очередную ячей- 5 ку оперативной памяти по адресу, поступающему по соответствующим входам адреса узла 6,

Третий выдаваемый по выходу тактовый импульс приращения адреса записи узла 8, поступая на соответствующий вход узла 9, производит сдвиг указателя адреса записи на одну позицию,

Четвертьш вьщаваемый по выходу тактовьй импульс приращения адреса считывания узла 8, поступая на вход узла 13, производит в нем сдвиг указателя адреса считывания (инкремиро- вание содержимого счетчика 53) данных из блока 12 на одну позицию. При этом пересылка одного слова из блока 12 в ячейку узла 6 оперативной памяти завершается. Процесс пересылки данных циклически повторяется и продолжает- ся до тех пор, пока не освободится узел памяти блока 12, что выявляется по переполнению счетчика 53 узла 13 при поступлении на его вход инкре- ментирования адреса импульса после считывания данных из последней ячейки узла памяти блока 12, При этом соот- ветствукидий импульс переполнения с выхода узла 13 поступает на второй вход блокировки тактовых импульсов узла 8 управления записью, осуществляя блокировку вьщачи тактовых импульсов записи, и поступает также на выход 21 сигнала сопровождения данных устройства, сигнализируя о поступлении в оперативную память

0

5

0

5

очередного информационного кадра данных.

После этого на вход 20 стробирова ния вьщаваемых данных начинают поступать синхроимпульсы, ньдаваемые принимакщей подсистемой. Поступление на вход 20 устройства 1-го импульса стробирования выдаваемых данных приводит к переполнению счетчика 4 импульсов, что приводит к выдаче по его выходу переполнения соответствующего сигнала, поступающего на вход разблокировки тактовых импульсов узла 7 управления считыванием, вырабатываемые тактовые импульсы которого обеспечивают управление считыванием очередного слова данных из ячейки узла 6 оперативной памяти и пересылку его в буферный регистр 22. При этом вьщаются следующие три тактовых импульса,

Первьм, выдаваемый по выходу элемента И 25 узла 7, тактовьй импульс установки указателя адреса считывания группы, поступая на соответствующий вход узла 9, устанавливает на его выходах признак режима считывания и адрес, записанный в указателе адреса ячейки считывания.

Второй, вьщаваемьш по выходу элемента И. 26 узла 7, тактовый импульс пересылки данных, поступая через элемент ИЛИ 14 на вход узла 6 оперативной памяти, обеспечивает чтение и выдачу данных из ячейки, памяти на выходы узла 6, Этот же тактовый импульс поступает на вход регистра 22, обеспечивая запись в него прочитанных из узла 6 данных

Третий, выдаваемый по выходу элемента И 27 узла 7, тактовьй импульс приращения адреса считывания, поступая на соответствующий вход узла 9, производит сдвиг указателя адреса .считывания на одну позицию.

На этом заканчивается чтение и передача слова из очередной ячейки узла 6 в буферный регистр 22, после чего вьщача тактовых импульсов прекращается,

г

Поступающий по входу 20 устройства импульс стробирования предпоследнего разряда приводит к возникновению на выходе счетчика 4 сигнала 55 связей устройства в принимающую подзаполнения, который, поступая на вход режима преобразователя 2, обеспечивает пересьшку содержимого буферного регистра 22 в преобразователь 2 синхронно с поступлением по входу 20 устройства последнего импульса строби- рования с одновременной выдачей на

выход 19 устройства значения старшего разряда пересылаемого кода данных Поступление по входу 20 каждого следующего импульса стробирования выдаваемых данных приводит к вьщаче синхронно с ним по выходу 19 значения

следующего разряда вьщаваемой двоич- . ной последовательности, С поступлением последнего импульса на вход счетчика 4 на его выходе вновь воз-

никает сигнал переполнения, который аналогично описанному инициирует процесс пересылки следующего слова данных из очередной ячейки узла 6 в буферный регистра 22 устройства,

т.е, к моменту завершения преобразования и вьщачи данных по выходу 19 следующая порция (слово) данных находится в буферном регистре 22„ Процесс тактирования выдаваемых

данных со стороны принимающей подсистемы и процесс пересылки следую- щего слова данных из очередной ячейки узла 6 в буферный регистр 22 устройства развиваются параллельно и

независимо одни от другого. Однако последний завершается раньще выдачи последнего бита, поступившего на преобразователь 2, благодаря тоьту что при примененг-ш устройства вьщерживают соответствующее ограничение на максимальную частоту поступления импульсов стробирования выдаваемых данных, определяемое разрядностью преобразователя 2 и быстродействием

основного тактового генератора узла 10 синхронизации.

Принимающая подсистема должна подсчитывать число импульсов, поступивших по выходу 21 устройства за время

сеанса обмена, так как это число определяет количество слов (кратных объему М узла памяти блока 12), пос-. тупивших за время обмена в узел 6 оперативной памяти

50

О начале следующего сеанса обмена передающая подсистема сообщает сигна- лом начальной установки, который поступает на ;вход 18 устройства и вне

систему в виде сигнала начала сеанса связи. После этого процесс обработки передаваемых между подсистемами данных осуществляется описанным образом.

Благодаря разнесению во времени синхроимпульсов доступа к основной памяти при записи и считывании реализована возможность -одновременного существования процесса передачи данных из узла памяти блока 12 буфери- рования в узле 6 и процесса передачи данных из узла 6 в буферный регистр 22 (и далее на выход 19 устройства), что обеспечивает возможность непрерывного обмена данными меткду подсистемами, работанлцими с различными или изменяющимися скоростями передачи

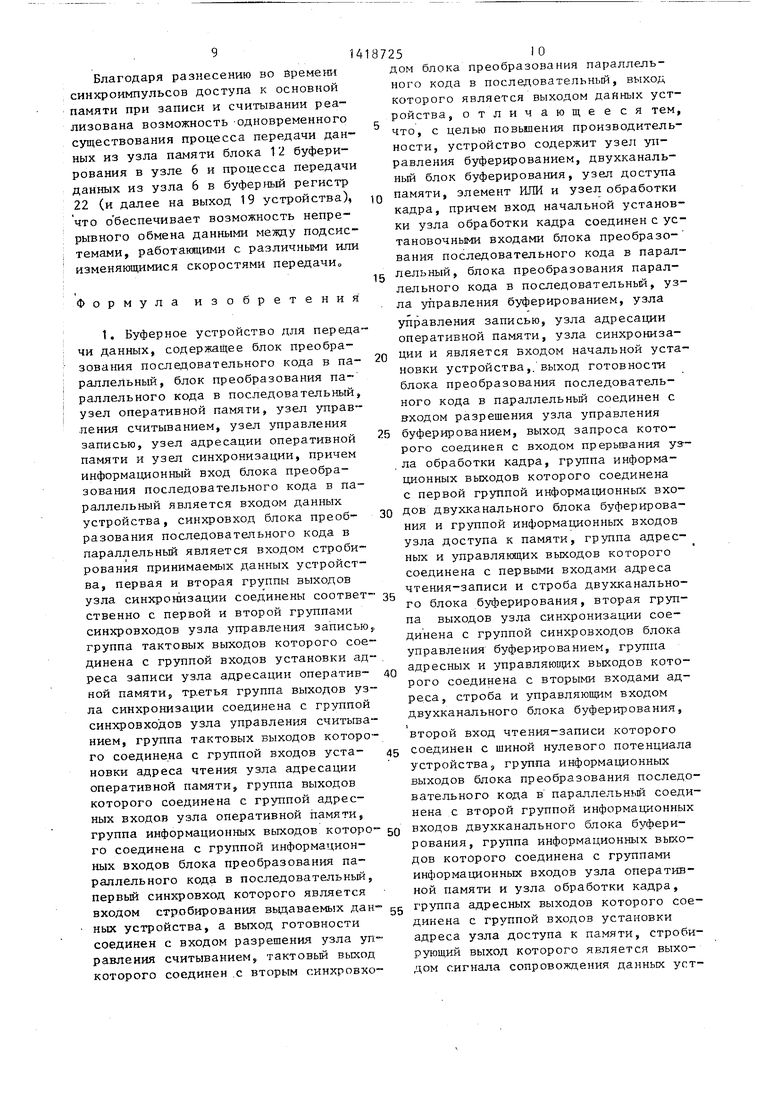

Формула изобретения

ла синхронизации соединена с группой синхровходов узла управления считыванием, группа тактовых выходов которого соединена с группой входов уста- новки адреса чтения узла адресации оперативной памяти, группа выходов которого соединена с группой адресных входов узла оперативной памяти, группа информационных выходов которо- го соединена с группой информационных входов блока преобразования параллельного кода в последовательньй, первьй синхровход которого является входом стробирования выдаваемых дан- ных устройства, а выход готовности соединен с входом разрешения узла управления считыванием, тактовьм выход которого соединен .с вторым синхровхо20

3540

45gQ gg 18725 0

дом блока преобразования параллельного кода в последовательный, выход которого является выходом данных устройства, отличающее ся тем, что, с целью повьшения производительности, устройство содержит узел управления буферированием, двухканаль- ный блок буферирования, узел доступа

Q памяти, элемент ИЛИ и узел обработки кадра, причем вход начальной установки узла обработки кадра соединен с установочными входами блока преобразо- вания последовательного кода в паралjg лельный, блока преобразования параллельного кода в последовательньй, уз- . ла управления буферированием, узла

управления записью, узла адресации оперативной памяти, узла синхронизации и является входом начальной установки устройства,, выход готовности блока преобразования последовательного кода в параллельньй соединен с входом разрешения узла управления буферированием, выход запроса которого соединен с входом прерывания узла обработки кадра, группа информационных выходов которого соединена с первой группой информационных входов двухканального блока буферирования и группой информационных входов узла доступа к памяти, группа адресных и управляющих выходов которого соединена с первыми входами адреса чтения-записи и строба двухканального блока буферирования, вторая группа выходов узла синхронизации соединена с группой синхровходов блока управления буферированием, группа адресных и управляюиц х выходов которого соединена с вторыми входами ад- ре.са, строба и управляющим входом двухканального блока буферирования.

25

30

второй вход чтения-записи которого соединен с шиной нулевого потенциала устройства, группа информационных выходов блока преобразования последовательного кода в параллельный соединена с второй группой информационных входов двухканального блока буферирования, группа информационных выходов которого соединена с группами информационных входов узла оперативной памяти и узла обработки кадра, группа адресных выходов которого соединена с группой входов установки адреса узла доступа к памяти, строби- рующий выход которого является выходом сигнала сопровождения данньк уст111

ройства и соединен с входом запрета узла управления записью, выход приращения адреса которого соединен с входом приращения адреса узла доступа к памяти, выход разрешения записи угла обработки кадра соединен с входом режима узла доступа к памяти и с входом разрешения узла управления записью, тактовьш выход которого сое- динен с тактовым входом узла доступа к памяти и с первым входом элемента ИЛИ, тактовый выход узла управления считыванием соединен с вторым входом элемента ИЛИ, выход которого соединен с входом записи чтения узла оперативной памяти.

блок буферирования содержит два узла памяти и три мультиплексора, причем первые группы информационных входов первого и второго мультиплексоров объединены и образуют первую группу информационных входов, первые входы адреса, чтения-записи и строба блока вторые группы информационных входов первого и второго мультиплексоров объединены и образуют вторую группу информационных входов, вторые входы адреса, чтения-записи и строба блока группа выходов первого и второго мультиплексоров соединена с входами данных адреса, записи-чтения и строба соответственно первого и второго узлов памяти, выходы которых соединены соответственно с второй и первой груп пами информационных входов третьего мультиплексора, выходы которого являются группой информационных выходов узла, управляющие входы первого, второго и третьего мультиплексоров объединены и являются управляюш м входом узла.

I

5 о Q

5 0 5

5

251 2

сброса первого и второго триггеров, выход первого триггера соединен с вхо- дом данных третьего триггера, выход которого соединен с первыми входами элементов И группы, вход синхронизации третьего триггера и второй вход первого элемента И образуют вторую группу синхровходов узла, вторые входы элементов И группы с второго по четвертый образуют входы соот- , ветственно с первого по третгш первой группы синхровходон узла, выходы первого и третьего элементов И группы образуют группу тактовых выходов узла, выход второго элемента И группы является тактовым выходом узла, выход четвертого элемента И группы является выходом пр1фащения адреса узла.

4, Устройство по п,1, о т л и ч а- ю щ е е с я тем, что узел управления буфер1фованием содержит три триггера, элемент И, элемент НЕ, счетчик, причем вход установки первого триггера является входом разрешения узла, вход синхронизации второго триггера и пер вый вход элемента И образуют группу синхровходов узла, вход сброса счетчика является установочным входом узла, выход первого триггера соединен с входом данных второго триггера, выход которого соединен с вторым входом элемента И, выход которого соединен с входом элемента НЕ, с входом сброса первого триггера и является выходом строба записи узла, выход элемента НЕ соединен со счетным входом счетчика, разрядные выходы которого являются группой адресных выходов узла, выход переполнения счетчика соединен со счетным входом третьего триггера и является выходом запроса, выход триггера является выходом управления узла.

дом узла, второй вход первого элемен- ИЛИ является входом режима узла, вы- та ИЛИ является входом приращения ход первого элемента ИЛИ соединен с адреса узла, второй вход третьего эле- суммируюЕцим входом реверсивнйго счет- нента ИЛИ является тактовым входом чика сброса, выход второго элемента узла, второй вход второго элемента ИЛИ соединен с входом сброса триггера.

Фt/&2

5f

31

33

34

Фиг.З

Ф1/&

«

49

7 hH w

г

Фиг,6

57

Фиг. 7

Фиг. 9

т

97

Авторы

Даты

1988-08-23—Публикация

1987-01-14—Подача