Изобретение относится к автомати- к|е и вьмислительной технике и может бЬггь использовано з устройствах числового программного управления металлообрабатывающим оборудованием, в трм числе металлорежущими станками, пьомьшотенными роботами, кузнечно- п;рессовым оборудованием.

Целью изобретения является сокращение аппаратных затрат на блок ha- мяти дпя хранения управляюпщхпрограмм

и

.повышение его надежности.

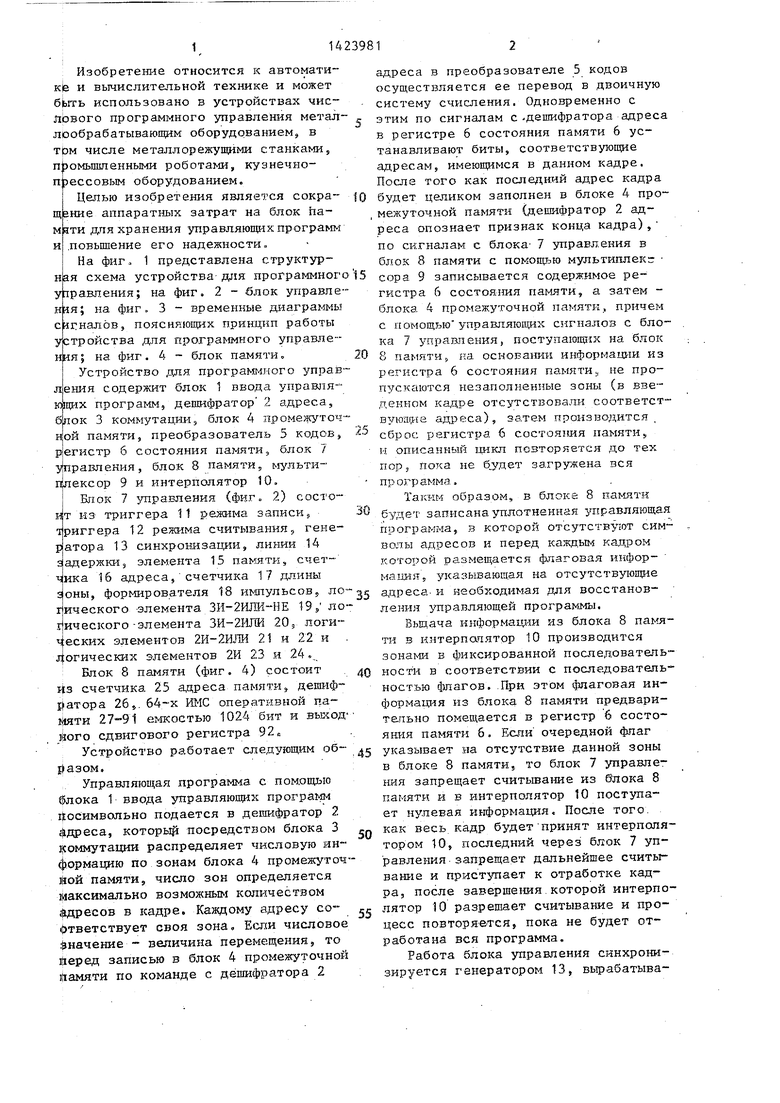

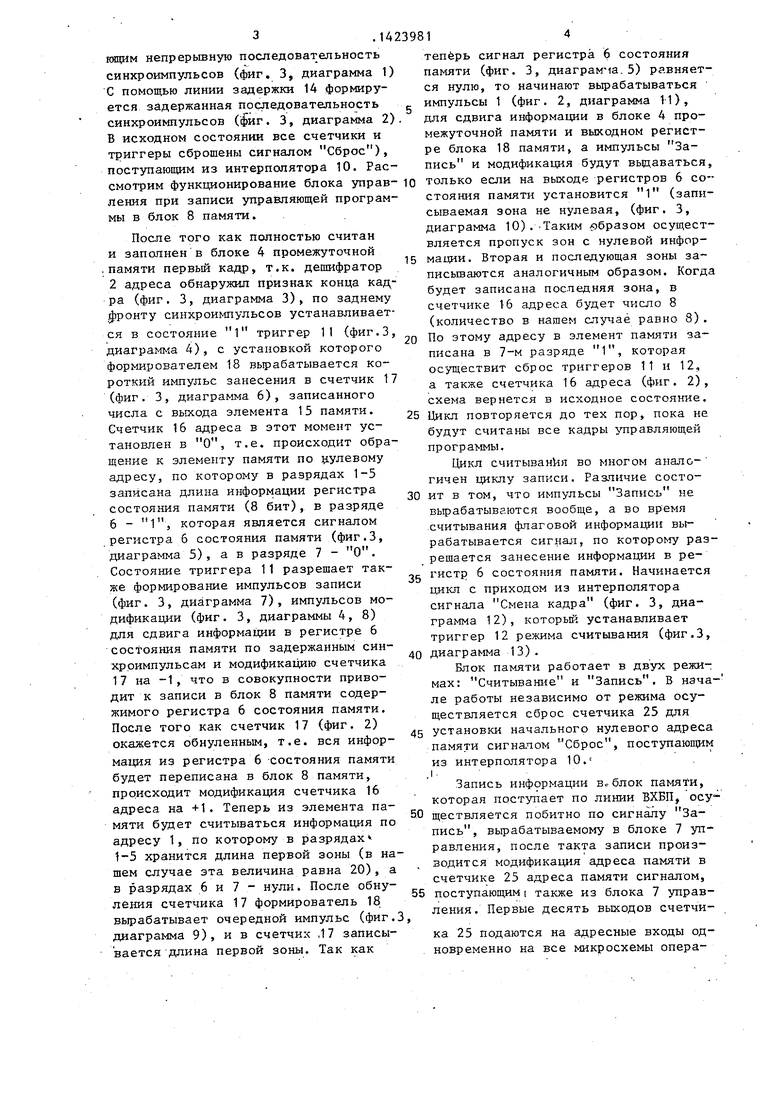

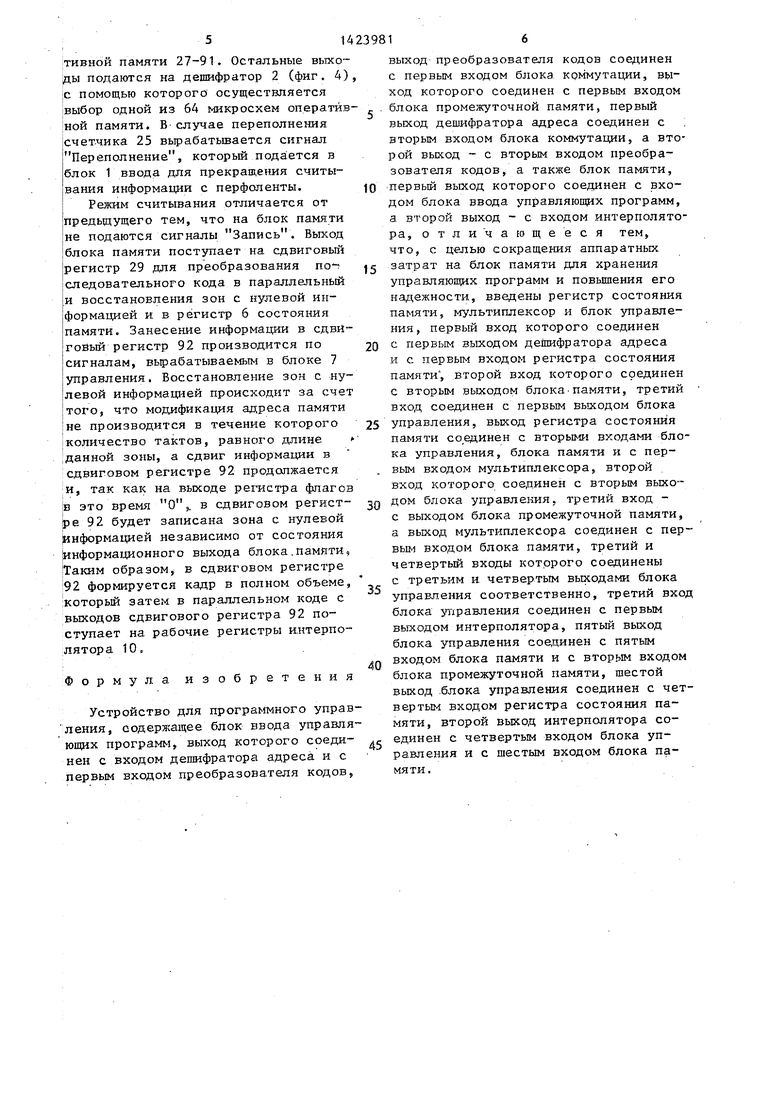

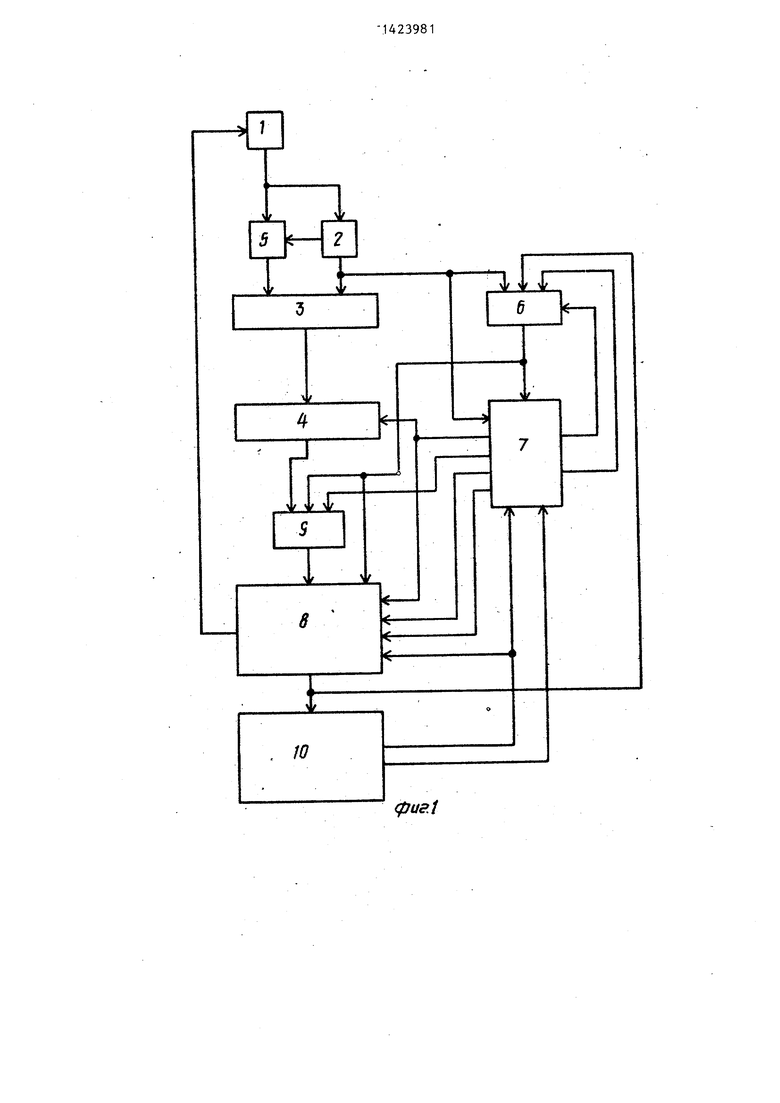

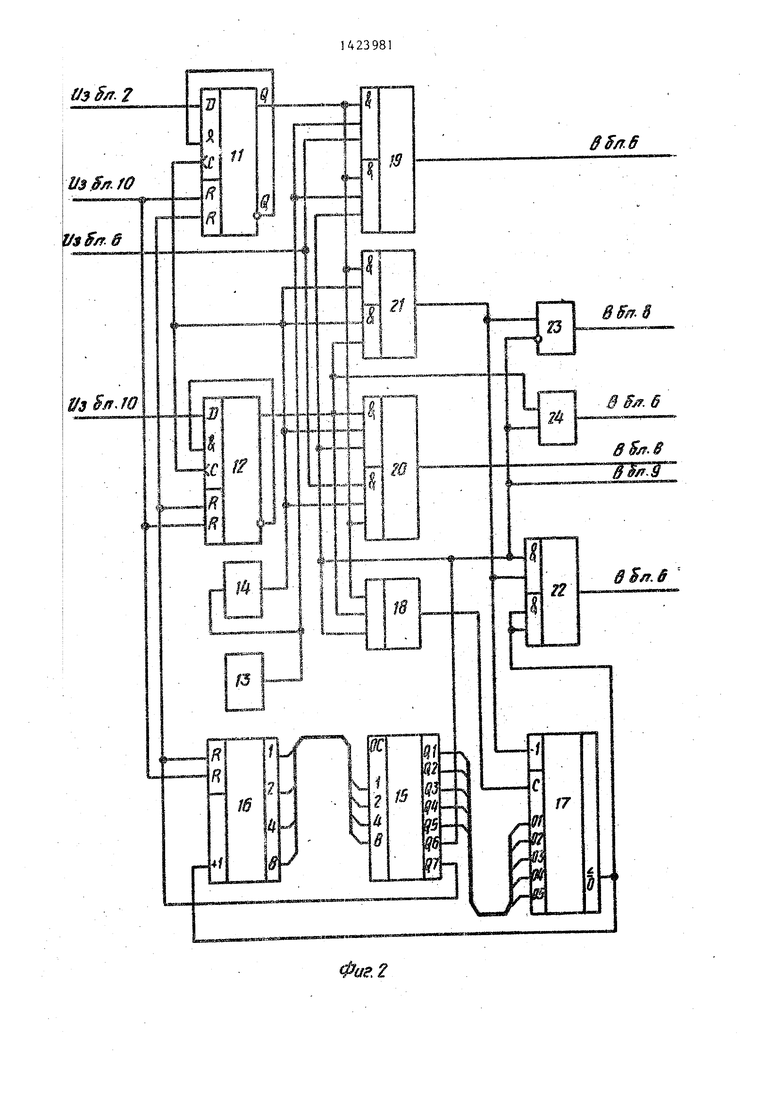

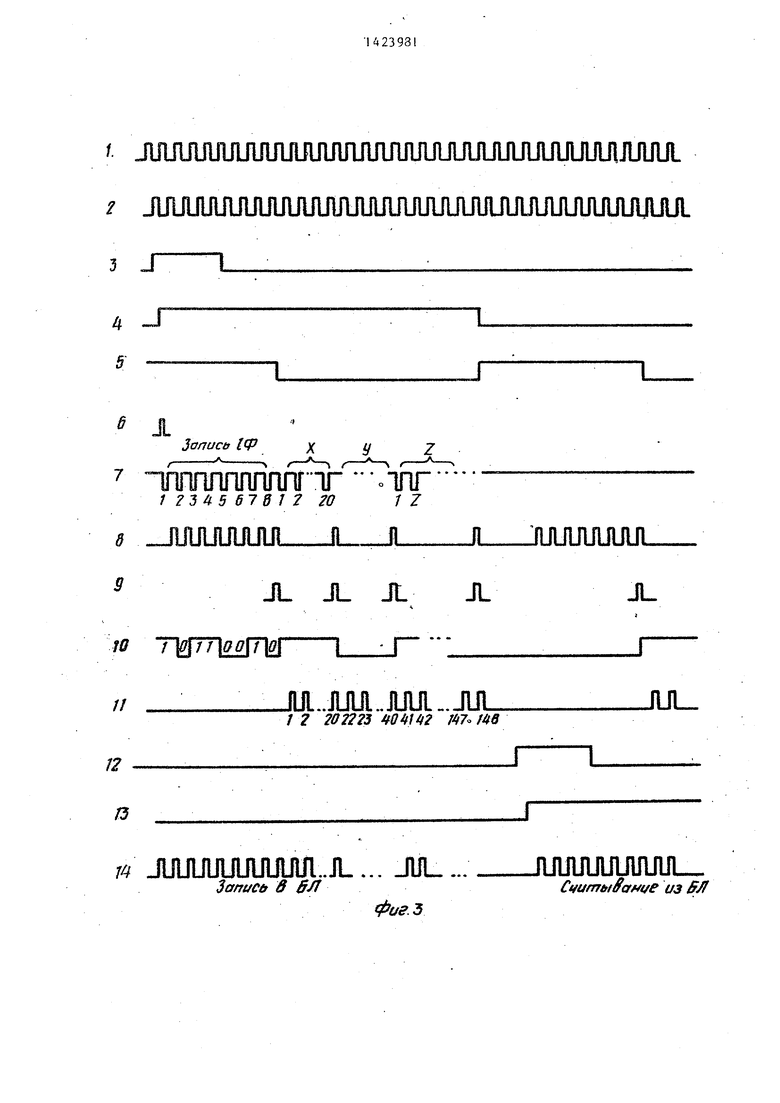

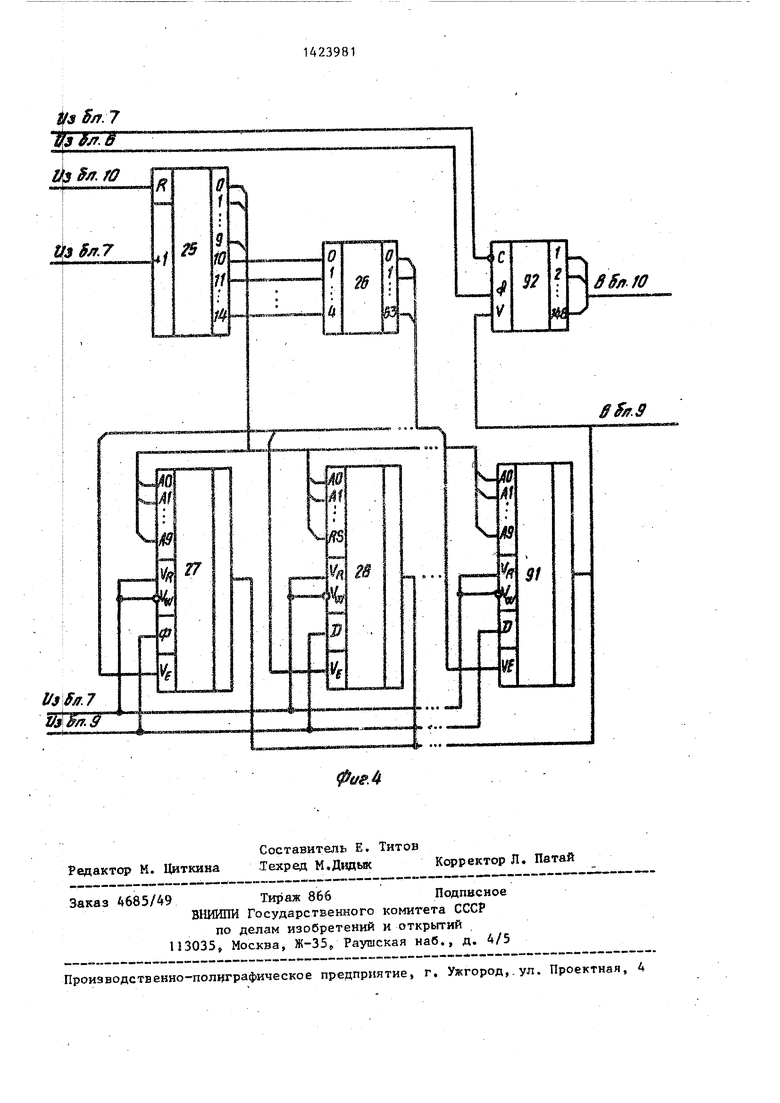

На фиг« 1 представлена структурная схема устройства-для программног управления; на фиг. 2 блок управления; на фиг. 3 - временные диаграммы сигналов, поясняющих принцип работы устройства для программного управления; на фиг. 4 блок памяти,

Устройстйо для программного управления содержит блок 1 ввода управляющих программ, дешифратор 2 адреса, бпок 3 коммутацииэ блок 4 промелсуточ ной памяти, преобразователь 5 кодов регистр б состояния памяти, блок 7 управления, блок 8 памяти, мульти- п|лексор 9 и интерполятор 10,

Клок 7 управления (фиг. 2) состо- из триггера 11 режима записИг

триггера 12 режима считывания, генератора 13 синхронизации, линии 14 адержки, элем:ента 15 памяти, счет- ика 16 адреса, счетчика 17 длины оны, формирователя 18 импульсов, ло г|ического -элемента ЗИ-2ИЛИ-НЕ 19з, ло

гического-элемента 20, логи-- ч:еских элементов 2И-2ИЛИ 21 и 22 и л:огических элементов 2И 23 и 24 «

Блок 8 памяти (фиг. 4) состоит Из счетчика 25 а,цреса памяти, дешифратора 26. ИМС оперативной па Кюти 27-91 е1 жостьго 1024 бит и йоге сдвигового регистра 92

Устройство работает сгседующим об- разоы,

Управляющая программа с помящыо Шлока 1- ввода управляющих nporpai i посимвольно подается в дешифратор 2 г дреса, которы|1 посредством блока 3 1 оммутации распределяет числовую информацию по зонам блока 4 промежуточной памяти, число зон определяется максимально возможным количеством i&ApecoB в кадре. Каждому адресу со- Ответствует своя зона, Е«1пи числовое; :&наченне - величина пер вмещения j то йеред записью в блок 4 промежуточной 1|1амяти по команде с дешифратора 2

8

адреса в преобразователе 5 кодов осуществляется ее перевод в двоичную систему счисления. Одновременно с этим по сигналам с-дешифратора адреса в регистре 6 состояния памяти 6 устанавливают биты, соответствующие адресам, имеющимся в данном кадре. После того как последний адрес кадра будет целиком заполнен в блоке 4 промежуточной памяти (дешифратор 2 адреса опознает признак конца кадра), по сигналам с блока- 7 управления в блок 8 памяти с помощью мультиплекг - сора 9 записывается содержимое регистра 6 состояния , а затем - блока 4 промежуточной памяти, причем с помощью управляющих сигналов с блока 7 управленияJ поступающих на блок 8 памяти, на осиова11ии информации из регистра 6 состояния памяти, не пропускаются незаполненные зоны (в введенном кадре отсутствовали соответст- вуюп(ие адреса), затем производится сброс регистра, б состояния памяти и описанный цикл повторяется до тех пор 5 пока не б.удет загружена вся пpoгpa 5мa.

Таким образом, в блоке. 8 памяти будет записана уплотненная управляющая программа, в которой отсутств-уют сим

волы адресов и перед каждым кадром которой размещается флаговая ннфор- - MauHiT, указываюгаая на отсутствующие а,цреса- и необходимая для восстановления управляющей программы,

Выдача информации из блока 8 памяти в интерполятор 10 производится зонами в фиксированной последовательности в соответстаии с последовательностью 4uiaroB. .При этом флаговая информация из блока 8 памяти предвари- тепьно помещается в регистр 6 состояния памяти б. Если очередной флаг указывает на отсутствие данной зоны в блоке В памяти, то блок 7 управления запрещает считывание из блока 8 памяти и в интерполятор 10 поступает нупевая информация. После того, как весь кадр будет принят интерполятором 10, последний через блок 7 управления .запрещает дальнейшее считывание и приступает к отработке кадра, после завершения которой интерполятор 10 разрешает считывание и процесс повторяе-тся, пока не будет отработана вся программа.

Работа блока управления синхронизируется генератором 13, вырабатываккцим непрерывную последовательность синхроимпульсов (фиг. 3, диаграмма 1) С помощью линии задержки 14 формируется задержанная последовательность (. синхроимпульсов (фиг. 3, диаграмма 2). В исходном состоянии все счетчики и триггеры сброшены сигналом Сброс), поступающим из интерполятора 10. Рассмотрим функционирование блока управ- 10 Ленин при записи управляющей программы в блок 8 памяти.

После того как полностью считан и заполнен в блоке 4 промежуточной .памяти первый кадр, т.к. дешифратор 2 адреса обнаружил признак конца кадра (фиг. 3, диаграмма 3), по заднему фронту синхроимпульсов устанавливается в состояние 1 триггер 11 (фиг.З, диaгpaм 5a 4), с установкой которого формирователем 18 вырабатывается короткий импульс занесения в счетчик 17 (фиг. 3, диаграмма 6), записанного числа с выхода элемента 15 памяти. Счетчик 16 адреса в этот момент установлен в О, т.е. происходит обращение к элементу памяти по вдлевому адресу, по которому в разрядах 1-5 записана длина информации регистра состояния памяти (8 бит), в разряде 6 - 1, которая является сигналом регистра 6 состояния памяти (фиг.3, диаграмма 5), а в разряде 7 - О. Состояние триггера 11 разрешает также формирование импульсов записи (фиг. 3, диаграмма 7), импульсов модификации (фиг. 3, диаграммы 4, 8) для сдвига информации в регистре 6 состояния памяти по задержанным синхроимпульсам и модификацию счетчика 17 на -1, что в совокупности приводит к записи в блок 8 памяти содержимого регистра 6 состояния памяти. После того как счетчик 17 (фиг. 2) окажется обнуленным, т.е. вся информация из регистра 6 состояния памяти будет переписана в блок 8 памяти, происходит модификация счетчика 16 адреса на +1. Теперь из элемента памяти будет считываться информация по адресу 1, по которому в разрядах 1-5 хранится длина первой зоны (в нашем случае эта величина равна 20), а в разрядах 6 и 7 - нули. После обнуЗапись информации в.блок памяти, которая поступает по линии ВХБП, осу- 50 ществляется побитно по сигналу Запись, вьфабатываемому в блоке 7 управления, после такта записи произ- . водится модификация адреса памяти в счетчике 25 адреса памяти сигналом, 55 поступающим i также из блока 7 управления счетчика 17 формирователь 18 вьфабатывает очередной импульс (фиг.З, ™«- выходов счетчи- диаграмма 9), и в счетчик Л 7 записывается длина первой зоны. Так как

ка 25 подаются на адресные входы одновременно на все микросхемы оператеперь сигнал регистра 6 состояния памяти (фиг. 3, диаграмма.5) равняется нулю, то начинают вырабатываться импульсы 1 (фиг. 2, диаграмма 11), для сдвига информации в блоке 4 промежуточной памяти и выходном регистре блока 18 памяти, а импульсы Запись и модификация будут вццаваться.

только если на выходе регистров 6 состояния памяти установится 1 (записываемая зона не нулевая, (фиг. 3, диаграмма 10),-Таким /образом осуществляется пропуск зон с нулевой информации. Вторая и последующая зоны за- письшаются аналогичным образом. Когда будет записана последняя зона, в счетчике 16 адреса будет число 8 (количество в нашем случае равно 8).

По этому адресу в элемент памяти записана в 7-м разряде 1, которая осуществит сброс триггеров 11 и 12, а также счетчика 16 адреса (фиг. 2), схема вернется в исходное состояние.

Цикл повторяется до тех пор, пока не будут считаны все кадры шравляющей программы.

Цикл считывания во многом анало- гичен циклу записи. Различие состоит в том, что импульсы Запись не вырабатываются вообще, а во время считывания флаговой информации вырабатывается сигнал, по которому разрешается занесение информации в регистр 6 состояния памяти. Начинается цикл с приходом из интерполятора сигнала Смена кадра (фиг. 3, диаграмма 12), который устанавливает триггер 12 режима считывания (фиг.З,

диаграмма 13).

Блок памяти работает в двух режимах; Считывание и Запись. В нача- ле работы независимо от режима осуществляется сброс счетчика 25 для

установки начального нулевого адреса памяти сигнатом Сброс, поступающим из интерполятора 10.

Запись информации в.блок памяти, которая поступает по линии ВХБП, осу- 50 ществляется побитно по сигналу Запись, вьфабатываемому в блоке 7 управления, после такта записи произ- . водится модификация адреса памяти в счетчике 25 адреса памяти сигналом, 55 поступающим i также из блока 7 управ ™«- выходов счетчи-

™«- выходов счетчи-

ка 25 подаются на адресные входы одновременно на все микросхемы опера514

тивной памяти 27-91. Остальные выхо- ры подаются на дешифратор 2 (фиг. 4) ;С помощью которого осуществлявтся 1выбор одной из 64 ivffitKpocxeM оператйв- ной памяти. В случае переполнения |счет.чика 25 вырабатывается сигнал Переполнение, который пода;ется в блок 1 ввода для прекраш,еиия считывания информации с перфоленты. Режим считывания отличается от |предьщущего тем, что на блок памяти |не подаются сигналы Запись. Выход |блока памяти поступает на сдвиговый |регистр 29 для преобразования по-- |следовательного кода в параллельный |и восстановления зон с нулевой информацией и в регистр 6 состояния памяти. Занесение информации в сдвиговый регистр 92 производится по сигналам, вырабатываемым в блоке 7 управления. Восстановление зон с нулевой информацией происходит за счет |того, что модификация адреса памяти |не производится в течение которого Iколичество тактов, равного длине :данной зоны, а сдвиг информации в сдвиговом регистре 92 продолжается

и, так как на выходе рех истра флагов IB это время 0 в сдвиговом регист- ре 92 будет записана зона с нулевой |информацией независимо от состояния Информационного выхода блока.памяти, |Таким образомS в сдвиговом регистре :92 формируется кадр в полном объеме, :который затем в параллельном коде с выходов сдвигового регистра 92 поступает на рабочие регистры интерполятора 10.

Формула изобретения

Устройство для программного управ- ления, содержащее блок ввода управляющих программ, выход которого соеди- иен с входом дешифратора адреса и с первым входом преобразователя кодов.

выход преобразователя кодов соединен с первым входом блока коммутации, вы ход которого соединен с первым входом блока промежуточной памяти, первый выход дешифратора адреса соединен с вторым входом блока коммутации, а второй выход - с вторым входом преобразователя кодов, а также блок памяти, первый выход которого соединен с входом блока ввода управляющих программ, а второй выход с входом интерполятора, отличающееся тем, что, с целью сокращения аппаратных затрат на блок памяти для хранения управляющих программ и повышения его надежности, введены регистр состояния памяти, мультиплексор и блок управления, первый вход которого соединен с первым выходом дешифратора адреса и с первьш входом регистра состояния памяти , второй вход которого соединен

с вторым выходом блока памяти, третий вход соединен с первым выходом блока управления, выход регистра состояния памяти со,единен с вторыми входами блока управления, блока памяти и с первым входом мультиплексора, второй вход которого соединен с вторым выходом блока управления, третий вход - с выходом блока промежуточной памяти, а выход мультиплексора соединен с первым входом блока памяти, третий и четвертый входы которого соединены с третьим и четвертым выходами блока управления соответственно, третий вход блока управления соединен с первым вь ходом интерполятора, пятый выход блока управления сое,цинен с пятым входом блока памяти и с втор.ым входом блока промежуточной памяти, шестой выход .блока управления соединен с четвертым входом регистра состояния памяти, второй выход интерполятора соединен с четвертым входом блока управления и с шестым входом блока памяти .

JLJaL

У i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство памяти на кадр цифрового теливизионного изображения | 1988 |

|

SU1600002A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1674221A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

| Система числового программного управления с постоянной скоростью резания для токарно-винторезных станков | 1981 |

|

SU978102A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах числового программного управления металлообрабатывающим оборудованием. Цель изобретения - сокращение аппаратных затрат на блок памяти для хранения управляющих программ и повышение его надежности. Эта цель достигается тем, что в устройство для программного управления, содержащее блок ввода управляющих программ, дешифратор адреса, преобразователь кодов, блок коммутации, блок промежуточной памяти, блок памяти управляющей программы, включенньй между блоком промежуточной памяти и интерполятором, AononHiiTenbHo введены регистр состояния памяти, блок управления и мультиплексор, причем входы регистра состояния памяти связаны с выходами дешифратора адреса, блока управления и блока памяти, а его выход присоединен к входам блока управления и мультиплексора, другие входы мультиплексора соединены с выходами блока промежуточной памяти и блока управления, выход мультиплексора присоединен к блоку памяти, другие входы блока управления подключены к вьгкодам интерполятора и дешифратора адреса, а другой выход блока управления присоединен к входу блока памяти. Использование предлагаемого устройства позволяет сократить почти в два раза аппаратные затраты на блок памяти для хранения управляющих программ 3 системах ЧПУ при сохранении заданного информационного объема памяти. Кроме того, за счет уменьшения количества элементов блока памяти в два раза надежность этого блока возрастает в два раза. 4 ил. сл го со оо

8

е

фиг.1

{J3§/f.2

Фае. 2

9

.6

JlIlШlШLПJUl lJLnJUШШUlllnJШlnJL(UlJlMЛ г ЖМЛШиии1Ши ШГ1Шииши11иШШ 1Ш

3 J

ц J

5 -

JL

Запись Ifp

TinnnnnnnnfTr 1Г

12 5 ПППППППП И ПП ПППППППП

74 JUI UUUUIJUIM..JL... JUL... nnnnnnnnnn

3anuctt в &f Cvumtiiffa ve из ff/f

Фиг.З

3 ёл7

УЗ ffJ7. в

Ш S/f. Ю

4/

5

.

/&

-4Ц

ЧМТМ

™

0

f

17

U45

ч.

.7

.3

W

/

Л7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Разработка, изготовление и внедрение аппаратуры ускоренной подготовки управляющих программ для станков с ЧПУ | |||

| № гос.per | |||

| 74031070, т | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

Авторы

Даты

1988-09-15—Публикация

1986-12-29—Подача