45

to СП

о о:

4

Изобретение относится к вычислительной технике и может быть исполь- аовано в специальных цифровых устройствах .

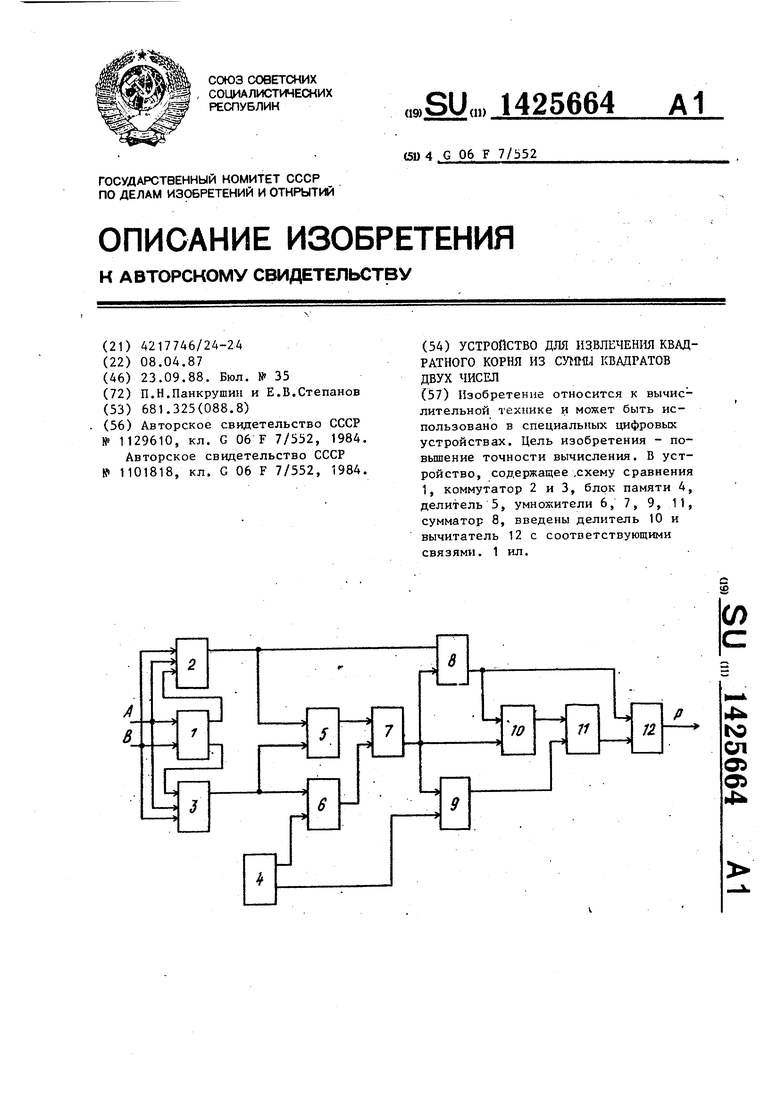

Целью изобретения является повьш1е- : ние точности вычисления. I На чертеже представлена блок-схема I устройства.

Устройство для извлечения корня |из суммы квадратов двух чисел содер- |жит схему 1 сравнения, коммутаторы |2 и 3, блок 4 памяти, первый дели- |тель 5, первый 6 и второй 7 умножители, сумматор 8, третий умножитель 9, второй делитель 10, четвертый умножитель 11, вычитатель 12.

Работа устройства основана на ис- )оользовании алгоритма приближенного

вычисления ч А + Ьамене функции

В

и заключается в

lA -f-B2 |A| 1 + |fi |A fbil2

Ые К , пррксимирующей функцией

А + С

А+С

(2)

тЫе С

В -.

-

: Коэффициенты, входящие в (2), со- с тветственно равны:

: с 0,519598; : f 0,501141.

Устройство работает следующим образом.

На вход схемы 1 сравнения и коммутаторов 2-й 3 подаются коды положительных чисел. При этрм вьпсодной сиг-нал схемы 1 сравнения разрешает про- хоадение кода большего числа на выход коммутатора 2 и меньшего числа В на выход коммутатора 3, Далее производится параллельное перемножение числа В и коэффициента «С в умножителе 6 и деление числа В на А в делителе 5, В умножителе 7 производится перемножение результатов и/А и В-Х.

Таким образом, на выходе умножителя 7 появляется промежуточный результат С. Далее производится парал- лельное перемножение результата С и коэффициента в умножителе 9 и

0

5

0

5

5

суммирование результата С и числа А в сумматоре 8. В делителе Ю произ- .водится деление результата С на С+А. В умножителе 11 производится перегмножение результатов --- и С-. В вы Vj А

читателе 12 производится вычитание

С результата А+С и , с выхода коА VJ

торого считывается результат. Формула изобретения

Устройство для извле чения квадратного корня из суммы квадратов двух чисел, содержащее схему сравнения, первый и второй коммутаторы, блок памяти, с первого по четвертый умножи0 тели, сумматор и первый делитель,

причем входы первого-и второго операн - дов первого делителя соединены с выходами соответственно первого и второго коммутаторов, управляющие входы

5 которых подключены к первому и второму выходам схемы сравнения, первый

вход которой соединен с входом первого числа устройства и с первыми информационными входами первого и 0 второго коммутаторов, вторые информационные входы которых и второй вход схемы сравнения подключен к входу второго числа устройства, выход первого делителя соединен с первым входом второго умножителя, второй вход которого подключен к выходу первого умножителя, первый и второй входы которого соединены с выходом второго коммутатора и первым выходом блока па-, мяти, отличающееся тем, что, с целью повышения точности вычисления, в него введены второй делитель и вычитатель, причем первый вход вычитателя соединен с выходом сумматора и входом первого аргумента второго делителя, вход второго аргумента которого соединен с выходом второго умножителя и первыми входами сумматора и третьего умножителя, вторые входы которых подключены к выходам соответственно второго коммутатора и второму выходу блока памяти, выходы третьего умножителя и второго делителя соединены с первым и вторым входами четвертого умножителя, выход которого подключен к второму входу вычитателя, выход которого является выходом устройства.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1101818A1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для вычисления квадратного корня из суммы квадратов трех чисел | 1985 |

|

SU1262488A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления функций у=aRcSINx и у=aRccoSx | 1980 |

|

SU935949A1 |

| Статический анализатор | 1988 |

|

SU1727140A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

Изобретение относится к вычислительной технике и может быть использовано в специальных цифровых устройствах. Цель изобретения - по- вьппение точности вычисления. В устройство, содержащее .схему сравнения 1, коммутатор 2 и 3, блок памяти 4, делитель 5, умножители 6, 7, 9, 11, сумматор 8, введены делитель 10 и вычитатель 12 с соответствующими связями. 1 ил.

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1129610A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1101818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-04-08—Подача