|я

(Л

о со о

О5

СО

//

Изобретение относится к вычислительной технике и может быть иснользовано в специализированных преобразователях.

Цель изобретения - повышение точности вычислений.

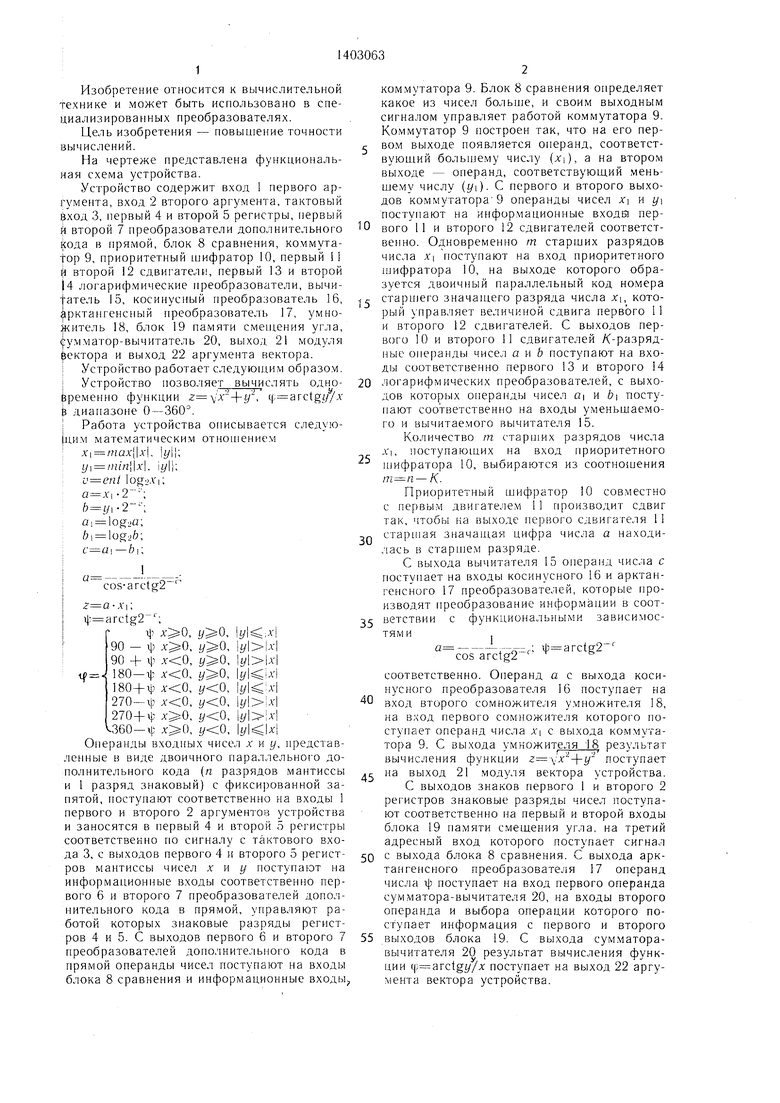

На чертеже представлена функциональная схема устройства.

Устройство содержит вход 1 первого аргумента, вход 2 второго аргумента, тактовый еход 3, первый 4 и второй 5 регистры, первый и второй 7 преобразователи дополнительного йода в прямой, блок 8 сравнения, коммута- fop 9, приоритетный нифратор 10, первый 11 и второй 12 сдвигатели, первый 13 и второй |4 логарифмические преобразователи, вычи- |атель 15, косинусный преобразователь 16, |1рктангенсный нреобразовате.ть 17, умно- |китель 18, блок 19 памяти смеи1ения угла, ({:умматор-вычитатель 20, выход 21 модуля ректора и выход 22 аргу.мента вектора. I Устройство работает следующим образом. I Устройство позволяет вычислять временно функции , ц. (з диапазоне О-360.

I Работа устройства о 1исывается следую- цим математическим отношением Х тах X ,

L/ iiiin x. iyli;

i cnl

а л-|-2 ;

6 yi-2- ;

Oi log2o;

/7i logo6; : 6- ai-61;

ОДНОarctgy/ Acos-arctg2

, ,|: arctg2 ;

ij) , , 90 - 4) . , 90 + H) , , J 180 -t , , 180+4) , , ) 0, , 270+4-- , , 360-4- , , lyKJA l Операнды входных чисел x и у, нредстав- ленные в виде двоичного параллельного до- полнительн01-о кода (п разрядов мантиссы и 1 разряд знаковый) с фиксированной запятой, ноступают соответственно на входы 1 первого и второго 2 аргументов устройства и заносятся в первый 4 и второй 5 регистры соответственно по сигналу с тактового входа 3, с выходов первого 4 и второго 5 регистров мантиссы чисел х и у поступают на информационные входы соответственно первого 6 и второго 7 преобразователей дополнительного кода в прямой, управляют работой которых знаковые разряды регистров 4 и 5. С выходов первого 6 и вто1)ого 7 преобразователей дополнительного кода в прямой операнды чисел поступают на входы блока 8 сравнения и информационные входы

0

5

0

5

0

5

коммутатора 9. Блок 8 сравнения определяет какое из чисел больн е, и своим выходным сигналом управляет работой коммутатора 9. Коммутатор 9 построен так, что на его первом выходе появляется операнд, соответствующий болыпему числу (xi), а на втором выходе - операнд, соответствуюш,ий меньшему числу (У|). С первого и второго выходов коммутатора 9 операнды чисел Х и у поступают на информационные входа первого 11 и второго 12 сдвигателей соответственно. Одновременно т старших разрядов числа А | поступают на вход приоритетного шифратора 10, на выходе которого образуется двоичный параллельный код номера старшего значащего разряда числа Xi, который управляет величиной сдвига первого 11 и второго 2 сдвигателей. С выходов первого 10 и второго 11 сдвигателей /(-разрядные операнды чисел а и 6 поступают на входы соответственно первого 13 и второго 14 логарифмических преобразователей, с выходов которых операнды чисел а и Ь поступают соответственно на входы уменьшаемого и вычитаемого вычитателя 15.

Количество т старших разрядов числа л |, поступающих на вход приоритетного н ифратора 10, выбираются из соотношения - К.

Приоритетный шифратор 10 совместно с первым двигателем 11 производит сдвиг так, чтобы на выходе первого сдвигателя 11 старшая значан1ая цифра числа а находилась в старшем разряде.

С выхода вычитателя 15 операнд числа с поступает на входы косинусного 16 и арктан- генсного 17 преобразователей, которые производят преобразование информации в соответствии с функциональными зависимостями

Q

COS arctg2

45 arctg2

0

5

0

5

соответственно. Операнд а с выхода косинусного преобразователя 16 поступает на вход второго сомножите;|я умножителя 18, на вход первого сомножителя которого поступает операнд числа л ; с выхода ко.ммута- тора 9. С выхода умножителя 18 результат вычисления функции поступает на выход 21 модуля вектора устройства. С выходов знаков первого 1 и второго 2 регистров знаковые разряды чисел поступают соответственно на первый и второй входы блока 19 памяти смещения угла, на третий адресный вход которого поступает сигнал с выхода блока 8 сравнения. С выхода арк- тангенсного преобразователя 17 операнд числа 45 поступает на вход первого операнда сумматора-вычитателя 20, на входы второго операнда и выбора операции которого поступает информация с первого и второго выходов блока 19. С выхода сумматора- вычитателя 20 результат вычисления функции (f aTcigy/x поступает на выход 22 аргумента вектора устройства.

Формула изобретения Устройство для вычисления модуля и аргумента вектора, содержащее коммутатор, первый сдвигатель, умножитель, вычитатель и блок па1мяти смещения угла, причем выход больщего числа коммутатора соединен с входом первого сомножителя умножителя, отличающееся тем, что, с целью повышения точности вычисления, в него дополнительно введены первый и второй регистры, первый и второй преобразователи дополнительного кода в прямой, блок сравнения, приоритетный и ифратор, второй .сдвигатель, первый и второй логарифмические преобразователи, арктангенсный преобразователь, косинусный преобразователь и сумматор-вычитатель, причем входы первого и второго значений операндов устройства соединены с информационными входами соответственно первого и второго регистров, синхронизирующие входы которых соединены с тактовым входом устройства, выходы разрядов, кроме старших, первого и второго регистров соединены с информационными входами соответственно первого и второго преобразователей дополнительного кода в прямой, управляющие входы которых соединены с выходами старших разрядов соответственно первого и второго регистров, выходы первого и второго преобразователей дополнительного кода в прямой соединены соответственно с первым и вторым информационными входами коммутатора и с первым и вторым входами блока

0

0

5

сравнения, выход которого соединен с управляющим входом коммутатора, первый выход которого соединен с информационным входом первого сдвигателя и входом приоритетного шифратора, второй выход коммутатора соединен с информационным входом второго сдвигателя, входы управления- величиной сдви1 а первого и второго сдвигателей соединен с выходом приоритетного шифратора, выходы первого и второго сдвигателеГ соединены с входами аргументов соответственно первого и второго логарифмического преобразователей, выходы которых соединены с входами соответственно уменьи|аемого и вычитаемого вычитателя, выход которого соединен с входами аргументов арктангенс- ного и косинусного преобразователей, выход косинусного преобразователя соединен с входом второго сомножителя умножителя, выход которого является выходом модуля вектора устройства, выход арктангенсного преобразователя соединен с входом первого операнда сумматора-вычитателя, выход которого является выходом аргумента вектора устройства, вход второго операнда и вход выборки операции сумматора-вычитателя соединены соответственно с первым и вторым выходами блока памяти смешения yr,ia, выходы старших разрядов первого и второго регистров и выход блока сравнения соединены с входами разрядов первой, второй и третьей групп адресного входа блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Устройство для вычисления функции арктангенса отношения | 1988 |

|

SU1615709A1 |

| Устройство для вычисления функции @ | 1985 |

|

SU1305671A1 |

| Устройство для вычисления корня @ -степени | 1986 |

|

SU1381494A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Вычислительное устройство | 1989 |

|

SU1691837A1 |

Изобретение может быть при.менено для вычисления модуля и аргумента выхода в специализированных вычислителях для нахождения амплитудных и фазовых составляющих сигнала в процессорах цифровой обработки сигнала. Целью изобретения является повышение точности вычислений. Устройство содержит вход I первого и вход 2 второго аргументов, тактовый вход 3, первый 4 и второй 5 регистры, первый 6 и второй 7 преобразователи дополнительного кода в прямой, блок 8 сравнения, коммутатор 9, приоритетный шифратор 10, первый П и второй 12 сдвигатели, первый 13 и второй 14 логарифмические преобразователи, вычи- татель 15, косинусный преобразователь 16, арктангенсный преобразователь 17, умножитель 18, блок 19 памяти смещения yr. ia, сум.матор-вычитатель 20, выход 21 .моду:1я вектора, выход 22 аргу.мента вектора. I ил.

| Устройство для вычисления функций @ | 1980 |

|

SU957207A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функций | 1978 |

|

SU824207A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-15—Публикация

1986-10-17—Подача