&wdt

Фиг.1

10

15

11425823

Изобретение относится к импульсной технике и может быть использовано в системах.автоматического управления, следящих электроприводах и в системах синхронизации генераторов.

Цель изобретения - повьшение надежности детектирования синхронных сигналов.

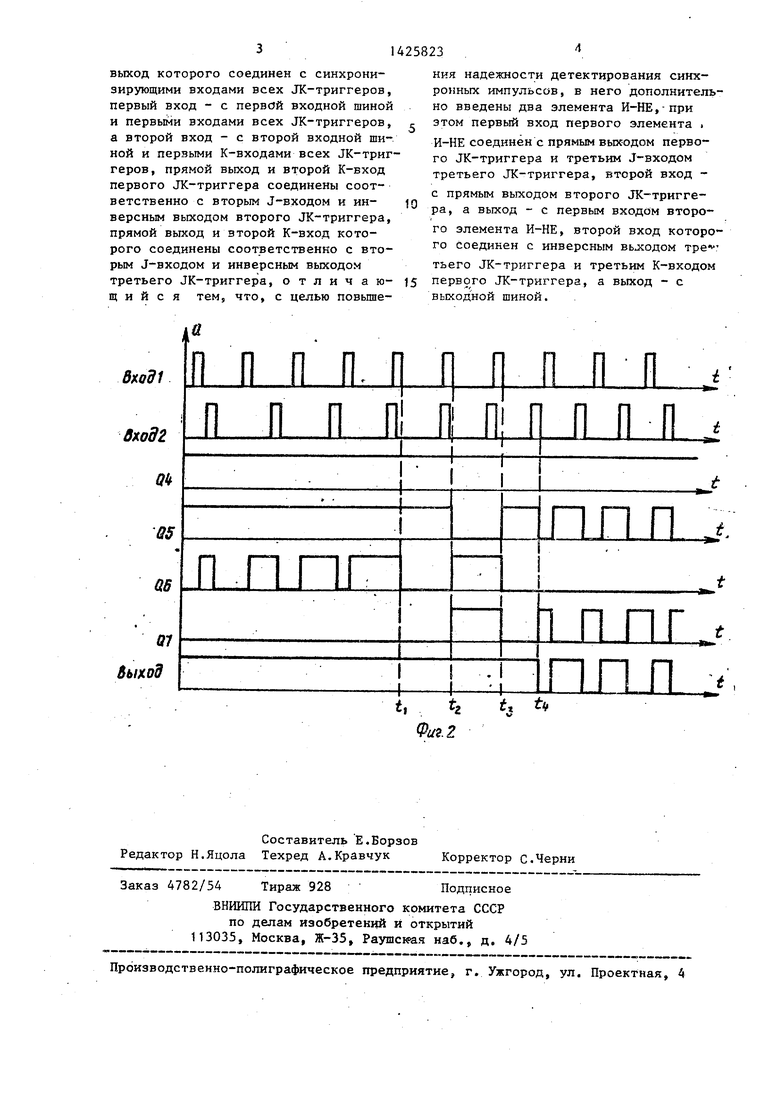

На фиг.1 приведена функциональная схема импульсно-фазового детектора; на фиг.2 - временные диаграммы его работы.

Импульсно-фазовый детектор содержит элемент ИЛИ 1, JK-триггеры 2-4 и элементы И-НЕ 5 и 6, при этом первая входная шина соединена с первым входом элемента ИЛИ 1 и первыми J-входами триггеров 2-4, вторая входная шина соединена с вторым входом элемента ИЛИ 1 и первыми К-входами триггеров 2-4, синхронизирующие входы которых соединены с выходом элемента ИЛИ 1, прямой выход триггера 2 соединен с вторыми J-входами триггеров 3 и 4 и первым входом элемента И-НЕ 5, второй вход которого соединен с прямым вькодом триггера 3 и третьим J-входом триггера 4, а выход - С:первым входом элемента И-НЕ 6, второй вход которого соединен с инверсным выходом триггера 4 и вторыми К-входами триггеров 2 и 3, выход - с выходной шиной, а инверсный выход триггера 3-е третьим К-входом триггера 2.

Импульсно-фазовый детектор работает следующим образом.

20

25

30

п н к о х в 45 а н м с п в х О

35

Пусть, например, частота импульсов на первой входной шине Вх1 постоянна, а на второй входной шине Вх.2 постепенно увеличивается, но в начальный момент вр емени меньше частоты сигналов на первой входной шине, (фиг.2). В некоторый момент времени t фазовое рассогласование уменьшается до наложения импульсов на входах элемента ИЛИ 1 друг на друга во времени (t,,t,t5).

что эквивалентно синхронному следованию импульсов . Начиная с момента времени t триггеры 3 и 4 начинают в противо- фазе изменять свои состояния, а триггер 2 все время находится в единичном состоянии, так как для .того чтобы он перешел в нулевое состояние необходимо, чтобы оба триггера 3 и 4 находились в нулевых состояниях, а

0

5

0

5

0

это возможно лишь при рассогласованном поступлении импульсов на входы детектора, когда триггер 4 постоянно находится в нулевом состоянии, а триггер 3 изменяет свои состояния . при поочередном поступлении импульсов на входные шины, т.е. когда триггер 3 находится в фазовом режиме.

Изменение частотного соотношения поступающих на входы детектора импульсов сопровождается обязательньш переходом триггера 3 в фазовый режим, так первый же одиночный импульс, поступающий на вход Вх.2 после пар синхронных импульсов (момент времени t) и свидетельствующий о том, что период импульсов на входе Вх.2 стал меньше периода импульсов на входе Вх.1, переводит оба триггера 3 и 4- в нулевое состояние. Триггер 3 переходит в фазовый режим.

Таким образом, введение двух логических элементов И-НЕ исключает образование меандра на выходе детектора в момент поступления синхронных импульсов, так как подключение элемента И-НЕ к выходам триггеров 2 и 3 исключает образование меандра на его выходе при противофазном изменении состояний этих триггеров, а подключение второго элемента И-НЕ к выходу первого элемента И-НЕ и инверсному выходу триггера 4 исключает образование меандра на выходе второго элемента И-НЕ при противофазном изменении СОСТО.ЯНИЙ триггеров 3 и 4, так как выходной сигнал первого элемента И-НЕ при введении дополнительньк связях между триггерами в это время соответствует сигналу на инверсном выходе триггера 3. При этом сигнал на выходе второго элемента И-НЕ находится в соответствии с разницей частот,- 5 а при равенстве частот и фазовом рассогласовании - в соответствии с состоянием триггера 3, т.е. с выходным сигналом детектора. Исключение меандра из выходного сигнала детектора при поступлении на его вход синхронных импульсов в свою очередь повьш1ает надежность работы устройства, так как при этом исключаются выходные сигналы, соответствующие фазовому сдвигу, в действительности ОТЦ1ХТС твующему. Формула изобретения

Импульсно-фазовый детектор, содер - жащий три JK-триггера и элемент ИЛИ,

5

0

0

5

выход которого соединен с синхронизирующими входами всех JK-триггеров, первый вход - с первой входной шиной и первыми входами всех JK-триггеров, а второй вход - с второй входной шиной и первыми К-входами всех JK-триггеров, прямой выход и второй К-вход первого JK-триггера соединены соответственно с вторым J-входом и инверсным выходом второго JK-триггера, прямой выход и второй К-вход которого соединены соот ветственно с вторым J-входом и инверсным выходом третьего JK-триггера, отличающийся тем, что, с целью повьше

ния надежности детектирования синхронных импульсов, в него дополнительно введены два элемента И-НЕ,-при этом первый вход первого элемента . И-НЕ соединён с прямым выходом первого JK-триггера и третьим J-входом третьего JK-триггера, второй вход с прямым выходом второго JK-триггера, а выход - с первым входом второго элемента И-НЕ, второй вход которо го соединен с инверсным вьлодом тьего JK TpHrrepa и третьим К-входом первого JK-триггера, а выход - с выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| Синхронный делитель частоты на 9 на JK-триггерах | 1987 |

|

SU1444938A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Управляемый делитель частоты | 1987 |

|

SU1522396A1 |

| Многофазный генератор ступенчато-треугольных функций | 1984 |

|

SU1246347A2 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Цифровой фазометр мгновенных значений | 1988 |

|

SU1553920A1 |

Изобретение относится к импульсной технике и может быть использовано в системах автоматического управления, следящих электроприводах и системах синхронизации генератора. Изобретение повышает надежность детектирования синхронных сигналов. Устройство содержит элемент ИЛИ I, JK-триггеры 2,3 и 4, элементы И-НЕ 5 и 6. Введение двух логических элементов И-НЕ исключает образование меандра на выходе детектора в момент поступления синхроимпульсов. Исключение меандра из выходного сигнала детектора при поступлении на его вход синхронных импульсов повышает надежность работы устройства, так как при этом исключаются выходные сигналы, соответствующие фазовому сдвигу, 2 ил. (Л

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 0 |

|

SU379049A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Импульсно-фазовый детектор | 1975 |

|

SU678661A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-23—Публикация

1986-12-10—Подача