0ue. f

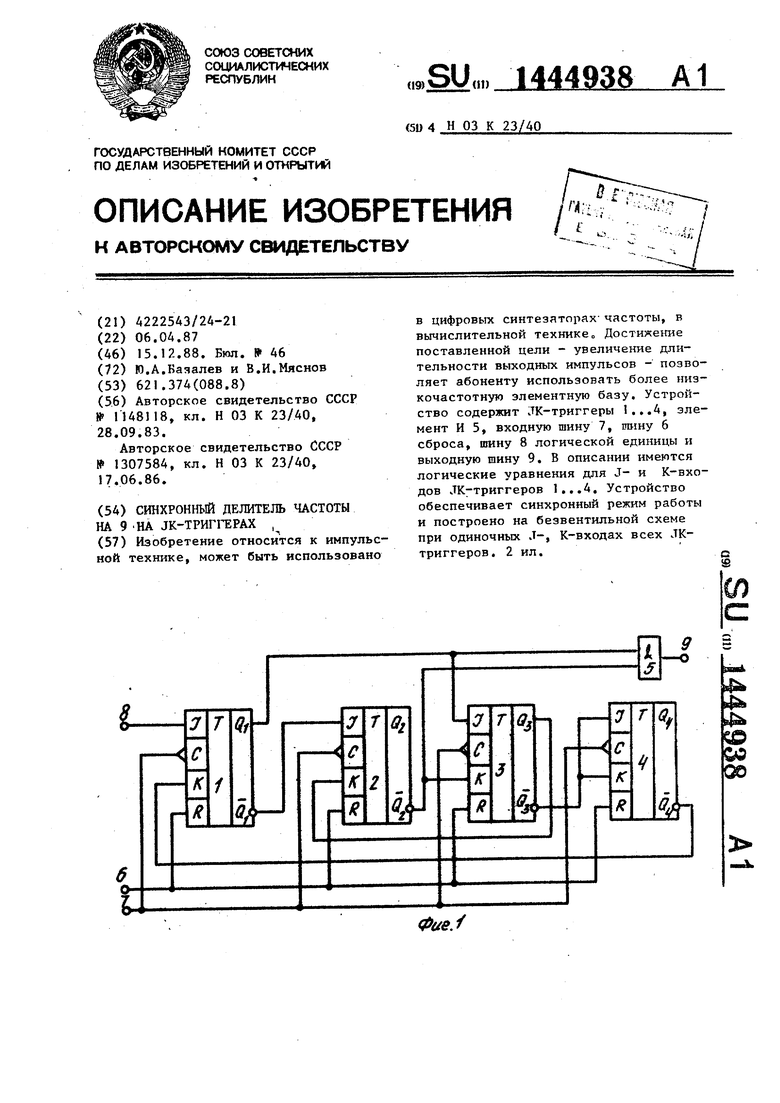

Изобретение относится к импульсной технике и может быть использовано в цифровой аппаратуре, например, в цифровых синтезаторах частоты.

Цель изобретения - увеличение длительности выходных импульсов, что позволяет абоненту использовать более низкочастотную элементную базу.

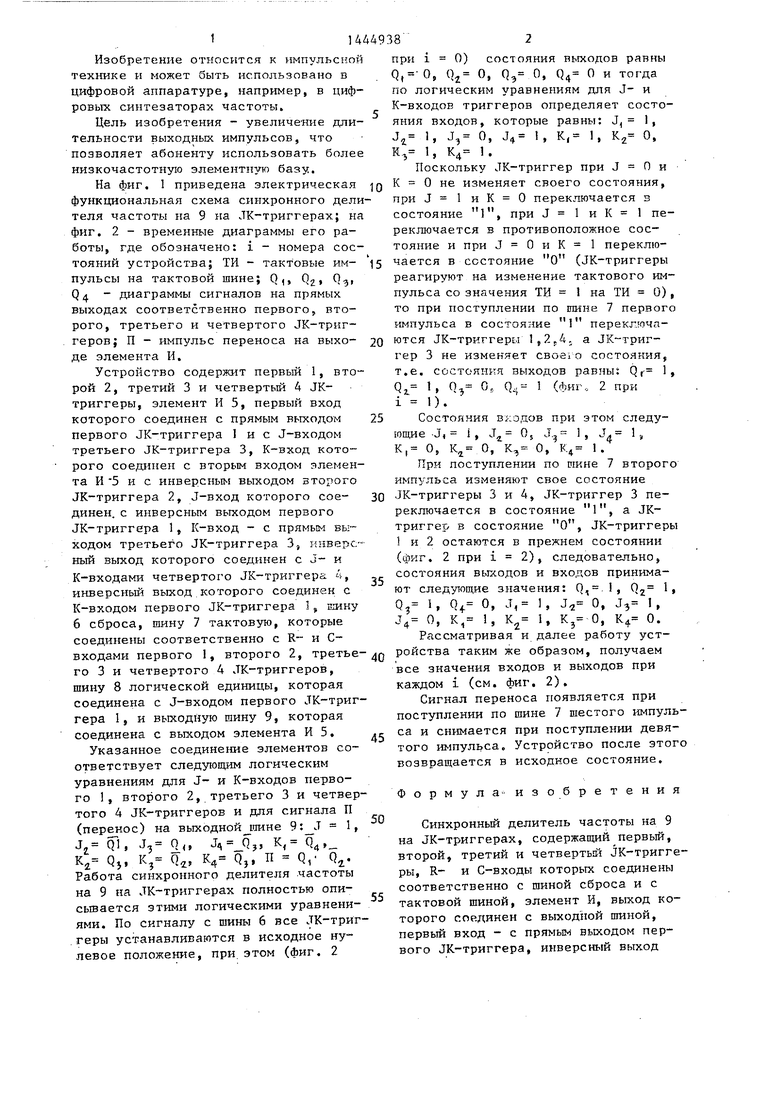

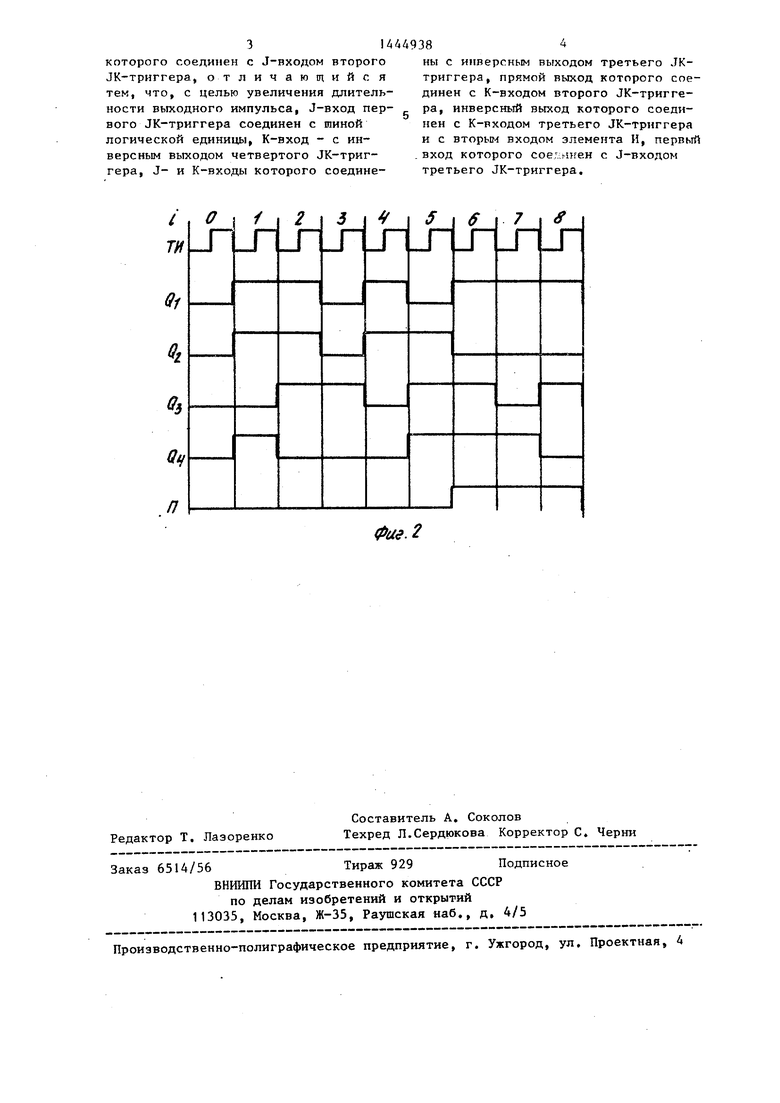

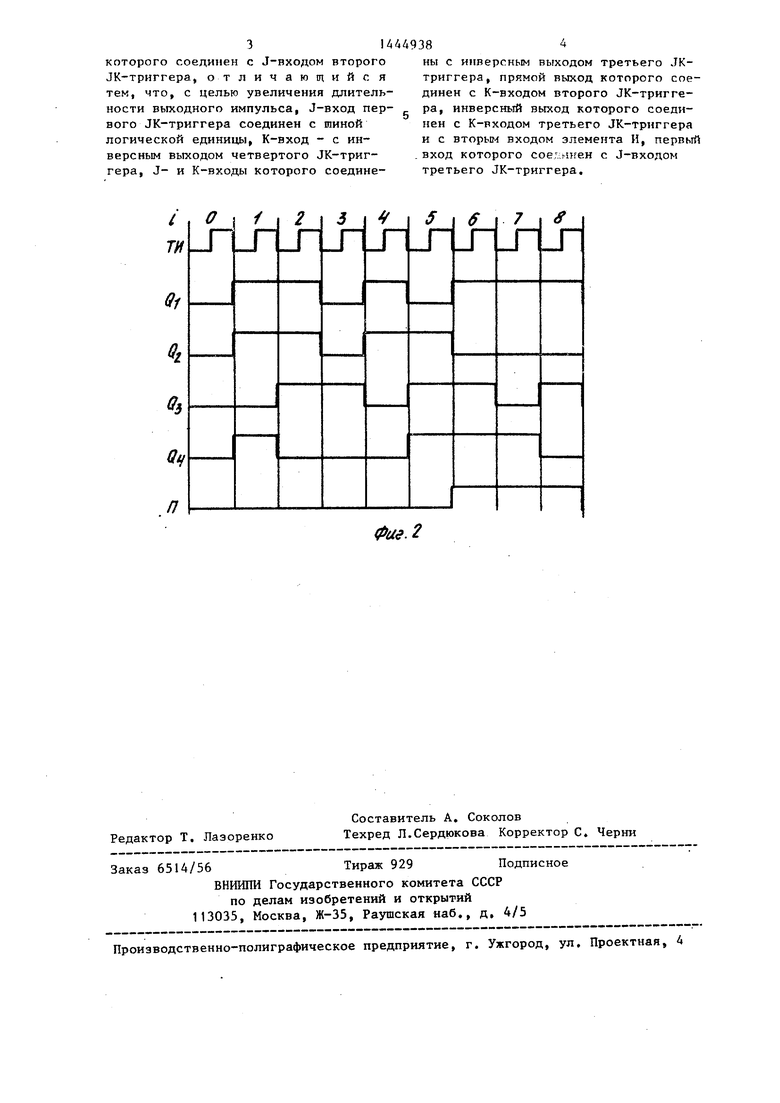

На фиг. 1 приведена электрическая функциональная схема синхронного дели теля частоты на 9 на ЛК-триггерах; на фиг. 2 - временные диаграммы его работы, где обозначено: i - номера состояний устройства; ТИ - тактовые импульсы на тактовой шине; Q,, Q, 0, Q 4 диаграммы сигналов на прямых выходах соответственно первого,, второго, третьего и четвертого JK-триг- геров; П - импульс переноса на выходе элемента И.

Устройство содержит первый 1, второй 2, третий 3 и четвертый 4 JK- триггеры, элемент И 5, первый вход которого соединен с прямым выходом первого JK-триггера 1 и с J-входом третьего JK-триггера 3, К-вход которого соединен с вторым входом элемента И 5 и с инверсным выходом второго JK-триггера 2, J-вход которого соединен, с инверсным выходом первого JK-триггвра 1, К-вход - с прямым выходом третьего JK-триггера 3, инверсный выход которого соединен с J- и К-входами четвертого JK-триггера Д, инверсный выход которого соединен с К-входом первого JK-триггера 1, шину 6 сброса, шину 7 тактовую, которые соединены соответственно с R- и С- входами первого 1, второго 2, третьего 3 и четвертого 4 JK-триггеров, шину 8 логической единицы, которая соединена с J-входом первого JK-триггера 1, и выходную шину 9, которая соединена с выходом элемента И 5.

Указанное соединение элементов соответствует следуюпщм логическим уравнениям для J- и К-входов первого , второго 2, третьего 3 и четвертого 4 JK-триггеров и для сигнала П (перенос) на выходной гчине 1,

, Q1, J, Qo

,i К, Q,

K.j Qj, K, Q,,, K Qj, П Q, Q,. Работа синхронного делителя частоты на 9 на JK-триггерах полностью опи- сьшается этими логическими уравнениями. По сигналу с шины 6 все JK-триТ- геры устанавливаются в исходное нулевое положение, при. этом (фиг. 2

0

5

0

5

0

5

D

5

при ) состояния выходов равны Q,-0, 0 О, Q, О, Q4 О и тогда по логическим уравнениям для J- и К-входов триггеров определяет состояния входов, которые равны: J, 1, Jj 1, J, О, J 1, К, 1, К2 О, К 1, К4 1.

Поскольку JK-триггер при J П и К О не изменяет своего состояния, при J 1 и К О переключается в состояние 1, при J 1 и К 1 переключается в противоположное состояние и при J О и К 1 переключается в состояние О (JK-триггеры реагируют на изменение тактового импульса со значения ТИ 1 на ТИ 0), то при поступлении по шине 7 первого импульса в состояние I переключаются JK-триггеры а JK-триггер 3 не изменяет состояния, т.е. cocтoян я выходов равны: Qr- 1, Q- 1, 0 О,, Q,,- 1 (фиг. 2 при ).

Состояния в :одов при этом следующие -J, i, J GS J. 1, J. 1, K, 0, K, 0, K, 0, K 1.

При поступлении по шине 7 второго импульса изменяют свое состояние JK-триггеры 3 и 4, JK-триггер 3 переключается в состояние 1, а JK- триггер в состояние О, JK-триггеры 1 и 2 остаются в прежнем состоянии (фкг. 2 при ), следовательно, состояния выходов и входов принимают следующие значения: Q, , Q2 1 Q 1, Q О, J, 1, J 0, J, 1, J 0, K, 1, K,, 1, K, 0, K4 0.

Рассматривая и далее работу устройства таким же образом, получаем все значения входов и выходов при каждом 1 (см. фиг. 2),

Сигнал переноса появляется при поступлении по шине 7 шестого импульса и снимается при поступлении девятого импульса. Устройство после этого возвращается в исходное состояние.

Формула изобрете

н и я

Синхронный делитель частоты на 9 на JK-триггерах, содержащий первый, второй, третий и четвертый JK-тригге- ры, R- и С-входы которых соединены соответственно с шиной сброса и с тактовой шиной, элемент И, выход которого соединен с выходной шиной, первый вход - с прямым выходом первого JK-триггера, инверсный выход

31Д/4

которого соединен с J-входом второго JK-триггера, отличающий с я тем, что, с целью увеличения длительности выходного импульса, J-вход первого JK-триггера соединен с шиной логической единицы, К-вход - с инверсным выходом четвертого JK-триггера, J- и К-входы которого соедине49384

ны с инверсным выходом третьего JK- триггера, прямой выход которого соединен с К-входом второго JK-триггера, инверсный выход которого соединен с К-Рходом третьего JK-трнггера и с вторым входом элемента И, первый .вход которого соединен с J-входом третьего JK-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Синхронный делитель частоты | 1986 |

|

SU1385291A1 |

| Реверсивная счетная декада | 1988 |

|

SU1554141A1 |

| Синхронный делитель частоты на 16 | 1984 |

|

SU1225010A1 |

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Синхронный делитель частоты на 14 | 1985 |

|

SU1243130A1 |

| Синхронный делитель на 12 | 1987 |

|

SU1517129A1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Синхронный делитель частоты | 1986 |

|

SU1374425A1 |

Изобретение относится к импульсной технике, может быть использовано в цифровых синтезаторах- частоты, в вычислительной технике о Достижение поставленной цели - увеличение длительности выходных импульсов - позволяет абоненту использовать более низкочастотную элементную базу. Устройство содержит JK-триггеры 1...4, элемент И 5, входную шину 7, тину 6 сброса, шину 8 логической единицы и выходную шину 9. В описании имеются логические уравнения для J- и К-вхо- дов ЛК-триггеров 1...4. Устройство обеспечивает синхронный режим работы и построено на безвентильной схеме при одиночных Л-, К-входах всех ЛК- триггеров. 2 ил. с

01

1

G5

QH

П

«f

Фие.

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1985 |

|

SU1307584A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-06—Подача