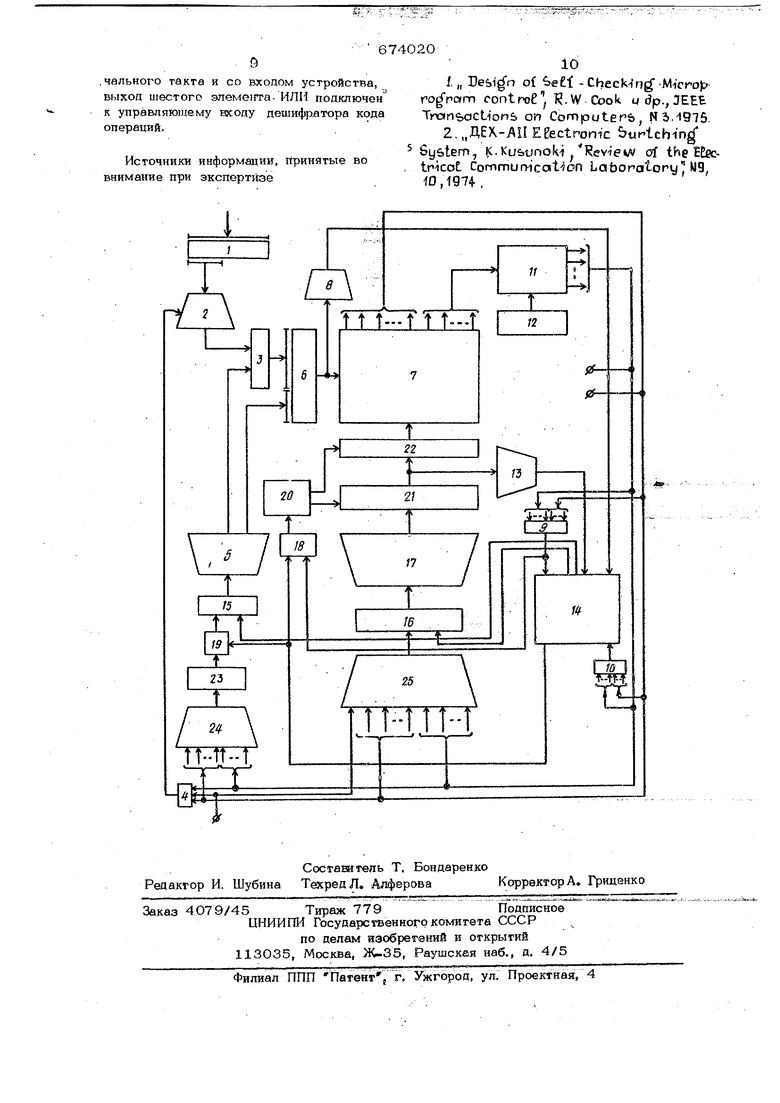

Из6бретеШ1ё относится к области вычислительной техшЕки и может бкррь использовано для управления ЭВМ с аппаратной реализацией. Известно устройство упрайленкя ЭВМ fl , содержащее Т1 ограммную и микро программную память, лог я даскуго ,;схему ветвления, управляющие триггеры регист и деши4ратор адреса микрокоманды, регистр микрокоманд, дешифратор номера исходного регистра, вьвсоды которого под ключен1э1 к выходным коммутаторам ЭВМ и к табличному дешифратору оперший, дешифратор номера конечного регистра, подключенный к входным коммутаторам , ЭВМ и к табличному деши4рат6ру Ций, подключен1а)му к арифметическому устройству ЭВМ. Это устройство обладает недостаточ ным быстродействием и требует больших затрат оборудования на его реализацию. Наиболее близким техническим решением к предложенному является известное устройство 2 ..содержащее регистр коман выход которого соедив Ж с информационным входом дешифратора кода операций, блок зфанения управпяклцих сигналов, блок хранения дополнительных управляющих сигналов, регистр условий, выход которого подключен к управляющему входу блока зфанешгя дополнительных управЛ5пощих сигналов, информационныйвзвод которого соединен с первь1М выходом блока хранения управляющих сигналов, генератор тактовых импульсов, первый выход которого подключен к управляющему регистра тактов, деши Ьратор тактов, ши4|{}атор микропрограмм: , Однако, недостатком этого.устройства является его громоздкость за счет того, что в блоке хранения управляющих сигналов (матр1ше управляющих сигналов табличном логическом дешифраторе) каждая команда (горизонталь матрицы) содержит набор элементов И.для всех своих микрокоманд (отсутств от микроподпрог- раммы|ГПри изменении команды и особенно при создании .макрокоманды требуется добавление 1говых элементов И и увеличение выходов дешифратора тактов. Целью предлагаемого устройства управления является сокращение объема обо- рудоветия. Поставленная достигается тем, /что Ъ устройство введены регистр oifepaций имикрЬподпрограмм, безад1эесная память дешифратор, шифратор такта, шифратор, регистр, коммутатор, блок счробирЬвания, шесть элементов ИЛИ, управляющий триг гер, шифратор начального такта, причем в.ькод дешифратора кода операций соеди-, иен с первым входом первого элемента ИЛИ, второй вход которого соединен с первым выходом дешифратора, второй выход Которого соединен о первым входом регистра операций и микроПодпроГрамм, второй вход которого Соединен с выходом первого элемента ИЛИ, выход регистра операций и мшсррпбдпрограмм соединен с пер вым входом блока хранения управляющих сигаалов, входом шифратора, вьрсод которого соединен с пертым информационным вх дом беаащ)есной памяти, BiTopoft информац оннъй вход которой подключен к 1выходу шифратора -raKfa, вход которого : соединен с информационным входом блока с робкро;вйния и с выходом регистра тактов, информационный вход которого соединен с вьгходом дешифратора тактов, вход которо го Шедийен с выходом второго элемента ИЛИ, первый вход которого соединен с информационным вькрдрм безадресной пакетти, второй информационный выход которой соединен з первьий входом третьего элемента ИЛИ, выход которого подключен ко входу дешифратора, второй вход второго элемента ИЛИ .соёдйЯён с выходом ши4ратора начального такта, вто рой вход третьего элемента, соединек с выходом коммутатора, информационный вход которого соединен с выходом регистра, управлякяций вход коммутатора соединен соуправляющим выходом безадресной Г сё|сйШШе1м входом равляющего фштера, выход которого под ключен ко входугенератора тактовых шмпупьсов, второй выход которого подключе к управляющему входу блока с.тробировагяия, вьпсод которогх) подключён ко втором Bxofljy блока хранения управляющих сигналов, второй выход кОторого,.подключен к первому выходу устройства, первым входам четвёртого и пятого элементов ИЛИ, nepBiuM входам шифратора начального, так та и шифратора мйкроподпрограмм, первому входу шестого элемента ИЛИ, второй вход которого соединен со вторьгм входом шифратора микроподпрограмм, вторым входом шифратора начального такта, вторыми вх.ода11 и четвертого и пятого элементов ИЛИ, вторым выходом устройства и с выходом блока хранения дополнительньк управляю- ших сигналов, выход четвертого элемента ИЛИ подключен к нулевому входу управляющего триггера, первому управляющему входу безадресной памяти, второй управляющий вход которой соединен с выходом пятого элемента ИЛИ, выход ши(|ратора микроподпрограмм соединен со входом регистра, третий вход шестого элемента ИЛИ соединен: с управляющим входом шифратора начального такта и со входом устройства, вькйдщестого элемента ИЛИ прдклйчен к управляющему входу Дешифратора коДа операций. . На чертеже представлена блок-схемй устройства управления электронной вычислительной маши1юй. Устройство содержит регистр команд 1, дешифратор 2 кода операций 2, первый и шестой элементы ИЛИ 3, 4, дешифратор 5, р1эгистр 6 операций и микропОдпрограмм, блок храненш 7 управляющих сиг. налов, шифратор 8, четвертый и пятый элементы ИЛИ 9, IQ блок хранения 11 дополнительных управляющих сигналов, регистр 12 условий, шифратор такта 13, безадресную память 1,, третий и второй элемента ИЛИ 15, 16, деши4ратор тактов 17, триггер управлшия 18, коммутатор 19, генератор 20 тактовых импульсов, регистр тактов 21, блок стробировакия 22, регистр 23, микроподпрограмм 24, щи4чратор 25 начального такпра. УсчройствО работает следующим образом, . . В кеходйбмеостояяий всё регистры устройс ва управления ЭВМ установлекьг на нуль. Генератор 20 тактовых импугаэсов вырабатьшает тактовые импульсы, поступают на регистр тактов 21 :и блок стробирования 22. Так как в регистре тактов 21, вшолнёнйом как регистр сдвига, нет , то состояние его не меняется. На блок хранещся 7 управляющихТсигнайОв поступают нули со всех разрядов регистра 6 и блока стробирования 22, так что блок хранения 7упраа :ляющйх Сигналов не вьграбГатывает никаких управлякхцих сигналов. При запуске устройства управления ЭВМ с пульта управления в регистр ко манд 1 Эаписывается начальная команда. Через шифратор 25 начального такта, второй элемент ИЛИ 16 и дешифратор тактов 17 записывается 1- -в старший разряд регистра тактов 21 и через шестой элемент ИЛИ 4 дается сигнал раз-, решения на дешифратор кода операций 2. Расшифрованкый код операций в виде ко да 1 из п через первый элемент ИЛИ 3 поступает на один иэ триггеров регнстра 6 операций и микроподпрограмм, и возбуждает (подает логическую I) соот- ветствукхцую входную горизонталь блока хранения 7 управляющих сигналов. От Генератора 2О тактовых импульсов на блок стробирования 22 поступает стробируюший сигнал, по которому элемент И блока стробирования пропускают сигнал логиче стой 1 на соответствующую входную вер тикаль блока хранения 7 управляющих сигналов (возбуждение вертикали) . Элв мент совйадения, находящийся на переевчении возбужденной горизонтали и вертикали блока хранения 7 управляющих сигналЫз, вырабатьюает сигнал логической I являющийся выходным сигналом блока 7, Как правило, элементы совпадения блока 7, относящиеся к рагрвдам операапи ре- гистра 6 (к разрядам, идущим через элемент ИЛИ 3) не вьшопнязот когжретйых микрокоманд, а обращаются к той или иной микроподпрограмие (формирование. адресов, чтение и записи в память и т.п.) Обращение к микроподпрограмме происходит 3 следующей последоватейьносэи: запись в безадресную память 14 через вшф раторы 8 и 13 номеров текущей возбужденной) вертикали и горизонтали, запись начального такта в регистр тактов 21 через шифратор 25, эпемейт ИЛИ16 и дещи4 тор тактов 17, щапись номера ми роподпрограммы в регистр 6 через шифра тор микроподпрограмм 24, регистр 23, коммутатор 19, элемент ИЛИ 15 и дешифратор 5. Тот же сигнал с выхода блока 7 поступает на вход элемента ИЛИ 9, с выхода которого возбуждается сигнал протолкнуть в безадресной памяти 14, по KOTOpoTviy вся информация в безадресной памяти (магазинной памяти т., .. последний вошел, первый вышел) пер&Местится из регистра в регистр вглубь безадресной памяти и в первый головной ее регистр запишет с-шифраторов 8 и 13 номера текущей горизонтали и в тикали блока 7. Так как запись в головной регввстр безадресной памяти 14 следует с замедлением (сначала переписывается информа-

674020 ция в глубинных ее регистрах), это в регистре 21 передаинется и на выходе шифратора 13 будет уже номер следующей вертикали блока 7. Параллельно с началом. записи номеров вертикали и горизонтали блока 7 в безадресную память 14 выход блока 7 запишет через шифратор 25, эл&мент ИЛИ 16 и дешифратор 17 в регистр 21 начальный номер вертикали, с которой должна начаться микроподпрограмма чеpea 24 в регистр 23 - номер горизонтали, на которой размещается вызьгоаемая микроподпрограмма и через триггер 18 блокирует работу генератора 2О. Сигнал конец записи с управляющего выхода безадресной памяти деблокирует гвнератор 2О и через коммутатор 19 перепшпет М«горизонтали в регистр6. Споступлением тактового импупьса от генератора 2О элементы И блока стробирования 22 пропускают логическую 1 с регистра 21 на вертикаль блока 7, так что срабатьюает схема совпадетгия, находящаяся на пересечении возбужденной горизонтали и вертикали, вьфабатьюая выходной управляющий сигнал блока 7, который прямо или через.блок 11 хранения дополяительных уггравляюшйх сигналов поступает на выходы устройства. Такт генератора 2О продвинет .Д. в., регистре тактов 21 8 следующийразряд так, что в следующий момент возбуждения элементов И блока стробирования 22 будет вьщан следующий управляющий сигнал микроподпрограк&л и. т. д. МиЕроподпраграмд лы могут использоваться рекурсивно, . переходить к сл дующей ми фойодпрограммё до своего окончания. При этом информация о номеpax вертикалей и горизонталей предшествукяцих операций и мшфоподпрограмм будет записьтаться из регистра в регистр в глубину безадресной памяти 14. После окончания всех мизфокомавд в микроподпрограмме последняя микрокоманда микроподпрограммы через элемент ИЛИ 10 обратится к безадрес ной памяти 14 с командой вытолкнуть. При этом информация, находящаяся в первом регистре памяти 14 (номера вертикали и горизонтали предьщущей операции или макрокомандьО поступает с информационных выходов безадресной памяти через элементы ИЛИ 16 и 15, дешифраторы 17 и 5 на регист ры 21 и 6, восстанавливая то состояние блока 7, какое было в момент обращения к мик1юподпрограмме. При этом вся иНтформация в регистрах безадресной памяти 14 продвинется из глубины к первоWty регистру на ОДИН регистре Сигнал возбуждения элементов И блока строби- 22 от генератора 2О вькзовет спедующую микрокоманду операции (или обращение и следующей микропрограмме) и т.д. до последней микрокоманды, опёра ции или никрсГкомакды, Котор1я череэ элемент ИЛИ 4 даст разрешение на деши4ратор 2 на дешифрацто и запись в регистр 6 ко да новой следующей операции команды, наход$аце йся к этому времени в регистре команд 1. Одновременно с этим поспедняя микрокоманда предьщущей операции установит через шифратор 25, элемент ИЛИ 16 и дешифратор 17 единицу в первый разряд регистра тактов 21. С при ходом такта стробировашш от генератора 2О будет выполняться, у7ке микрокоманда следующей операции, и таким образом выполняться программа, закодированная соединениями выходов блоков 11 со входами элементов ИЛИ 9, 1О, 4 и шифраторов 24 и 25. Предлагаемое устройство управления ЭВМ вЫгЬдно отличается от протот1ша, так как позволяет экономить оборудование эвмГ Формула изобретения Усчройство управления электронной вычислительной машиной, Йодёр кащёе регйстр к6манд которого соединен с инфорМашюнмым входом дешифратора кода oneраций, блок гфанейия управлшбших сигналов, блок Хр(аяеиия дополнитёльйьк управляющих сигналов, регистр условий, выход кЬт&ротЧ) подключен к управП51ющему входу блока хранения дополнительных управяяющих сигналов, информационный вход которого соединен с первым выходом блока храненщ управпшощих сигналов, тактовых импульсов, первый вь1Ход которого поякяючен и равляющему входу гистра тшстов, тактов, шифратор мйЕроподпрограмм, о т Я и ч а ю - . щ е е с я тем, что с цепью сокрахйения объема оборудования, в устройство введе- ны регистр операций и мййрОпйдпрограмм безадресная память, дешифратор, шифратор такта, шифратор, регистр, крлшутатор блок стробировашя, шесть элементов ИЛИ управляющий триггер, шифратор начального такта, причем вьпсод дешифратора кода операций ГёоЩййён с пфвьййЁхШом перво го элемента ИЛИ, второй вход которого соединен с первым вькодом дешифратора. второй выход которого соединен с первым входом регистра операций и микроподпрограмм, второй вход которого соединен с выходом первого элемента ИЛИ, вьосод регистра операций и микроподпрограмм соединен с первым входом блока хранения управляющих сигналов, входом шифратора, выход которого соединен с первым информационньпи входом безадресной памяти, второй информационный вход которой подключен к выходу шифратора такта, вход которого соединен с информационным входом блока стробирования и с выходом регистра тактов, информационный вход которого соединен с выходом дешифратора тактов, вход которого coefljmeH с выходом второго элемента ИЛИ, пqэвый вход которого соединен с первым информационным выходом безадресной памяти, второй информационный выход которой соединен 9, первым входом третьего элемента ИЛИ, выход которого подключен ко входу дешифратора, второй вход второго элемента ИЛИ соединен с вьрсодом шифрато Р начального такта, второй вход третьего элемента ИЛИ соединен с выходом коммутатора, информационный вход которого соединен с выходом регистра, управляющий вход коммутатора соединен с уцравлякицим выходом безадресной памяти не единичным входом управляющего триггера, выход которого подключен ко входу генератора такговых импульсов, второй выход которого подключен к управляющему щоду блока стробировайия, вьссод хотороро яойключеи ко второму входу блока хранения управляющих сигналов второй выход которого подключен к первому выходу устройства, первым входам четвертого и пятого элементов .ИЛИ, первым входам шифратора начального такта и шифратора микропог программ, первому в;;соду шестого элемента ИЛИ, второй вход Которого соединен со вторым входом шифратора микропод.программ, бторым входом шифратора начального такта, вторыми входами четъер- того /и пятого элементов ИЛИ, вторым выходом устройства и с выходом блока хранения допопнитеяьных управлякяцих еиг налов, выход четвертого элемента ИЛИ подключен к нулевому входу управляющего триггера,, первому управляющему вкоду безадресной памяти, второй управляющий вход которой соединен с выходом пятого элемента ИЛИ, выход шифратора микроподпрограмм соединен со входом регистра, третий Вход шестого элемента ИЛИ соедг кен с 511равляюшим входом ши4$)атора на-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807290A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935959A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1716512A1 |

| Устройство для задания режимов работы цифровой вычислительной машины и индикации ее состояния | 1979 |

|

SU873240A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

Авторы

Даты

1979-07-15—Публикация

1977-03-28—Подача