Изобретение относится к автоматике и технике связи и может использоваться в системах передачи сигналов (например, речевых).

Цель изобретения - повышение функциональной надежности и достоверности преобразования.

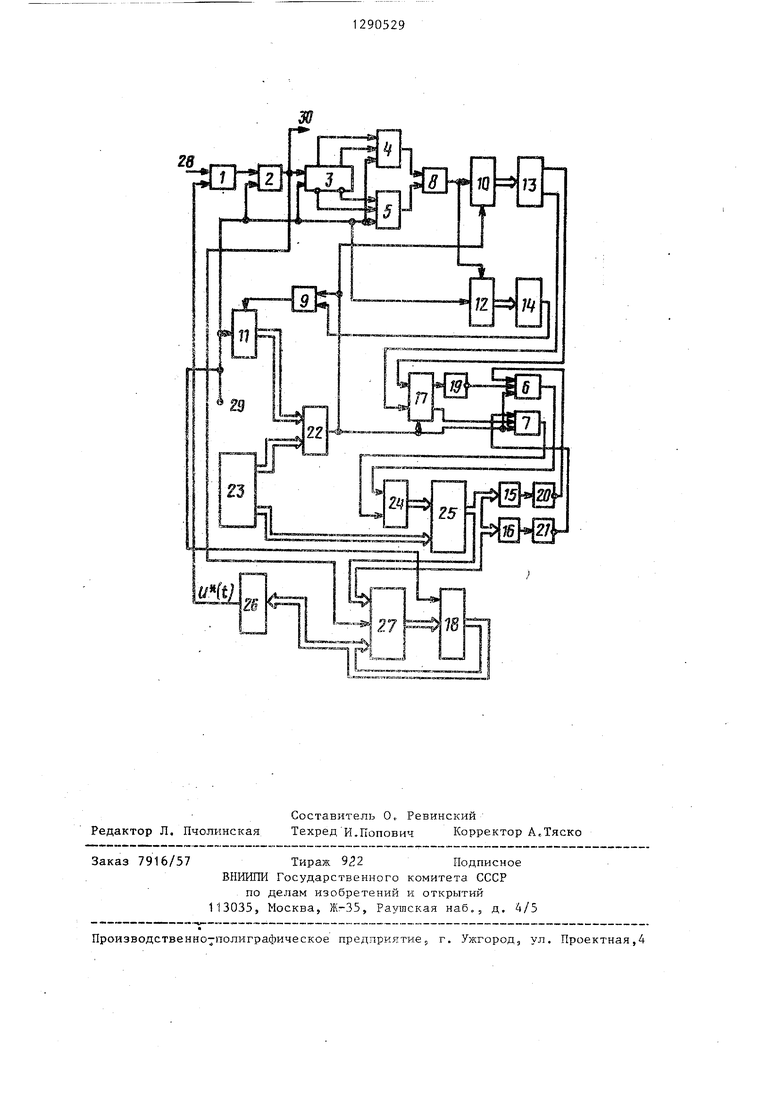

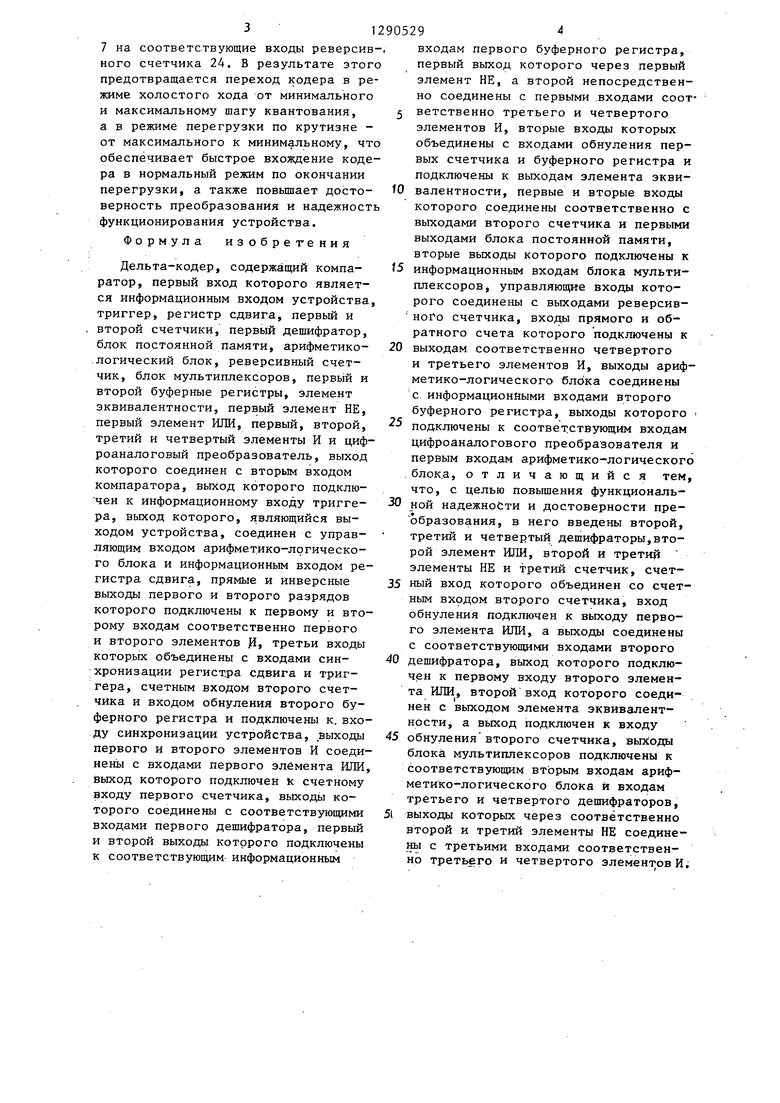

На чертеже изображена функциональная схема устройства.

Дельта-кодер содержит компаратор 1, триггер 2, регистр 3 сдвига,первый 4, второй 5, третий 6 и четвертый 7 элементы И, первый 8 и второй 9 элементы ИЛИ, первый 10, второй 11 и третий 12 счетчики, первый 13, второй 14, третий 15 и четвертый. 16 дешифраторы, первый 17 и второй 18 буферные регистры, первый 19, второй 20 и третий 21 элементы .НЕ,элемент 22 эквивалентности, блок 23 постоянной памяти,реверсивный счетчик 24, блок 25 мультиплексоров, цифроаналоговый преобразователь (ЦАП 26, арифметико-логический блок 27, информационШ)1й вход 28, вход 29 синхронизации и выход 30.

Устройство работает следующим образом.

Аналоговый сигнал, поступающий на информационный вход 28 устройства, сравнивается в компараторе 1 с аппроксиммирующим сигналом с ЦАП 26. Полученная цифровая последовательность дискретизируется в три- гере 2 сигналом синхронизации с входа 29 и поступает на вход 30 устройства, а также в регистр 3 сдвига Сигналы с выходов регистра 3 анализируются элементами И 4 и 5, РШИ 8, первым счетчиком 10 и первым дешифратором 13. Одновременно второй счетчик 1-1, подсчитывает синхроимпульсы с входа 29. Результат подсчета сравнивается на элементе 22 эквивалентности с числом из блока 23 постоянной памяти, соответствующим некоторому заранее заданному интервалу Т . анализа. По истечении каждого интервала Т. счетчики 10 и 11 обнуляются. Если при этом за вре мя Т . в выходном сигнале дельта-кодера число сдвоенных символов (единиц или нулей) не превысило некоторого числа N,|flj;,H то на выходах первог дешифратора 13 сигналы отсутствуют, если это число больше некоторого числа М„„„„ , то сигналы присутст

вуют

макс

на обоих

выходах дешифра5

0

5

0 5

0

5

0

5

тора 13. Когда число сдвоенных символов находится между N и N. сигнал имеется лишь на первом выходе; дешифратора 13. С интервалом Тд сигналы с дешифратора 13 записываются в первый буферный регистр 17, причем сигнал с его первого выхода инвертируется элементом НЕ 19. В конце каждого интервала Т открываются элементы И 6 и 7 .и пропускают соответствующие сигналы на входы реверсивного счетчика 24. В результате, если сдвоенных символов меньше , содержимое реверсивного счетчика 24 уменьшается на единицу, а если сдвоенных символов больше N. - увеличивается. Сигналы с реверсивного счетчика 24 при помощи блока 25 мультиплексоров управляют подключением на арифметико-логический блок 27 с блока 23 постоянной памяти сигналов, соответствующих требуемому (большему или меньшему) шагу квантования. Арифметико-логический блок 27 в сочетании со вторым буферным регистром 18 и ЦАП 26 представляет блок восстановления аппроксимирующего напряжения.

Третий счет чик 12 ведет подсчет синхроимпульсов с входа 29, при этом наличие в выходном сигнале дельта-кодера сдвоенных импульсов вызывает обнуление этого счетчика 12. .Таким образам счетчик 12 подсчитывает число синхроимпульсов в паузах входного сигнала и при достижении некоторого числа, выбранного с учетом того, что в сигнале холостого хода дельта-кодера практически отсутствуют шумы свободного канала,второй дешифратор 14,вьщает сигнал,который через второй элемент ИЛИ 9 обнуляет второй счетчик 11. Так как это происходит одновременно в кодере и декодере, то по окончании паузы второй счетчик 11 кодера и аналогичный счетчик декодера работают синхронно, благодаря чему повьш1ает- ся функциональная надежность и достоверность преобразования.

Третий и четвертый дешифраторы 15 и 16 фиксируют состояния реверсивного счетчика 24, соответствующие минимальному и максимальному шагу квантования. Сигналы с этих дешифраторов после инвертирования на элементах НЕ 20 и 21 запрещают прохождение сигналов через элементы И 6 и

7 на соответствующие входы реверсив ного счетчика 24. В результате этог предотвращается переход кодера в режиме холостого хода от минимального и максимальному шагу квантования, а в режиме перегрузки по крутизне - от максимального к минимальному, чт обеспечивает быстрое вхождение кодера в нормальный режим по окончании перегрузки, а также повьшает досто- верность преобразования и надежност функционирования устройства.

Формула изобретения

Дельта-кодер, содержащий компа- ратор, первый вход которого является информационным входом устройства триггер, регистр сдвига, первый и второй счетчики, первый дешифратор, блок постоянной памяти, арифметико- .логический блок, реверсивный счетчик, блок мультиплексоров, первый и второй буферные регистры, элемент эквивалентности, первый элемент НЕ, первый элемент ИЛИ, первый, второй, третий и четвертый элементы И и циф- роаналоговый преобразователь, выход которого соединен с вторьм входом компаратора, выход которого подклю- чен к информационному входу тригге- ра, выход которого, являющийся выходом устройства, соединен с управ- ляющим входом арифметико-логического блока и информационным входом регистра сдвига, прямые и инверсные выходы первого и второго разрядов которого подключены к первому и второму входам соответственно первого и второго элементов Д, третьи входы которых объединены с входами син- хронизации регистра сдвига и триггера, счетным входом второго счетчика и входом обнуления второго буферного регистра и подключены к. входу синхронизации устройства, выходы первого и второго элементов И соеди- нень с входами первого элемента ИЛИ выход которого подключен k счетному входу первого счетчика, выходы которого соединены с соответствующими входами первого дешифратора, первый и второй выходы которого подключены к соответствующим- информационньм

входам первого буферного регистра, первый выход которого через первый элемент НЕ, а второй непосредственно соединены с первыми входами соответственно третьего и четвертого элементов И, вторые входы которых объединены с входами обнуления первых счетчика и буферного регистра и подключены к выходам элемента эквивалентности, первые и вторые входы которого соединены соответственно с вьгходами второго счетчика и первыми выходами блока постоянной памяти, вторые выходы которого подключены к информационным входам блока мультиплексоров, управляющие входы которого соединены с выходами реверсив ноГо счетчика, входы прямого и обратного счета которого подключены к выходам соответственно четвертого и третьего элементов И, выходы арифметико-логического блока соединены с информационными входами второго буферного регистра, выходы которого подключены к соответствующим входам цифроаналогового преобразователя и первым входам арифметико-логическог

. блок.а, отличающийся тем что, с целью повышения функциональной надежности и достоверности пре- образования, в него введены второй, третий и четвертый дешифраторы,второй элемент ИЛИ, второй и третий элементы НЕ и третий счетчик, счетный вход которого объединен со счетным вхрдом второго счетчика, вход обнуления подключен к выходу первого элемента ИЛИ, а выходы соединены с соответствующими входами второго дешифратора, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом элемента эквивалентности а выход подключен к входу обнуления второго счетчика, выходы блока мультиплексоров подключены к соответствующим вторым входам арифметико-логического блока и входам третьего и четвертого дешифраторов, выходы которых через соответственно второй и третий элементы НЕ соединены с третьими входами соответственно третьего и четвертого элементов И

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Устройство связи с дельта-модуляцией | 1986 |

|

SU1365364A1 |

| Устройство для обработки данных | 1987 |

|

SU1536396A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для регистрации информации | 1984 |

|

SU1234858A1 |

Изобретение относится к автоматике и технике связи. Его использование в системах передачи позволяет повысить.функциональную надежность и достоверность преобразования. Дельта-кодер содержит компаратор, триггер, регистр сдвига, четыре элемента И, злемент ИЛИ, элемент НЕ,два счетчика, дешифратор, два буферных регистра, элемент эквивалентности, блок постоянной памяти, реверсивный счетчик, блок мультиплексоров, циф- роаналоговый преобразователь и арифметико-логический блок. Вв еденйе дополнительно счетчика,элемента ИЛИ, .двух дешифраторов и двух элемен- : тов НЕ обеспечивает блокировку ре- версивного счетчика в крайних состояниях, а также возможность допол-: нительной синхронизации передаваемого сигнала. 1 ил. а (Л to со о ел ю QD

Составитель 0„ Ревинский Редактор Л, Пчолкнская Техред И.Попович Корректор А.Тяско

7916/57

Тираж 9 2Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

11роизводственно7полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| Патент США № 3835385, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-15—Публикация

1985-04-11—Подача