Изобретение относится к запоминающим устройствам и может быть использовано в линиях задержки цифровой информации.

Цель изобретения является повьше- 5 ние достовернсгсти функционирования устройства.

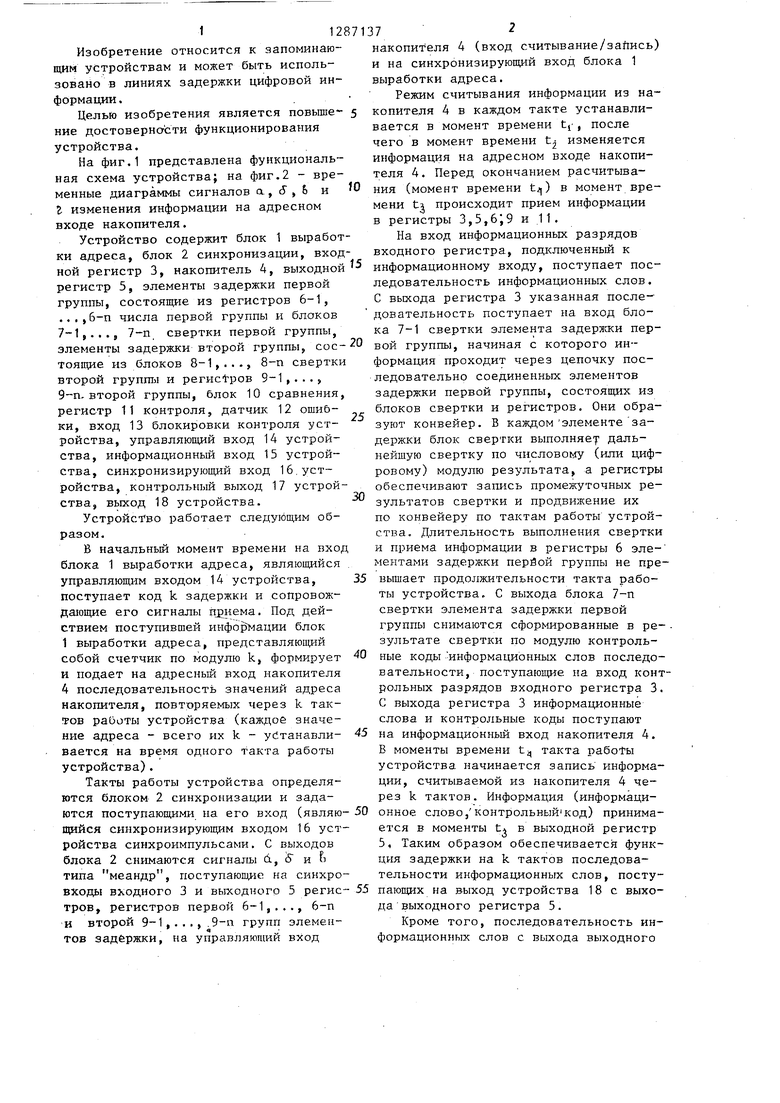

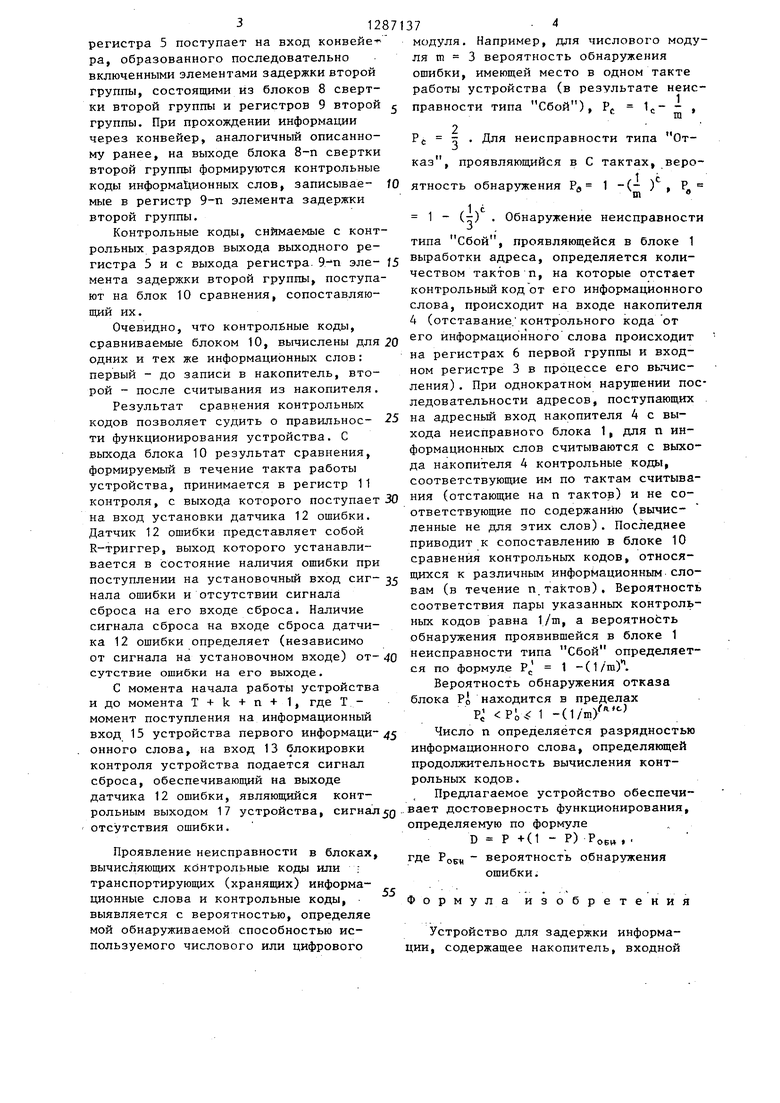

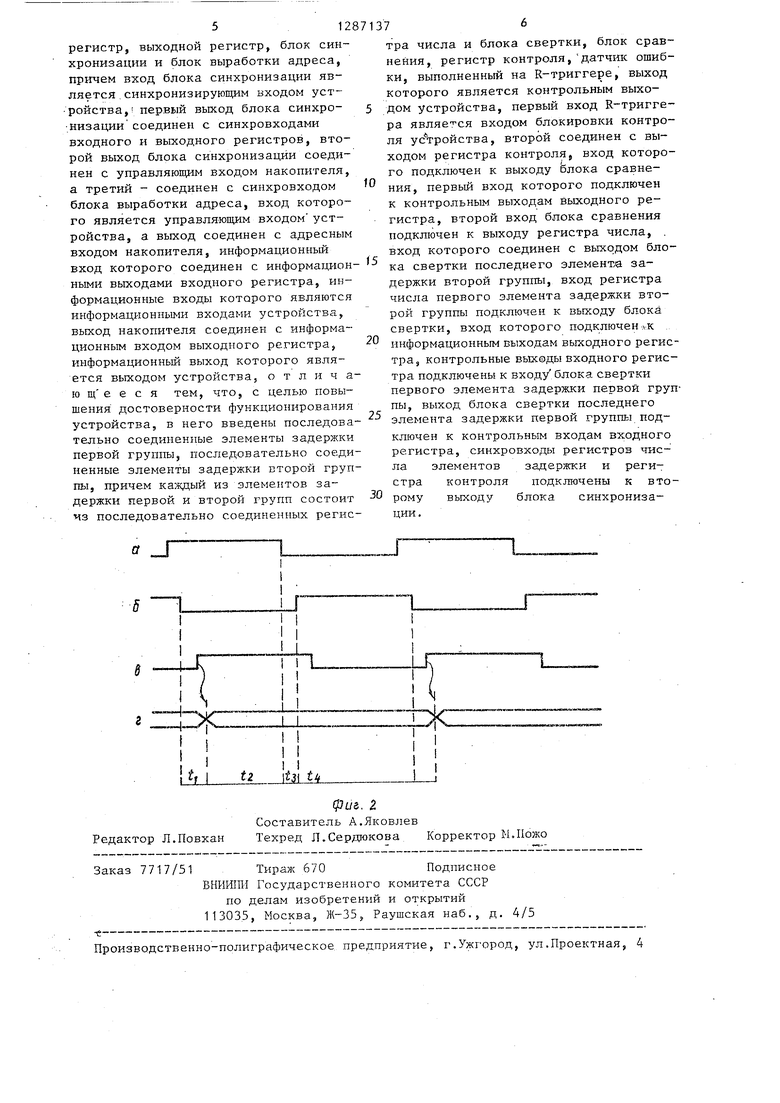

На фиг.1 представлена функциональная схема устройства; на фиг.2 - временные диаграммы сигналов а, сЗ , 6 и Ч изменения информации на адресном входе накопителя.

Устройство содержит блок 1 выработки адреса, блок 2 синхронизации, вход

fO

накопителя 4 (вход считывание/зайись) и на синхронизирующий вход блока 1 выработки адреса.

Режим считывания информации из накопителя 4 в каждом такте устанавливается в момент времени , после чего в момент времени t изменяется информация на адресном входе накопителя 4. Перед окончанием расчитыва- ния (момент времени tjj) в момент времени tj происходит прием информации в регистры 3,5,6,9 и 11.

На вход информационных разрядов входного регистра, подключенный к

ной регистр 3, накопитель 4, выходной информационному входу, поступает пос- регистр 5, элементы задержки первой ледовательность информационных слов, группы, состоящие из регистров 6-1, ...,б-п числа первой группы и блоков 7-1,..., 7-п свертки первой группы.

элементы задержки второй группы, сое

-20

С выхода регистра 3 указанная последовательность поступает на вход блока 7-1 свертки элемента задержки первой группы, начиная с которого информация проходит через цепочку последовательно соединенных элементов задержки первой группы, состоящих из блоков свертки и регистров. Они образуют конвейер. В каждом элементе задержки блок свертки выполняем дальнейшую свертку по числовому (или цифровому) модулю результата, а регистры обеспе швают запись промежуточных результатов свертки и продвижение их по конвейеру по тактам работы устройства. Длительность выполнения свертки и приема информации в регистры 6 элементами задержки перйой группы не превышает продолжительности такта работы устройства. С выхода блока 7-п свертки элемента задержки первой группы снимаются сформированные в результате свертки по модулю контрольные коды -информационных слов последовательности, поступающие на вход конт рольных разрядов входного регистра 3. С выхода регистра 3 информационные слова и контрольные коды поступают

тояпще из блоков 8-1,..., 8-п свертк второй групш:. и peгиctpoв 9-1,..., . второй группы, блок 10 сравнения регистр 11 контроля, датчик 12 ошибки, вход 13 блокировки контроля устройства, управляющий вход 14 устройства, информационньм вход 15 устройства, синхронизирующий вход 16,устройства, контрольный выход 17 устройства, вьгход 18 устройства.Устройство работает следующим образом.

В начальный момент времени на вхо блока 1 выработки адреса, являющийся управляющим входом 14 устройства, поступает код k задержки и сопровождающие его сигналы приема. Под действием поступившей блок 1 выработки адреса, представляюпщй собой счетчик по модулю k, формирует и подает на адресный вход накопителя 4 последовательность значений адреса накопителя, повторяемых через k тактов работы устройства (каждое значеС выхода регистра 3 указанная последовательность поступает на вход блока 7-1 свертки элемента задержки первой группы, начиная с которого информация проходит через цепочку последовательно соединенных элементов задержки первой группы, состоящих из блоков свертки и регистров. Они образуют конвейер. В каждом элементе задержки блок свертки выполняем дальнейшую свертку по числовому (или цифровому) модулю результата, а регистры обеспе швают запись промежуточных результатов свертки и продвижение их по конвейеру по тактам работы устройства. Длительность выполнения свертки и приема информации в регистры 6 элементами задержки перйой группы не пре вышает продолжительности такта работы устройства. С выхода блока 7-п свертки элемента задержки первой группы снимаются сформированные в результате свертки по модулю контрольные коды -информационных слов последовательности, поступающие на вход конт рольных разрядов входного регистра 3 С выхода регистра 3 информационные слова и контрольные коды поступают

ние адреса - всего их k - уСтанавли- 45 на информационный вход накопителя 4.

вается на время одного такта работы устройства).

Такты работы устройства определяются блоком 2 синхронизации и задаются поступающими на его вход (являю-50 онное слово, контрольный код) принимащийся синхронизирующим входом 16 устройства синхроимпульсами. С выходов блока 2 снимаются сигналы й-, S и f)

ется в моменты t. в выходной регистр 5, Таким образом обеспечивается функция задержки на k тактов последова- типа меандр, поступающ 1е на синхро- тельности информационных слов, посту- входы входного 3 и выходного 5 регис- 55 пающих на выход устройства 18 с выхо- тров, регистров первой 6-1,..., 6-п да выходного регистра 5. к второй 9-1,...,.9-п групп элемен- Кроме того, последовательность ин- тов задержки, на управляющий вХод формационных слов с выхода выходного

накопителя 4 (вход считывание/зайись) и на синхронизирующий вход блока 1 выработки адреса.

Режим считывания информации из накопителя 4 в каждом такте устанавливается в момент времени , после чего в момент времени t изменяется информация на адресном входе накопителя 4. Перед окончанием расчитыва- ния (момент времени tjj) в момент времени tj происходит прием информации в регистры 3,5,6,9 и 11.

На вход информационных разрядов входного регистра, подключенный к

информационному входу, поступает пос- ледовательность информационных слов,

информационному входу, поступает пос- ледовательность информационных слов,

0

5

50

С выхода регистра 3 указанная последовательность поступает на вход блока 7-1 свертки элемента задержки первой группы, начиная с которого информация проходит через цепочку последовательно соединенных элементов задержки первой группы, состоящих из блоков свертки и регистров. Они образуют конвейер. В каждом элементе задержки блок свертки выполняем дальнейшую свертку по числовому (или цифровому) модулю результата, а регистры обеспе швают запись промежуточных результатов свертки и продвижение их по конвейеру по тактам работы устройства. Длительность выполнения свертки и приема информации в регистры 6 эле ментами задержки перйой группы не превышает продолжительности такта работы устройства. С выхода блока 7-п свертки элемента задержки первой группы снимаются сформированные в ре. зультате свертки по модулю контрольные коды -информационных слов последовательности, поступающие на вход контрольных разрядов входного регистра 3. С выхода регистра 3 информационные слова и контрольные коды поступают

В моменты времени tj, такта работы устройства начинается запись информации, считываемой из накопителя 4 через k тактов. Информация (информацирегистра 5 поступает на вход конвейет ра, образованного последовательно включенными элементами задержки второй группы, состоящими из блоков 8 свертмодуля. Например, для числового модуля m 3 вероятность обнаружения ошибки, имеющей место в одном такте работы устройства (в результате неиски второй группы и регистров 9 второй правности типа Сбой), Р - , группы. При прохождении информации

через конвейер, аналогичный описанно- р , д неисправности типа 0т- му ранее, на выходе блока 8-п свертки второй группь формируются контрольные коды информа1;ионных слов, записывае- fO мне в регистр 9-т1 элемента задержки второй группы.

Контрольные коды, снимаемые с контрольных разрядов выхода выходного ре

m

Р -

PC - 3

каз, проявляющийся в С тактах, веро1 ш

ятность обнаружения Р, 1 -(- ) , Р

1 - (|)

Обнаружение неисправности типа Сбой, проявляющейся в блоке 1

гистра 5 и с выхода регистра. 9-п эле- 15 выработки адреса, определяется коли- мента задержки второй группы, поступа- чеством тактов п, на которые отстает ют на блок 10 сравнения, сопоставляю- контрольный код от его информационного щий их.слова, происходит на входе накопителя

Очевидно, что контрольные коды, (отставание; контрольного кода от сравниваемые блоком 10, вычислены для 20 ° информационного слова происходит

одних и тех же информационных слов: первый - до записи в накопитель, второй - после считывания из накопителя.

Результат сравнения контрольных кодов позволяет судить о правильности функционирования устройства. С выхода блока 10 результат сравнения, формируемый в течение такта работы устройства, принимается в регистр 11

на регистрах 6 первой группы и входном регистре 3 в процессе его вычисления) . При однократном нарушении последовательности адресов, поступающих 25 на адресный вход накопителя 4 с выхода неисправного блока 1, для п информационных слов считываются с выхода накопителя 4 контрольные коды, соответствующие им по тактам считываконтроля, с выхода которого поступает 30 ния (отстающие на п тактов) и не со- на вход установки датчика 12 ошибки. ответствующие по содержанию (вычис- Датчик 12 ошибки представляет собой ленные не для этих слов). Последнее R-триггер, выход которого устанавли- приводит к сопоставлению в блоке 10 вается в состояние наличия ошибки при сравнения контрольных кодов, относя- поступлении на установочный вход сиг-35 различным информационным, сло- нала ошибки и отсутствии сигнала сброса на его входе сброса. Наличие сигнала сброса на входе сброса датчика 12 ошибки определяет (независимо от сигнала на установочном входе) от-40 неисправности типа Сбой определяет- сутствие ошибки на его выходе.ся по формуле Р 1 -(1/т).

С момента начала работы устройства Вероятность обнаружения отказа и до момента Т + k + п + 1, где Т - блока Р находится в пределах момент поступления на информационныйPC Po-J 1 -(1/m)

вход 15 устройства первого информаци- 5 онного слова, на вход 13 блокировки контроля устройства подается сигнал сброса, обеспечивающий на выходе

вам (в течение п.тактов), Вероятность соответствия пары указанных контрольных кодов равна l/m, а вероятность обнаружения проявившейся в блоке 1

с о

Число п определяется разрядностью информационного слова, определяющей продолжительность вычисления контрольных кодов.

Предлагаемое устройство обеспечиР +(1 - Р) Р

OBW

датчика 12 ошибки, являющийся конт

рольным выходом 17 устройства, сигнал50 достоверность функционирования,

отсутствия ошибки. определяемую по формуле

D Проявление неисправности в блоках,

вычисляющих контрольные коды или ; транспортирующих (хранящих) информационные слова и контрольные коды, . выявляется с вероятностью, определяе мой обнаруживаемой способностью используемого числового или цифрового

где РОР„ - вероятность обнаружения ошибки.

55

Формула из

обретения

Устройство для задержки информации, содержащее накопитель, входной

модуля. Например, для числового модуля m 3 вероятность обнаружения ошибки, имеющей место в одном такте работы устройства (в результате неисправности типа Сбой), Р - ,

р , д неисправности типа 0т-

m

Р -

PC - 3

каз, проявляющийся в С тактах, веро1 ш

ятность обнаружения Р, 1 -(- ) , Р

р , д неисправности типа 0т-

1 - (|)

Обнаружение неисправности типа Сбой, проявляющейся в блоке 1

ния (отстающие на п тактов) и не со- ответствующие по содержанию (вычис- ленные не для этих слов). Последнее приводит к сопоставлению в блоке 10 сравнения контрольных кодов, относя- различным информационным, сло- неисправности типа Сбой определяет- ся по формуле Р 1 -(1/т).

вам (в течение п.тактов), Вероятность соответствия пары указанных контрольных кодов равна l/m, а вероятность обнаружения проявившейся в блоке 1

Вероятность обнаружения отказа блока Р находится в пределах PC Po-J 1 -(1/m)

с о

Число п определяется разрядностью информационного слова, определяющей продолжительность вычисления контрольных кодов.

Предлагаемое устройство обеспечиР +(1 - Р) Р

OBW

по формуле

D

где РОР„ - вероятность обнаружения ошибки.

55

Формула из

обретения

Устройство для задержки информации, содержащее накопитель, входной

регистр, выходной регистр, блок синхронизации и блок выработки адреса, вход блока синхронизации является . синхронизирующим входом уст- ройства, первый выход блока синхро- низации соединен с синхровходами входного и выходного регистров, второй выход блока синхронизации соединен с управляющим входом накопителя, а третий - соединен с синхровходом блока выработки адреса, вход которого является управляющим входом устройства, а выход соединен с адресным входом накопителя, информационный вход которого соединен с информацион ными выходами входного регистра, информационные входы которого являются информационными входами устройства, выход накопителя соединен с информационным входом выходного регистра, информационный выход которого является выходом устройства, о т л и ч а- ю щ е е с я тем, что, с целью повышения достоверности функционирования устройства, в него введены последовательно соединенные элементы задержки первой группы, последовательно соединенные элементы задержки второй группы, причем каждый из элементов задержки первой и второй групп состоит 43 последовательно соединенных регис-

Ю

15

20

25

30

тра числа и блока свертки, блок сравнения, регистр контроля, датчик ошибки, выполненный на R-триггере, выход которого является контрольным выходом устройства, первый вход R-тригге- ра является входом блокировки контроля устройства, второй соединен с выходом регистра контроля, вход которого подключен к выходу Ьлока сравнения, первый вход которого подключен к контрольным выходам выходного регистра, второй вход блока сравнения подключен к выходу регистра числа, . вход которого соединен с выходом блока свертки последнего элемента задержки второй группы, вход регистра числа первого элемента задержки второй группы подключен к вькоду блока свертки, вход которого подключенак - информационным выходам выходного регистра, контрольные выходы входного регистра подключены к входу блока свертки первого элемента задержки первой группы, выход блока свертки последнего элемента задержки первой группы подключен к контрольным входам входного регистра, синхровходы регистров числа элементов задержки и регистра контроля подключены к второму выходу блока синхронизации .

а

Редактор Л.Повхан

Фий. г

Составитель А.Яковлев

Техред Л.Сердгокова Корректор М.Пожо

Заказ 7717/51 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Устройство для задержки цифровой информации с контролем | 1987 |

|

SU1462424A1 |

| Устройство цифровой задержки информации с контролем | 1988 |

|

SU1635225A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1211811A1 |

| Устройство для контроля схем управления | 1984 |

|

SU1252785A1 |

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в линиях задержки цифровой информации. Целью изобретения является повьшение достоверности функционирования устройства. Поставленная цель достигается тем, что в устройство введены блоки свертки 7,8 соответственно первой и второй групп, регистры 6 первой группы, регистры 9 второй группы, блок 10 сравнения, регистр 11 контроля, датчик 12 ошибки, что позволяет повысить достоверность функционирования. Выигрыш в достоверности определяется величиной (1-P) P,g||, где Р - вероятность безотказной работы, POSH - вероятность обнаружения ошибок. Выигрыш достигнут одновременно с поддержанием высокой производительности устройства путем вычисления контрольных кодов информационных слов в течение п тактов работы устройства. 2 ил. (Л to 00 со фиг.1

| Запоминающее устройство | 1975 |

|

SU556495A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для программируемой задержки информации | 1984 |

|

SU1193653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-03-22—Подача