Изобретение относится к вычисли- тельной технике и может быть использовано при построении запоминающих устройств с высокой достоверностью выдаваемой информаттии.

Цель изобретения повьшение быстродействия устройства.

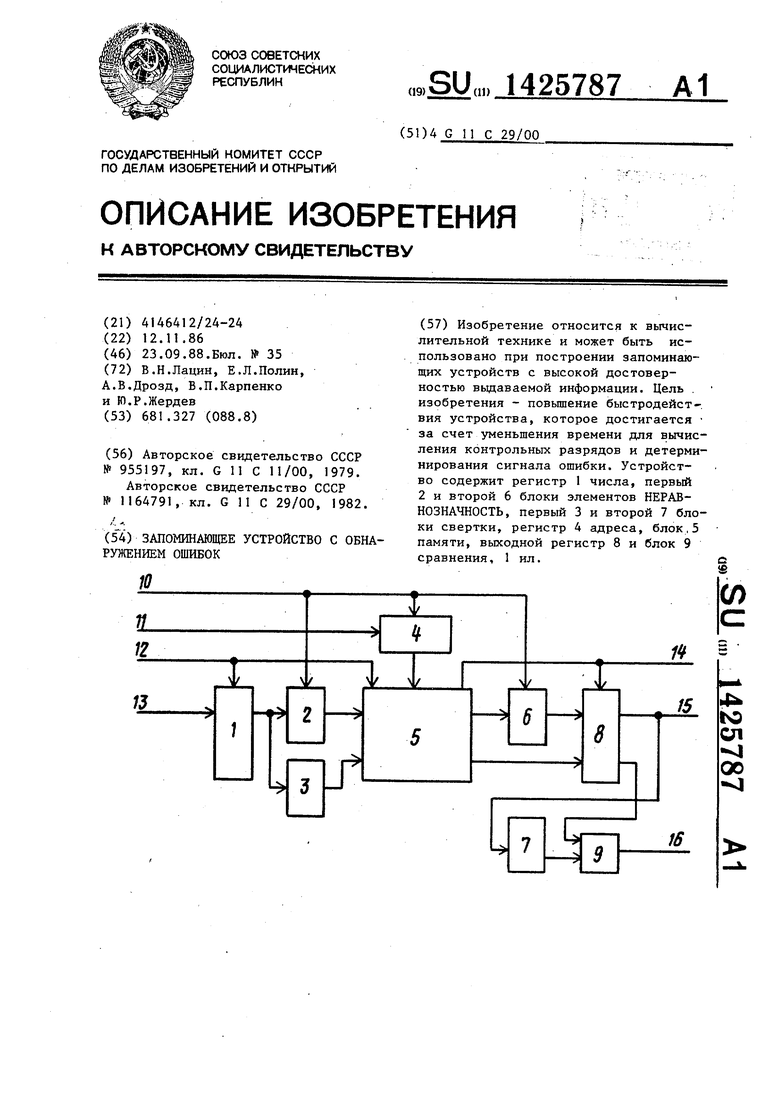

На чертеже представле а структурная схема устройства.

Устройство содержит регистр 1 числа, первый блок 2 .элементов НЕРАВНОЗНАЧНОСТЬ, первый блок 3 свертки, регистр 4 адреса, блок 5 памяти, второй блок 6 элементов НЕРАВНОЗНАЧНОСТЬ, второй блок 7 свертки, выходной регистр 8, блок 9 сравнения, адресные входы 1 О,-управляющий вход П, вход 12 управления записью, информационные входы 13, вход 14 управления чтением, тчформационные выходы 15 и контрольный выход 16.

Устройство работает следующим образом ,

На адресные входы 10 устройства поступает адрес ячейки блока 5, в ко торз ю должно записаться информационное слово, которое одновременно с . адресом поступает на информационные входы. Прием адреса в регистре 4 адреса происходит по отрицательному перепаду на входе 11, Далее на . вход 12 управления записью поступает сигнал записи, по которому происходит прием информационного слова в регистр 1.,Под управлением этого же сигнала блок 5 переводится в режим записи. При этом на его информационные входы поступает поразрядная сумма по модулю два входного слова, хранящегося в регистре 1, и адреса, по которому данное слово должно быть записано ,

При чтении из этой ячейки блока 5 адрес аналогично режиму записи заносится в регистр 4, а на вход 14 управления чтением подается сигнал чтения, который переводит блок 5 в режим чтения. Кодированное при записи информационное слово с некоторой задержкой считьшается из блока 5 и вместе с адресом чтения поступает на входы блока 6, где происходит декодирование считываемой информации.

Декодированное слово записъшает- ся в выходной регистр 8 вместе с контрольными разрядами, вычисленными блоком 3 свертки до записи соответствующего информационного слова в

блок 5. Контрольные разряды вычисляются как свертка по модулю. Занесение информации в выходной регистр 8 происходит по заднему фронту сигнала управления чтением на входе 14, . Второй блок 7 свертки вычисляет контрольные разряды для декодированного слова как свертку по тому же модулю,

что и блок 3. Блок 9 сравнения производит анализ совпадения контрольных разрядов вьмисленных до записи и кодирования и после считьшания декодирования .

При нормальной работе разрядных и адресных цепей устройства (хранение информации в блоке 5 осуществляется без искажения и адрес чтения соответствует адресу записи) декодирование считанного блока 5 слова происходит правильно и контрольные разряды, считанные из блока 5, совпадают с контрольными разрядами, вычисленными вторым блоком 7 свертки. На выходе блока 9 сравнения при этом будет удерживаться сигнал логического нуля. Если произошло искажение информации в блоке 5 в процессе хранения или или произошел сбой в адресных цепях

(закоротка или обрыв то контрольные разряды, вычисленные для декодированного слова, не совпадают с контрольными разрядами, считанными из блока 5. При зтом на выходе 16 устройства появится сигнал логической единицы,

свидетельствующий о сбое, в устройстве. ,

0

5

0

5

Формула изобретения Запоминающее устройство с обнаружением ошибок, содержащее блок памяти, регистр числа, регистр адреса, выходной регистр, первьй и второй блоки свертки и блок сравнения, причем информационный вход регистра числа является информационным входом устройства, информационные входы регистра адреса являются адресными входами устройства, вход приема регистра адреса является управляющим входом устройства, выходы регистра адреса соединены с адресными входами блока памяти, выходы контрольных разрядов блока памяти соединены с входами контрольных разрядов выходного регистра, выходы информационных разрядов которого являются информационными выходами устройства, выходы контрольных разрядов выходного регистра сое31Д257874

дииены с входами первой группы блокадами первого блока свертки, выходы Сравнения, вход записи блока памятипервого блока элементов НЕРАВНОЗНАЧ- и вход приема регистра числа объеди-НОСТЬ и первого блока свертки соединены и являются входом управлениянены соответственно с входами инфор- записью устройства, вход чтения бло-мационных и контрольных разрядов ка памяти и вход приема выходного ре-блока памяти, выходы информационных гистра объединены и являются входомразрядов блока памяти подключены к управления чтением устройства, о т -информационным входам второго блока личающееся тем, что, с Q элементов НЕРАВНОЗНАЧНОСТЬ, выходы целью повышения быстродействия уст-которого соединены с входами инфор- ройства, в него введены первый и вто-мационных разрядов выходного регист- рой блоки элементов НЕРАВНОЗНАЧНОСТЬ,ра, выходы информационных разрядов причем управляющие входы обоих бло-выходного регистра подключены к ков поразрядно объединены и соедине- 15 входам второго блока свертки, ны с адресными входами устройства,выходы которого соединены с входами выходы регистра числа соединены свторой группы блока сравнения, выход информационными входами первого бло-которого является контрольным вьгхо- ка элементов НЕРАВНОЗНАЧНОСТЬ и вхо-дом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с контролем по Хэммингу | 1983 |

|

SU1127011A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Устройство для задержки цифровой информации с самоконтролем | 1986 |

|

SU1429174A1 |

| Запоминающее устройство с обнаружением ошибок | 1987 |

|

SU1425790A1 |

| Устройство для задержки информации с контролем | 1986 |

|

SU1383323A1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1986 |

|

SU1439679A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств с высокой достоверностью вьщаваемой информации. Цель . изобретения - повьшение быстродействия устройства, которое достигается за счет уменьшения времени для вычисления контрольных разрядов и детерминирования сигнала ошибки. Устройство содержит регистр 1 числа, первый 2 и второй 6 блоки элементов НЕРАВНОЗНАЧНОСТЬ, первый 3 и второй 7 блоки свертки, регистр 4 адреса, блок,5 памяти, выходной регистр 8 и блок 9 сравнения, 1 ил.

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с обнаружением ошибок | 1984 |

|

SU1164791A1 |

| Солесос | 1922 |

|

SU29A1 |

| /- -. | |||

Авторы

Даты

1988-09-23—Публикация

1986-11-12—Подача