(Л

4

(Х

о со

.4

контроля коротких замыканий между контактными площадками интегральных схем. На первом этапе контроля осуществляется проверка наличия контактов к площадкам объекта 10 контроля. При этом коммутатор 5 отключает выводы объекта 10 контроля, выходы блока 2 ключей и входы многоканального паратора 3 от блока 7 нагрузок. На каждый канал блока 2 ключей поступает информация об необходимой коммутации с блока 1 памяти. При наличии контакта с выводом объекта 10 контроля через его входной диод протекает ток, которьй создает падение напряжения, фиксируемое измерителем 9. Превьшение входным напряжением нормы соответствует браку. Если входной сигнал ниже второго уровня, поступающего с программируемого источника 6 напряжений, то это значит, что нет контакта с объектом 10 контроля. Реакция объекта 10 контроля на функциональный контроль поступает на входы многоканального компаратора 3, которьй сравнивает эти реакции с ожидаемыми комбинациями с блока 1 памяти. Сигнал с выхода блока 1 памяти на ; триггер 15 (Брак) или на триггер 14 (Годный) заканчивает контроль. Введение блока 2 ключей, многоканального компаратора 3, блока 1 памяти, регистра 11, блока 7 нагрузок позволяет проводить проверку контактирования, целостности входных диодов и короткого замыкания выводом объекта 10 контроля. 5 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство параметрического контроля интегральных схем | 1985 |

|

SU1287060A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| Устройство контроля интегральных схем | 1986 |

|

SU1370634A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1348835A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

Изобретение относится к контрольно-измерительной технике и может быть применено для автоматизирован- ного контроля интегральных схем. Цель изобретения - расширение функциональных возможностей устройства за счет

1

Изобретение относится к контрольно-измерительной технике и может быгь применено для автоматизированного контроля интегральных схем.

Цель изобретения - расширение функциональных возможностей устройст на за счет контроля коротких замыканий между контактными площадками интегральных схем.

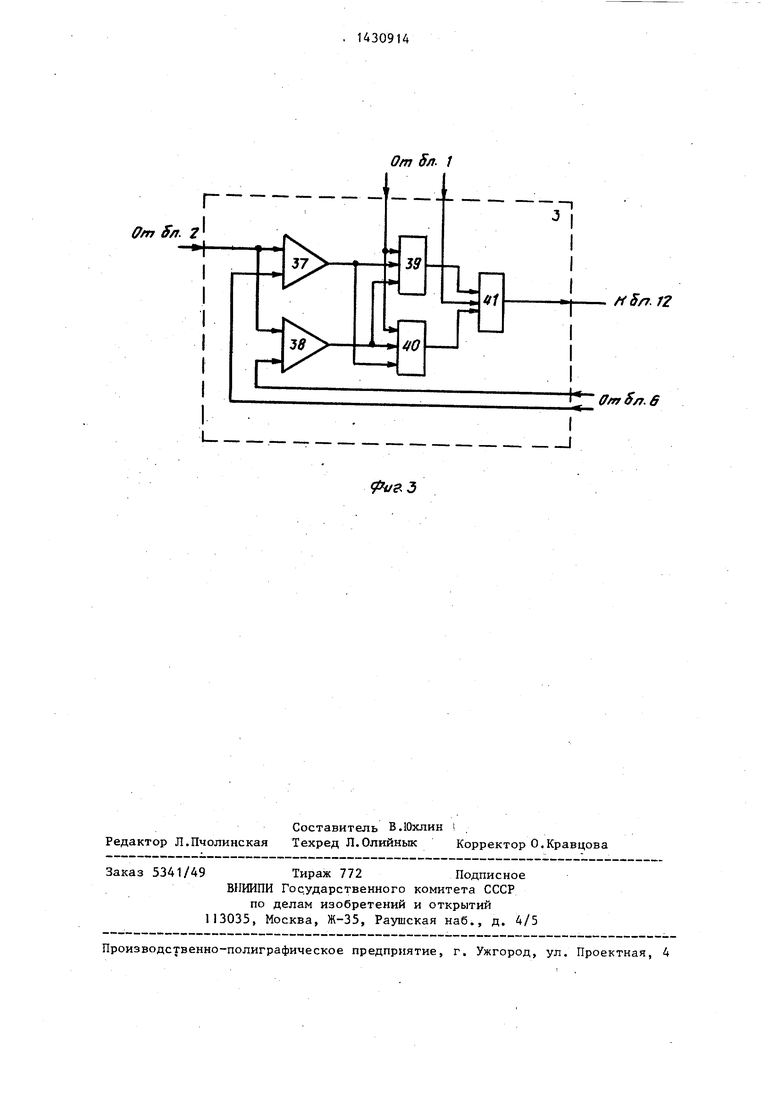

На фиг.1 приведена функциональная .схема устройства контроля интегральных схем; на фиг.2 - принципиальная схема одного канала блока ключей; на фиг.З - принципиальная схема одного канала многоканального компаратора.

Устройство содержит блок 1 памяти блок 2 ключей, многоканальный компаратор 3, первый и второй 5 коммутаторы, программируемый источник 6 напряжения, блок 7 нагрузок, генератор 8 тока, измеритель 9, объект 10 контроля, регистр 11 и блок 12 управле- ния.

Первый выход блока 12 управления соединен с первым входом блока 1 па- мяти, первые выходы которого соеди- нены с соответствующими первыми входами блока 2 Ключей, выходы которого соединены с соответствующими первыми входами многоканального компаратора

3 и с соответствующими первыми входами коммутатора 5, первые выходы которого соединены с соответствующими клеммами для подключения объекта 10 контроля, а вторые выходы - с соответствующими входами блока 7 нагрузок, выходы многоканального компаратора 3 соединены с соответствующими первыми входами блока 12 управления,

,второй выход которого соединен с управляющим входом регистра 11, информационные входы которого соединены с соответствующими вторыми выходами

блока 1 памяти, выходы регистра 11 соединены с соответствующими входами программного источника 6 напряжения, первые выходы которого соединены с соответствующими опорными входами измерителя 9, первый и второй выходы которого соединены соответственно с вторым и третьим входами блока 12 управления, четвертый, пятый, шестой, седьмой входы которого соединены соответственно с третьим, четвертым, пятым, шестым выходами блока 1 памяти, седьмые выходы которого соединены с .соответствующими первыми входами коммутатора 4, первый выход которого соединен с информационным входом измерителя 9, а вторые выходы с соответствующими вторьми входами блока 2 ключей, выходы генератора 8 тока соединены с соответствующими вторыми входами коммутатора 4,.третьи входы которого соединены с соответствующими вторыми выходами программируемого источника 6 напряжения,третьи выходы которого соединены с соответствующими вторыми входами многоканального компаратора 3, третьи входы которого соединены с соотв ет- ствующими восьмыми выходами блока Г памяти, девятые выходы которого соединены с соответствующими вторыми

входами коммутатора 5, десятые выходы блока 1 памяти соединены с соответствующими четвертыми входами многоканального компаратора 3.

Блок 12 управления содержит элемент НЕ 13, первый 14 и второй 15 триггеры, первый 16, второй 17 и третий 18 И1адикаторы, первый 19, второй 20 и третий 21 формирователи импульсов, первый 22, второй 23 и третий 24 элементы ИЛИ, первый 25, второй 26 и третий 27 элементы, счетчик

28, генератор 29 тактовых импульсов, щину 30 Пуск и шину 31 Код.

Выход счетчика 28 соединен с первым выходом блока 12 управления, второй выход которого соединен с выходом элемента ИЛИ 22, первый вход которого соединен с выходом формирователя 19 импульсов, щина 30 Пуск соединена с первыми входами триггеров 14 и 15, первым входом счетчика 28 через формирователь 20 импульсов с вторым входом элемента ИЛИ 22,первые выходы триггеров 14 и 15 соедиие- дд элемента И 39 и элемента ИЛИ-НЕ 40,

ны соответственно с первым и вторым входами элемента И 25, третий вход которого соединен с выходом генератора 29 тактовых импуль сов, выход элемента И 25 соединен с тактовым входом счетчика 28 и через формирователь 21 импульсов с первыми входами элементов И 26 и 27, выходы кото- рых соединены соответственно с вторым и третьим входами триггера 15, выход элемента ИЛИ 23 соединен с вто- рьм входом элемента И 26, выход элемента ИЛИ 24 соединен с вторым входом элемента И 27, входы элемента ИЛИ 24 являются первыми входами блока 12 управления, второй вход которого соединен с первым входом элемента ИЛИ 23, второй вход которого соединен с третьим входом блока 12

.45

50

55

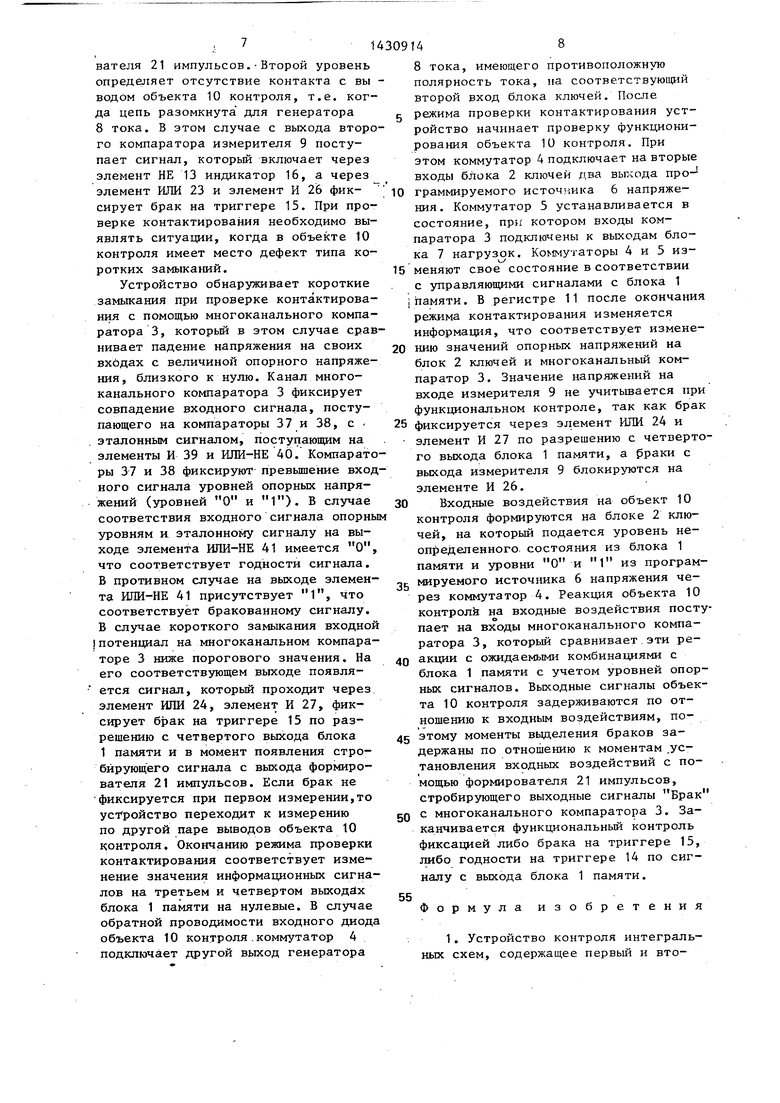

вторые входы которых соединен с выходом компаратора 37, а третьи - с выходом компаратора 38, выход элемента И 39 соединен с первым входом элемента ИЛИ-НЕ 41, выход которого является выходом канала, четвертый вход которого соединен с вторым входом элемента ИПИ-НЕ 41, третий вход которого соединен с выходом элемента ИЛИ-НЕ 40.

Коммутатор 4 содержит первое 42, второе 43 и третье 44 реле. Первые контакты реле 42 и 43 соединены с со ответствующими первыми входами коммутатора 4, первый выход которого соединен с вторыми контактами реле 42 и 43 и первьйч контактом реле 44, второй и третий контакты которого соединены с соответствующими вторыми

10

15

управления и через элемент НЕ 13 с индикатором 16, вторые выходы триггеров 14 и 15 соединены соответственно с индикаторами 17 и 18, четвертый, пятый, шестой и седьмой входы блока 12 управления соединены соответственно с входом формирователя 19 импульсов, третьим входом элемента И 26, третьим входом элемента И 27 и вторым входом триггера 14..

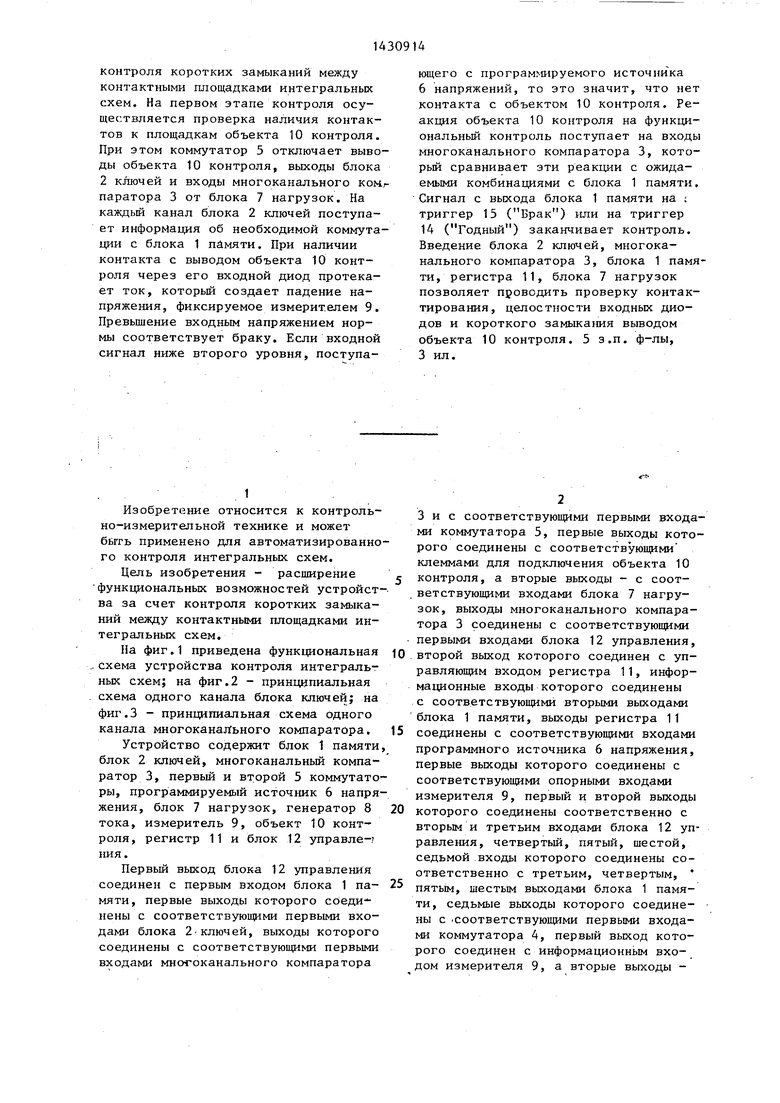

Один канал блока 2 ключей состоит из первого 32, второго 33 элементов И, первого 34 и второго 35 электронных ключей и элемента НЕ 36. Пер- |вьй вход канала соединен с первым входом элемента И 33, второй вход которого сЬединен с вторым входом элемента И 32 и вторьм входом канала, выход элемента И 32 соединен с управляющим входом электронного ключа 34, выход элемента И 33 соединен с управляющим входом электронного ключа 35, первый вывод которого со- единен с первым выводом электронного ключа 34 и выходом канала,третий и четвертый входы которого соединены соответственно с вторыми выводами электронных ключей 35 и 34.

Один канал многоканального компаратора 3 состоит иэ первого 37 и второго 38 компараторов элемента И 39 -И первого 40 и второго 41 элемен- тов ИЛИ-НЕ. Первый вход канала со- единен с первыми входами компараторов 37 и 38, вторые входы которых соединены с соответствуюсцими вторыми входами канала,третий вход которого соединен с первыми входами

20

25

30

35

вторые входы которых соединен с выходом компаратора 37, а третьи - с выходом компаратора 38, выход элемента И 39 соединен с первым входом элемента ИЛИ-НЕ 41, выход которого является выходом канала, четвертый вход которого соединен с вторым входом элемента ИПИ-НЕ 41, третий вход которого соединен с выходом элемента ИЛИ-НЕ 40.

Коммутатор 4 содержит первое 42, второе 43 и третье 44 реле. Первые контакты реле 42 и 43 соединены с соответствующими первыми входами коммутатора 4, первый выход которого соединен с вторыми контактами реле 42 и 43 и первьйч контактом реле 44, второй и третий контакты которого соединены с соответствующими вторыми

5

входами коммутатора 4, третьи входы которого соединены с соответствующими управляющими входами реле 42-44,

третьи контакты реле 42 и 43 соеди-

нень с соответствующими вторыми

выходами коммутатора 4.

Коммутатор 5 содержит первую 45.1-45.П и вторую 46.1-46.п группы реле.

Первые входы коммутатора 4 соединены с его выходами и первыми контактами реле 45.1-45.п, вторые контакты которых соединены с соответствующими первыми контактами реле 46.1-46.п, вторые контакты которых и третьи контакты реле 45.1-45.п дельно соединены с соответствующими вторыми входами коммутатора 4, третьи входы которого соединены с соот- ветствующими управляющими входами реле 45.1-45.11, 46.1-46.п.

Устройство работает следующим образом.

.

Первоначально в регистр 11 записывается информация из блока 1 памя- ти по уп1эавляющему сигналу с шины 30 Пуск через формирователь 20 импульсов и элемент ИЛИ 22. После этого на первом и втором входах элемента И 25 появляются сигналы разрешения с триггеров 14 и 15, т.е. тактовые импульсы с выхода генератора 29 тактовых импульсов начинают поступать Через элемент И 25 на- тактовый вход счетчика 28. По заданному адресу из счетчика 28 считывается информация блока 1 памяти. Функционально информация разбита на следующие группы:

Ня группа выходов блока 1 памяти несет информацию о входных воздействиях на блок 2 ключей;

2-я группа выходов блока 1 памяти задает ожидаемую эталонную информа- цию на многоканальный компаратор 3;

3-я группа выходов блока 1 памя- ти передает информацию состояния коммутатора 4;

4-я группа - состояния коммутатора 5;

5-я группа - коды величин напряжений на многоканальньй источник напряжения 6 через регистр 11;

6-я группа - признак смены .напря- жений;

7-я группа - признак режима контроля контактирования;

146

8-я группа - признак режима функционального контроля и режима проверки на короткие замыкания;

9-я группа - признак конца тестов о годности объекта контроля.

Регистр 11 необходим для того, чтобы исключить помехи на выходах блока 1 памяти при смене входного адреса. Запись в регистр 11 осуществляется по сигналу с щины 30 Пуск через формирователь 20 импульсов, а затем при смене режима контроля по сигналу с 6-го выхода блока памяти 1 через формирователь 19 импульсов и элемент ИЛИ 22.

Первоначально осуществляется проверка наличия контактов к площадкам объекта 10 контроля.При этом коммутатор 5 отключает выводы объекта 10 контроля, выходы блока 2 ключей и входы многоканального компаратора 3 от блока 7 нагрузок.

На каждьй канал блока 2 ключей поступает информация о необходимой коммутации с блока 1 памяти.

Появление единицы на выходе одного из элементов И 32 или 33 открывает один из ключей 34, или 35, т.е. происходит перекоммутация одного из выходов коммутатора 4 на выход клю- ,чей 34 или 35. Коммутатор 4 подключает к одному из вторых входов блок/ 2 ключей один из выходов программиру емого источника 6 напряжения, а другой вход блока 2 ключей подключается К первым выходам генератора 8 тока. Значение напряжения программируемого источника 6 напряжения равно О. Ток и нулевой потенциал поступают на два соответствующих вывода объекта 10 контроля. Выбор вывода объекта 10 контроля определяется информацией с блока 1 памяти. При наличии контакта с выводом объекта 10 контроля через его входной диод протекает ток, которьй создает падение напряжения, фиксируемое измерителем 9. Компараторы измерителя 9 сравнивают уровень входного напряжения с двумя опорными напряженияьш, задаваемыми программируемым источником 6 напряжений. Превьш1ение входным напряжение Hopi-ibi соответствует браку, который фиксируется с выхода соответствующего компаратора измерителя 9 через . элемент ИЛИ 23 и элемент И 26 на . триггере 15 в момент появления стро- бирующего импульса с выхода формиро-10

15

20

25

14309

вателя 21 импульсов.Второй уровень определяет отсутствие контакта с вы - водом объекта 10 контроля, т.е. когда цепь разомкнута для генератора 8 тока. В этом случае с вьгхода второго компаратора измерителя 9 поступает сигнал, который включает через элемент НЕ 13 индикатор 16, а через элемент ИЛИ 23 и элемент И 26 фик- сирует брак на триггере 15. При проверке контактирования необходимо выявлять ситуации, когда в объекте 10 контроля имеет место дефект типа коротких замыка1шй.

Устройство обнаруживает короткие замьжания при проверке контактирования с помощью многоканального компаратора 3, которьш в этом случае сравнивает падение напряжения на своих входах с величиной опорного напряжения, близкого к нулю. Канал многоканального компаратора 3 фиксирует совпадение входного сигнала, поступающего на компараторы 37 и 38, с эталонным сигналом, поступающим на элементы И 39 и ИЛИ-НЕ 40. Компараторы 37 и 38 фиксируют превышение входного сигнала уровней опорных напряжений (уровней О и 1). В случае соответствия входного сигнала опорным уровням и эталонному сигналу на выходе элемента ИЛИ-НЕ 41 имеется О, что соответствует годности сигнала. В противном случае на выходе элемента ИПИ-НЕ 41 присутствует 1, что соответствует бракованному сигналу, В случае короткого замыкания входной

потенциал на многоканальном компараторе 3 ниже порогового значения. На его соответствующем выходе появляется сигнал, который проходит через элемент ИЛИ 24, элемент И 27, фиксирует брак на триггере 15 по разрешению с четвертого выхода блока 1 памяти и в момент появления стро- бйрующ его сигнала с выхода формирователя 21 импульсов. Если брак не иксируется при первом измерении,то устройство переходит к измерению по другой паре выводов объекта 10 контроля. Окончанию режима проверки контактирования соответствует изменение значения информационных сигнаов на третьем и четвертом выходах блока 1 памяти на нулевые. В случае обратной проводимости входного диода объекта 10 контроля.коммутатор 4 подключает другой выход генератора

30

35

40

45

50

55

0

5

0

5

09

0

5

0

5

0

5

148

8 тока, имеющего противоположную полярность тока, на соответствующий второй вход блока ключей. После режима проверки контактирования устройство начинает проверку функционирования объекта 10 контроля. При этом коммутатор 4 подключает на вторые входы блока 2 ключей два выхода про- граммируемого источника 6 напряжения. Коммутатор 5 устанавливается в состояние, пря котором входы компаратора 3 подключены к выходам блока 7 нагрузок. Коммутаторы 4 и 5 изменяют свое состояние в соответствии с управляющими сигналами с блока 1 памяти. В регистре 11 после окончания режима контактирования изменяется информация, что соответствует изменению значений опорных напряжений на блок 2 ключей и многоканальный компаратор 3. Значение напряжений на входе измерителя 9 не учитьшается при функциональном контроле, так как брак фиксируется через элемент ИЛИ 24 и элемент И 27 по разрешению с четвертого выхода блока 1 памяти, а 0раки с выхода измерителя 9 блокируются на элементе И 26.

Входные воздействия на объект 10 контроля формируются на блоке 2 ключей, на который подается уровень неопределенного, состояния из блока 1 памяти и уровни О и 1 из программируемого источника 6 напряжения через коммутатор 4. Реакция объекта 10 контроля на входные воздействия поступает на входы многоканального компаратора 3, который сравнивает.эти реакции с ожидаемыми комбинациями с блока 1 памяти с учетом уровней опорных сигналов. Выходные сигналы объекта 10 контроля задерживаются по отношению к входным воздействиям, поэтому моменты выделения браков задержаны по отношению к моментам .установления входных воздействий с помощью формирователя 21 импульсов, стробирующего выходные сигналы Брак с многоканального компаратора 3. Заканчивается функциональный контроль фиксацией либо брака на триггере 15, либо годности на триггере 14 по сигналу с выхода блока 1 памяти.

Формула изобретения

первые выходы второго коммутатооа го- in ш-.

м V лимму1с11ора со 10 содержит элемент НЕ, первый и втоединены с соответствующими клеммами для подключения объекта контроля, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены блок ключей, многоканальный компаратор,блок памяти, регистр, блок нагрузок, причем вторые выходы программируемого источника напряжений соединены с соответствующими первыъш входами первого коммутатора, вторые входы которого соединены с соответствующими выходами генератора тока, первый выход блока управления соединен с перрой триггеры, первый, второй и трет индикаторы, первый, второй и третий формирователи импульсов, первый, вт рой и.третий элементы ИЛИ, первый,

15 второй и третий элементы И, счетчик генератор тактовых импульсов, шину Пуск, , причем выход сче чика соединен с первым вьпсодом бло второй выход которого соединен с

20 выходом первого элемента ИЛИ, первы вход которого соединен с выходом пе вого формирователя импульсов, шина Пуск соединена с первыми входами первого и второго триггеров, первым

20 выходом первого элемента ИЛИ, первый вход которого соединен с выходом пер вого формирователя импульсов, шина Пуск соединена с первыми входами первого и второго триггеров, первым

вым входом блока памяти, первые выхо- 25 входом счетчика и через второй форды которого соединены с соответствующими первыми входами блока ключей, выходы которых соединены с соо.твет- ствующими первыми BxoAah« многоканального компаратора и соответствующими первь 1И входами второго коммутатора, вторые выходы которого соединены с соответствующими входам блока нагрузок, вторые входы многоканаль-- ного компаратора соединены с соот- ветствующим вторыми выходами блока памяти, третьи вькоды которого соединены с соответствующими третьими входами первого коммутатора, вторые выходы первого коммутатора соединены с вторыми входами блока ключей, вторые входы второго коммутатора соединены с соответствую11№1ми четвертыми выходами блока памяти, пятые выходы которого соединены с соответствующими первыми входами регистра, выходы которого соединены с соответствующими входами программируемого источника напряжений, третьи выходы которого соединены с третьими входами многоканального компаратора, выходы которого соединены с соответствующими первыми входами блока управления, . второй, третий входы которого соединены соответственно с первым и вторым ; выходами измерителя, шестой, седьмой, восьмой и девятый выходы блока памяти соединены соответственно с v четвертым, пятым, шестым и седьмым

мирователь импульсов с вторым входом первого элемента ИЛИ, первые вы ходы первого и второго триггеров соединены соответственно с первым и

30 вторым входами первого элемента И, третий вход которого соединен с вых дом генератора тактовых импульсов, выход первого элемента И соединен с входом счетчика и через третий фор35 мнрователь импульсов с первыми вход ми второго и третьего элементов И, выходы которых соединены соответственно с вторым и третьим входами вто рого триггера, выход второго элемен

40 та ИЛИ соединен с вторым входом вто рого элемента И, выход третьего эле мента ИЛИ соединен с вторым входом третьего элемента И, входы третьего элемента ИЛИ соединены с соответств

45 ющими первыми входами блока, второй вход которого соединен с первым вх дом второго элемента ИЛИ, второй вход которого соединен с третьим вх дом блока и через элемент НЕ с перв

50 индикатором, вторые выходы первого

и второго триггеров соединены соотв ственно с вторым и третьим индикато рами, четвертый вход блока соединен с входом первого формирователя им55 пульсов, пятый вход - с третьим вх дом второго элемента И, шестой вход с третьим входом третьего элемента И седьмой вход - с вторым входом перво го триггера.

входами блока управления, второй вы-i ход которого соединен с вторым входом регистра, десятые выходы блока памяти соединены с соответствуюи1ими четвертыми входами многоканального компаратора.

ш-.

рой триггеры, первый, второй и третий индикаторы, первый, второй и третий формирователи импульсов, первый, второй и.третий элементы ИЛИ, первый,

второй и третий элементы И, счетчик, генератор тактовых импульсов, шину Пуск, , причем выход счетчика соединен с первым вьпсодом блока, второй выход которого соединен с

выходом первого элемента ИЛИ, первый вход которого соединен с выходом первого формирователя импульсов, шина Пуск соединена с первыми входами первого и второго триггеров, первым

входом счетчика и через второй фор

мирователь импульсов с вторым входом первого элемента ИЛИ, первые выходы первого и второго триггеров соединены соответственно с первым и

0 вторым входами первого элемента И, третий вход которого соединен с выходом генератора тактовых импульсов, выход первого элемента И соединен с входом счетчика и через третий фор5 мнрователь импульсов с первыми входами второго и третьего элементов И, выходы которых соединены соответственно с вторым и третьим входами второго триггера, выход второго элемен0 та ИЛИ соединен с вторым входом второго элемента И, выход третьего элемента ИЛИ соединен с вторым входом третьего элемента И, входы третьего элемента ИЛИ соединены с соответству5 ющими первыми входами блока, второй вход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с третьим входом блока и через элемент НЕ с первым

0 индикатором, вторые выходы первого

и второго триггеров соединены соответственно с вторым и третьим индикаторами, четвертый вход блока соединен с входом первого формирователя им5 пульсов, пятый вход - с третьим входом второго элемента И, шестой вход - с третьим входом третьего элемента И, седьмой вход - с вторым входом первого триггера.

; 111430914

ойство по п.1, о т л и ч а- я тем, что каж;дый канал ьного компаратора содержит торой компараторы,элемент и второй элементы ШШ-НЕ, вый вход канала соединен входами первого и второго ов,вторые входы которых с соответствующими вторыми

10

ка то вт кл эл

ю то ре и ст ра вт ре ре ро вт ть ве пе тр ле

входами канала, третий вход которого соединен с первыми входами элемента И и первого элемента ИЛИ-НЕ, вторые входы которых соединены с выходом первого компаратора, а третьи - с выходом второго компаратора, выход элемента И соединен с первым входом второго элемента И)Щ-НЕ, выход которого соединен с выходом канала, четвертый вход которого соединен с вторым входом второго элемента ИПИ-НЕ, третий вход которого соединен с выходом первого элемента ИЛИ-НЕ.

I 2

0

5

0

5

0

5

0

канала, третий и четвертый входы которого соединены соответственно с вторь м выводом первого электронного ключа и с вторым выводом второго электронного ключа.

От 5л. 1

. 3

| Устройство для контроля логических блоков | 1982 |

|

SU1078365A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля интегральных схем | 1984 |

|

SU1208555A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-10-15—Публикация

1987-01-06—Подача