128

мируемый источник напряжений 14, элемент ИЛИ 15, блок 25 управления, регистр 8. Для достижения поставленной цели в устройство введены многоканальный компаратор 7, блок 13 совпадения, блоки 9, 10 памяти, блок 11 нагрузок, блок 16 выделения напряжений, образованы новые функциональные связи. В описании изобретения предложен вариант исполнения блока вьзделения напряжений и блока управления. Работа устройства заклюИзобретение относится к вычислительной технике и может быть приме- нен о -для параметрического контроля интегральньпс схем (ИС) .

1Дель изобретения - повьшение быстродействия контроля.

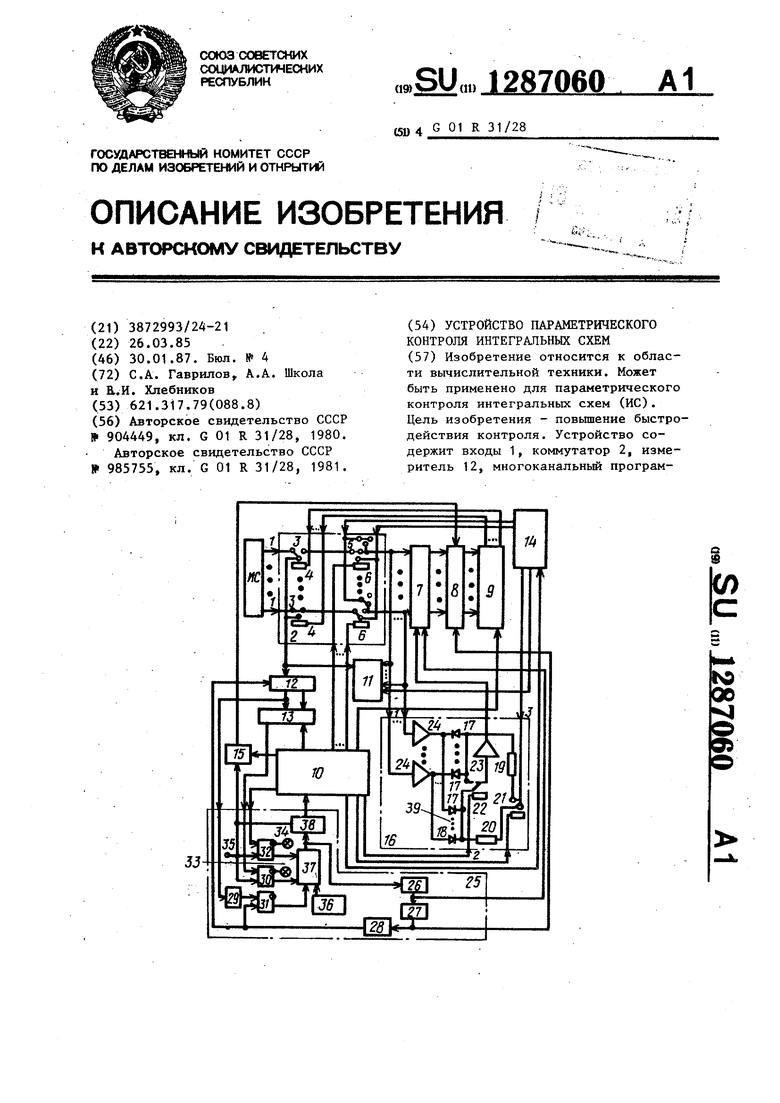

На чертеже представлена структурная схема устройства параметрического контроля ИС.

Устройство состоит из входов 1, коммутатора 2, состоящего из первойу группы реле с контактами 3 и обмот- ками управления 4, второй группы реле с контактами 5 и обмотками управления 6, многоканального компаратора 7, регистра 8, первого 9 и второго 10 блоков памяти, блока 11 нагрузок, измерителя 12, блока 13 совпадения, многоканального программируемого источника 14 напряжений, элемента ИЛИ 15, блока 16 вьщеления напряжений, Состоящего, например из первой 17 и второй 18 диодных групп, первого 19 и бторого 20 резисторов, первого 21 и второго 22 реле, операционного усилителя 23, группы 24 операционных усилителей; блока 25 управления, состоящего, например, из четырех элементов задержки 26-29, трех триггеров 30 - 32, двух индикаторов 33 и 34, входа 35 Пуск, генератора 36 тактовых импульсов, элемента И 37, счетчика 38.

Входами 1 устройства являются первые входы коммутатора 2, вторые входы которого соединены с выходами - первого блока 9 памяти, первые входы которого соединены с выходами регистра 8, первые входы которого соечается в последовательном контроле всех заданных параметров ИС. Устройство позволяет значительно быстрее обеспечить параметрический контроль ИС за счет измерения только на тех выходах ИС, которые имеют наихудшие параметры. Использование устройства для контроля ИС позволяет резко повысить производительность контроля в том случае, когда требуется : проводить большое количество измереНИИ параметров. 2 з.п. ф-лы, 1 ил.

5

0

5

0

5

динены с выходами многоканального компаратора 7, измерительные входы

которого соединены с первыми выходами коммутатора 2, первыми входами блока 11 нагрузок и первыми входами блока 16 вьщеления напряжений, вторые входы которого соединены с первыми выходами второго блока 10, вторые выходы которого соединены с входами источника 14 напряжений, первьй выход которого соединен со вторым входом блока 11 нагрузок, два третьих входа коммутатора 2 соединены с двумя вторыми выходами источника 14 напряжений соответственно, третий выход источника 14 напряжений соединен с третьим входом блока 16 вьщеления напряжений, выход которого соединен с задающим входом многоканального компаратора 7, стро- бирующий вход которого соединен с первым выходом блока 25 управления, второй выход которого соединен со стробирующим входом регистра 8, сбросовый вход которого соединен с выходом элемента ИЛИ 15. Третьи выходы второго блока 10 памяти соединены с четвертыми входами коммутатора 2, второй выход которого соединен с третьим входом блока 11 и измерительным входом измерителя 12, второй вход которого соединен с третьим выходом блока 25 управления, четвертые выходы которого соединены с входами второго блока 10 памяти, четвертые выходы которого соединены с первым входом блока 13. Выход ответа измерителя 12 соединен с первым входом блока 25 управления и

стробирующим входом блока 13, второй вход которого соединен с вторым выходом измерителя 12. Выход блока 13 соединен с вторым входом блока 25 управления, третий вход которого со- единен с пятым выходом второго блока памяти 10, шестой выход которого соединен с первым входом элемента ИЛИ 15, второй вход которого соединен с пятым выходом блока 25 управления, седьмой выход блока памяти 10 соединен с вторым входом блока памяти 9, а восьмой - с четвертым входом блока 16.

Устройство работает следуклцим об- разом.

Функцией блока 16 является вьще- ление максимального или минимального из напряжений , имеющихся на его первых входах и передача этого нап- - ряжения на свой выход. Допустим, ч что все напряжения на первых входах блока 16 выделения напряжений (U, U2,...,Uf,, где п - количество входов) имеют положительную полярность, и реле 21 и 22 находятся в положении показанном на чертеже (в случае отрицательных напряжений эти реле должны находиться в положении, обозначенном пунктиром).

Напряжения на выходах операционных усилителей группы 24 (ОУ 24) будут соответственно равны И KU, ; и KU2,...,U; K U,, где К- коэффициент усиления ОУ 24.

Если на третий вход блока вьщеле- ния напряжений 16 подать нулевой потенциал, то напряжение в точке (39) будет равно максимальному из напря- жений Uj ,и ,... , за вычетом падения напряжения на открытом диоде группы 18, т.е.

UB макс (up - ид К. макс (Uj )-U

где Цд - падение напряжения на открытом диоде группы 18. В этом случае на выходе операционного усилителя 23, который имеет коэффициент усиления равный 1/К будет напряжение

Uj3 макс (Ui) - --|- ,

т.е. на втором выходе блока 16 уста- новится максимальное из напряжений на его первых входах за вычетом поправки. Если же на третий вход блока выделения 16 подать напряжение, большее каждого из и Д ,....,,,, то напряжение в точке (39) равно

и, мин (и) + UA К-мин (и)+ид

тогда, напряжение на выходе операционного усилителя 23 равно

I

и,, мин (и,)-ь -|- ,

5 О

5

0

5

0

5

0

5

т.е. на втором выходе блока 16 установится минимальное из напряжений на его первых входах плюс поправка ид/К.

Аналогичным образом производится выбор максимального или минимального из напряжений на первых входах блока выделения 16 тогда, когда они имеют отрицательную полярность. При этом реле 21 и 22 должны быть переведены в положение, обозначенное на чертеже пунктиром.

Величина Пд/К выбирается из требований разрешающей способности многоканального компаратора 7. Эта величина напряжения является также и величиной допустимой зоны фиксации предельных значений по другим входам 1. В случае попадания в эту зону нескольких входов выбор входа .1 для замера на измерителе 12 осуществляется блоком памяти 9, который из нескольких предельных входов 1 выделяет один и переключает одно из реле первой группы.

Работа устройства заключается в последовательном контроле всех заданных параметров ИС. При контроле каждого из параметров вьтолняется следующая последовательность деист- ВИЯ: подготовка устройства к контролю очередного параметра; поиск входа 1, который обладает наихудшим значением контролируемого параметра; измерение з.начения контролируемого параметра на выбранном входе 1.

Начинается работа устройства с подачи на вход Пуск 35. По этому сигналу сбрасывается счетчик 38 и регистр 8, а триггера 32 и 30 переводятся в состояние, соответствующее разрешению прохождения тактовых импульсов с генератора 36 через элемент И 37 на вход счетчика 38 (индикаторы Годность 34 и Брак 33 при этом гаснут). При обнулении регистра 8 из блока памяти 9 выбирается ячейка, соответствующая нулевым значениям на олч) riepnt-ix входах.

независимо от второго входа блока памяти 9 на его выходах появляется код, по которому реле первой группы отключают входы 1 от измерителя 12 и подключают их к реле второй группы.

При обнулении счетчика 38 сигналом с входа Пуск 35 из блока памяти 10 выбирается первая ячейка. По появлении информации, хранящейся в этой ячейке, на выходах блока памя- ти 10, производятся следующие действия.

С четвертых выходов на блок 13 подается уставка, соответ.ствумцая границе допустимого значения контролируемого параметрар один из разрядов уставки задает больше или меньше данной величины должно- быть измерен1287060--6

мяти 10 переводятся в

как показано на чертеж контроля при отрицател ниях они переводятся 5 показанное пунктиром.

С седьмого выхода б 10 на второй вход блок дается сигнал, указыва

0 кой из вькодов ИС 1 не тать наихудшим, тот ко максимальное значение го параметра, или тот, раметра у которого мин

5 С появлением первог генератора тактовых им входе счетчика 38, его увеличивается на едини из блока 10 памяти выб

ное значение контролируемого парамет- 20 рая ячейка, содержимое которой равра.

jC вторых выходов блока памяти 10 подается код на входы многоканального источника 14 напряжения. При этом с третьего выхода источника 14 на третий вход блока 16 вьщеления напряжений подается напряжение в соответствии с тем, какое из напряжений на первых входах блока 16 вьщеления должно быть выделено на его выходе, максимальное или минимальное , С первого и второго выходов источника 14 подаются напряжения соответственно на второй вход блока 11 нагрузок и третий вход коммутатора 2, необходимые для установки объекта контроля в нужный для контроля режим. С четвертого выхода источника 14 на пятый вход коммутатора 2 подается напряжение, которое необходимо установить на незадействованных при контроле измерительных входах многоканального компаратора 7;

С помощью третьих выходов блока памяти 10 реле второй группы коммутатора 2 переключаются в положение, при котором контролируемые входы 1 подключаются ко входам многоканального компаратора 7, первым входом блока 11 нагрузок и первым входом блока 16 выделения напряжений. Остальные входы 1 соединяются со вторым выходом программируемого источника 14. .

В случае контроля при положительных напряжениях реле 21 и 22 по информации с первых выходов блока памяти 10 переводятся в

положение, как показано на чертеже. В случае контроля при отрицательных напряжениях они переводятся в положение, показанное пунктиром.

С седьмого выхода блока памяти 10 на второй вход блока памяти 9 подается сигнал, указывающий на то, какой из вькодов ИС 1 необходимо считать наихудшим, тот который имеет максимальное значение контролируемого параметра, или тот, значение параметра у которого минимально.

С появлением первого импульса с генератора тактовых импульсов 36 на входе счетчика 38, его содержимое увеличивается на единицу. При этом из блока 10 памяти выбирается содержимому первой ячейки и, поэтому состояние устройства при этом не изменяется. Это сделано , чтобы исключить завис1 |ость от взаг имного расположения во времени сигналов с генератора 36 и сигнала на входе Пуск 35.

Этот же импульс пройдет через элементы задержки 26-28. Задержка на элементе 26 обеспечивает окончание переходных процессов на входах многоканального компаратора и выходе блока вьщеления напряжений 16.

Сигнал с выхода элемента 26 поступает на стробирующий вход компаратора 7. Вход порога на многоканальном л компараторе 7 соединен непосредственно с выходом блока 16 вьщеления,

поэтому на выходах многоканального компаратора -7 будет вьщелен вход 1 с наихудшим значением контролируемого параметра. Если наихудшим входом 1 является трт,который имеет наибольшее значение контролируемого параметра, то соответствующий ему выход компаратора 7 будет установлен в состояние логического О, в то время как другие выходы компаратора находятся в состоянии логической 1. В случае, когда наихудшим входом 1 является тот, у которого значение контролируемого . вывода минимально, соответствующий ему выход компаратора 7 будет установлен в состояние логической 1, в то время как другие выходы компаратора будут находиться в состоянии логического О.

При появлении сигнала на выходе .элемента 27 задержки состояние выходов компаратора 7. записывается в регистр 8, откуда поступает на вход блока 9 памяти. При этом, в зависимости от второго входа блока 9 памяти (этот вход установлен в зависимости от того, какой из входов 1 является наихудшим, тот который имеет максимальное или минимальное значение параметра) и первых входов блок 9 памяти на его выходах появляется код, по которому наихудший вход 1 с помощью реле первой группы коммутатора 2 подключается к измерительному входу измерителя 12.

В информации, записанной в блоке 9 памяти, предусмотрен и тот случай когда разрешающая способность компаратора 7 и блока 16 выделения напряжений не позволяет выделить равно один вход 1 с наихудшим значением контролируемого параметра. В этом случае может, например, выбираться тот из наихудших входов 1, который имеет наименьший номер.

После появления сигнала на выходе элемента 28 задержки запускается измеритель 12, который к этому моменту подключен к входу 1 с наихудшим значением контролируемого параметра. Для ожидания конца измерений в устройство введен триггер 31, который сигналом запуска измерителя 12 переводится в состояние, При котором запрещается прохождение импульсов через элемент И 37. Поэтому состояние устройства не изменяется до тех пор, пока триггер 31 не будет опять переведен в состояние, разрешающее прохождение импульсов через элемент И 37, сигналом Конец измерений, который вырабатывается на первом выходе измерителя 12 и проходит на триггер 31 через элемент 29 задержки. Элемент 29 введен для того, чтобы переход к контролю следующего параметра не начинался до тех пор, пока не будет установлена годность контролируемой ИС по текущему параметру.

Решение о годности контролируемой ИС по текущему параметру устанавливается по выходу блока 13, на который со вторых выходов измерителя 12 поступает измеренное значение параметра. Стробируется блок 13 сигналом Конец измерения с перво-

го выхода измерителя 12. Если блок 13 устанавливает брак ИС по контролируемому параметру, то на его выходе появляется сигнал, который переводит триггер 30 в состояние, при котором загорается индикатор брак 33 и запрещается прохождение тактовых импульсов через элемент И 37. Работа устройства заканчивается.

В случае, если не установлен брак ИС по контролируемому параметру, триггер 31 открывает элемент И 37, и очередной тактовый импульс с генератора 36 тактовых импульсов поступает на вход счетчика 38 и элемента 26 задержки. Происходит сброс регистра 8 сигналом с шестого выхода блока памяти 10,. проходящем через элемент ИЛИ 15, подготовка устройства к контролю следующего параметра ИС, нахождение вывода ИС, обладающего наихудшим значением данного параметра и затем непосредственное измерение значения параметра на выбранном выводе. Вьшолняются эти операции аналогично тем, которые описаны для контроля первого параметра.

Если величина некоторого контролируемого параметра должна находиться в области между двумя значениями и, следовательно, наихудшими входами являются входы с наибольшим и наименьшим значениями параметра, то в этом случае производится два измерения соответственно с выводов, имеющих наибольшее и наименьшее значения параметра.

Если ни по одному параметру ИС не обнаруживается брак, то с пятого выхода блока 10 памяти триггер 32 переводится в состояние, при котором загорается индикатор Годность 34 и запрещается прохождение тактовых импульсов через элемент 37 И. Работа

устройства заканчивается.

Коммутатор 2 обеспечивает также блокировку тех входов многоканального компаратора 7, которые не исполь-

зуются при контроле данного параметра. В этом случае на них с четвертого выхода многоканального программируемого источника 14 напряжений подается потенциал, соответствующий

гарантированной годности ИС по данному параметру, например другой полярности, что обеспечивает исключение выбора вьшода ИС, который не участвует в контроле по данному па-

91287060

аметру. Этот потенциал поступает дов ерез контакты 5 реле, которые подлючены на соответствующие входы ногоканального компаратора 2. .

Количество измерений, необходиых для контроля ИС с помощью даного устройства равно

но дам ми ми рой вых рой дом го ход дом тор дом вет упр сов с в тре стр ком упр дом сое тре с д нал нап сое дел сое нал ход с N соо упр рог кот бло рог изм ка бло пер вых пер чет нап

N

п, + .2« п

2

где HI - количество параметров, имеющих одно граничное значение;

п.- количество параметров, имеющих два граничных значения.

Таким образом, устройство позволяет значительно быстрее обеспечить параметрический контроль ИС за счет измерения только на тех выводах ИС, которые имеют наихудшие параметры.

Использование устройства для контроля ИС позволяет резко повысит производительность контроля в том случае, когда требуется проводить большое количество измерений параметров.

Формула изобретения 30

Устройство параметрического- контроля интегральных схем, содержащее коммутатор, измеритель, многоканальный программируемый источник напряжений, элемент ИЛИ, блок управления, регистр, причем N-первых входов коммутатора соединены соответственно с N-входами устройства, первый измерительный вьпсод коммутатора соединен с измерительным входом измерителя, запускающий вход которого соединен с первым выходом блока управления, второй выход которого соединен с первым входом элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия контроля, введены многоканальный i компаратор, блок совпадения, первый и второй блоки памяти, блок нагрузок, блок выделения напряжений, причем N-вторых входов коммутатора соединены соответственно с N-выходами первого блока памяти, N-первых вхо- дов которого соединены с N-выходами регистра соответственно N-первых входов которого соединены с N-выходами многоканального компаратора соответственно, N-измерительных вхо10

5

0

0

5

5

0

5

которого соединены соответственно с N-вторыми измерительными выходами коммутатора, N-первыми входами блока нагрузок и Ы-первыми входами блока выделения напряжений, второй вход которого соединен с первьм выходом второго блока памяти, второй выход которого соединен с входом многоканального программируемого источника напряжения, первый выход которого соединен с вторым входом блока нагрузок, третий вход которого соединен с измерительным входом измерителя, у которого выход ответа соединен с первым входом блока управления и стробовым входом блока совпадения, выход которого соединен с вторым входом блока управления, третий выход которого соединен с стробовым входом многоканального компаратора, четвертый выход блока управления соединен с стробовым.входом регистра, вход сброса которого соединен с выходом элемента ИЛИ, два третьих входа коммутатора соединены с двумя вторыми выходами многоканального программируемого источника напряжения, третий выход которого соединен с третьим входом блока выделения напряжений, выход которого соединен с задающим входом многоканального компаратора, N-третьих выходов второго блока памяти соединены с N-четвертыми входами коммутатора соответственно, пятьш выход блока управления соединенi с входом второго блока памяти, четвертый выход которого соединен с первым входом блока совпадения, второй вход которого соединен с выходом результата измерителя, пятый выход второго блока памяти соединен с третьим входом блока управления, шестой выход - с первым входом элемента ИЛИ, седьмой выход - соединен с вторым входом первого блока памяти, а восьмой - с четвертым входом блока выделения напряжений.

2. Устройство по п, а ю щ е в с я тем.

1, о т л и - что блок выделения напряжений состоит из первой и второй диодных групп, первого и второго резисторов,.двух реле, группы операционных усилителей, операционного усилителя, причем входы группы операционных усилителей являются N-первыми входами блока выделения напряжений, второй вход которого со

111

единен с обмотками первого реле, первый контакт которого через операционный усилитель соединен с выходом блока выделения напряжений, третий вход которого соединен с первым контактом второго реле, второй контакт которого через первый резистор соединен с вторым контактом второго реле и общим вькодом первой диодной группы, раздельные входы которой соединены с соответствующими выходами группы операционных усилителей и с соответствующими раздельными входами второй диодной группы, общий выход которой соединен с третьим контактом первого реле и через второй резистор с третьим контактом второго реле.

3. Устройство по п. 1, отличающееся тем, что блок уп- I равления состоит из первого, второго, третьего и четвертого элементов задержки, первого, второго и третьего триггеров первого и второго индикаторов, входа Пуск, генератора тактовых импульсов, элемента И, счетчика, причем выход первого элемента задержки является третьим выходом блока управления и соединен с входом второго элемента задержки.

Редактор И. Сегляник

Составитель В, Савинов

Техред М.Ходанич Корректор Е. Сирохман

Заказ 7710/47.Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

12

выход которого является четвертым выходом блока управления и соединен с входом третьего элемента задержки, вькод которого соединен с первым выходом блока управления и первым входом первого триггера, вход Пуск соединен с сбросовым входом счетчика, первыми входами второго и третьего триггеров и вторым выходом блока управления, пятый выход которого соединен с выходом счетчика, тактовый вход которого соединен с входом первого элемента задержки и выходом,элемента И, первый вход блока управления через четвертый элемент задержки соединен с вторым входом первого триггера, второй вход блока управления соединен с вторым входом второго триггера, третий вход блока управления соединен с вторым входом третьего триггера, первые выходы первого, второго и третьега триггеров соединены соответственно с первым, вторым и третьим входами

элемента И, четвертый вход которого соединен с выходом генератора тактовых импульсов, вторые выходы второго и третьего триггеров соединены соответственно с первым и вторым инди|каторами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1430914A1 |

| Устройство контроля интегральных схем | 1986 |

|

SU1370634A1 |

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1348835A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

| Устройство для контроля интегральных схем | 1984 |

|

SU1208555A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство контроля интегральных схем | 1982 |

|

SU1049838A1 |

Изобретение относится к области вычислительной техники. Может быть применено для параметрического контроля интегральных схем (ИС). Цель изобретения - повышение быстродействия контроля. Устройство содержит входы 1, коммутатор 2, измеритель 12, многоканальный програм

| Авторское свидетельство СССР 904449, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для параметрического контроля интегральных схем | 1981 |

|

SU985755A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-01-30—Публикация

1985-03-26—Подача