рых являются соответственно первым и вторым входами измерительного блока, первый и второй выходы которого соеднены соответственно с выходами первого и второго компараторов.

2,Устройство по п, 1, о т л и - чающееся тем, что блок управления содержит блок памяти,, соединенный первым, вторым, третьим, четвертым и пятым выходами с одноименными выходами блока управления, адресными входами с выходами счетчика адреса, соединенного установочным входом с вторым входом блока управ ления, счетным входом - с выходом первого элемента И и с входом первого одновибратора, соединенного выходом с шестым выходом блока управления, соединенного первым входом с первым входом первого элемента И, второй вход которого соединен

с выходом генератора тактовых импульсов ,

3.Устройство по п, I, отличающееся тем, что блок анализа брака содержит элемент ИЛИ-НЕ, соединенный выходом с третьим выходом блока анализа брака, соединенно- го первым и вторым выходами соответственно с первыми выходами первого

и второго триггеров, вторые выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, четвертый выход блока анализа брака соединен с вторым выходом второго триггера, соединенного первым входом с первым входом перво- го триггера и с третьим входом блока анализа брака, соединенного вторым

, «

Изобретение относится к контрольно-измерительной технике и может быть использовано при контроле интегральных схем (ИС).

Цель изобретения - расширение . функциональных возможностей устройства путем обеспечения возможности контроля качества охранных (защит- : ных) диодов о

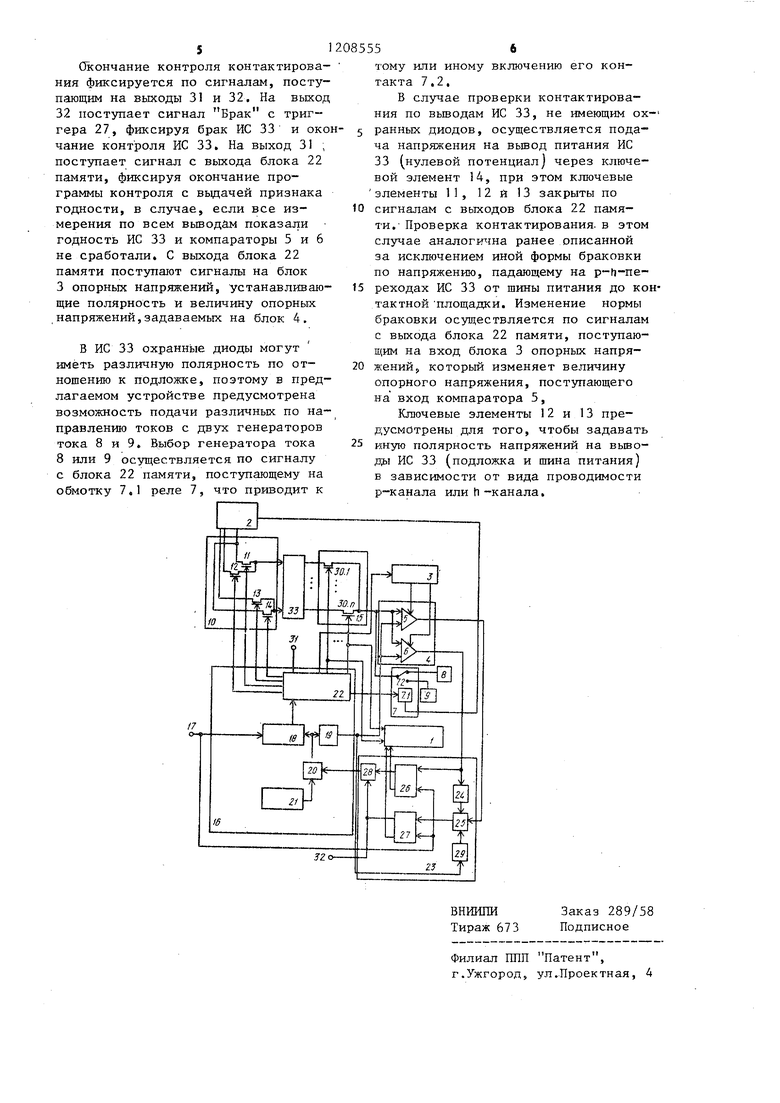

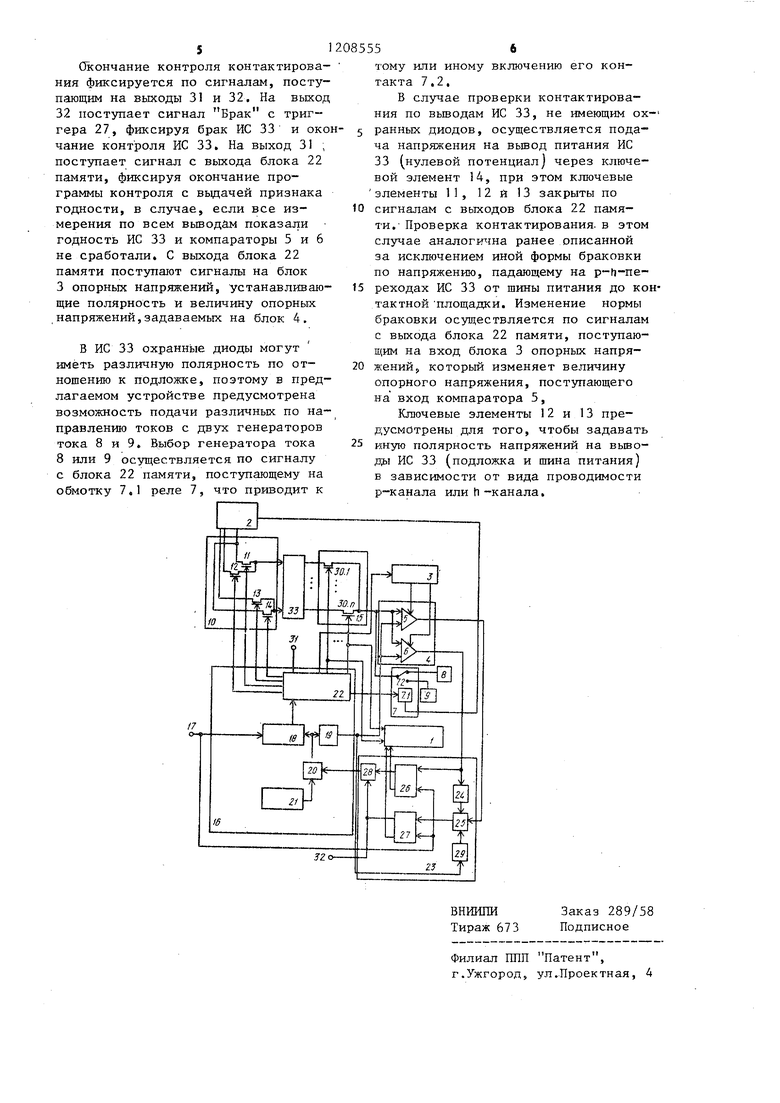

На чертеже приведена блок-схема устройства.

входом с вторым входом первого триггера и с входом элемента НЕ, выход которого соединен с первым входом второго элемента И, соединенного вторым входом с первым входом блока анализа брака, третьим входом через второй одновибратор - с четвертым входом блока анализа брака, выходом - с вторым.входом второго триггера,

Ас Устройство по п. 1, отличающееся тем, что второй коммутационный блок содержит первые ключевые элементы, соединенные выходами с выходом второго коммутационного блока, соединенного информационными входами с информационными входами соответствующих первых ключевых элементов , управляющие входы которых соединены с управляющими входами второго коммутационного блока.

5, Устройство по п, 1, о т л и - чающееся тем, что первьй ком мутационный блок содержит второй и третий коммутационные элементы, соединенные сигнальными входами с третьим сигнальным входом первого коммутационного блока, соединенного первым и вторым сигнальными входами соответственно с сигнальными входами четвертого и пятого ключевых элементов, управляющими входами соответственно - с управляющими входами второго, третьего и четвертого ключе- вьк элементов, первым выходом - с выходами третьего и пятого ключевых элементов, вторым выходом - с выходами второго и четвертого ключевых элементов.

Устройство содержит блок 1 индикации, блок 2 питающих напряжений, блок 3 опорных напряжений, измерительный блок 4, первый 5 и второй 6 комапараторы, реле 7 с обмоткой 7.1 и контактами 7,2, первый 8 и второй 9 генераторы тока, первый комму- тационньвй блок 10, второй II, четвертый 12, пятый 13 и третий 14 ключевые элементы, например реле, второй коммутационный блок 15, блок 16

управления, второй вход 17, счетчик 18 адреса, первый одновибратор, 19, первый элемент 20 И, генератор 21 тактовых импульсов, блок 22 памяти, блок 23 анализа брака, элемент 24 НЕ, второй элемент 25 И, первый 26 и второй 27 триггеры элемент 28 ИЛИ-НЕ, второй одновибратор 29,. первые ключевые элементы 30,1-30.tt, например, реле, четвертый 31 и третий 32 выходы. На чертеже показана также контролируемая ИС 33,

Устройство работает следующим образом.

При поступлении сигнала с входа 17 происходит сброс счетчика 18 адреса триггеров 26 и 27 в блоке 16 управления в исходное состояние. При этом на входы элемента 28 ИЛИ-НЕ поступают логические нули с выходов триггеров 26 и 27, Импульсы с выхода генератора 21 тактовых импульсов через элемент 20 И поступают на входы счетчика 18 адреса и одновибратор 19, поскольку элемент 20 И открыт логической единицей, поступающей с выхода элемента 28 ИЛИ-НЕ при заполнении счетчика 18 адреса, происходит последовательно во времени считьша- ние программ контроля из блока 22 памяти, что обеспечивает се необходимые виды проверок ИС 33.

Первоначально устройство осуществляет контроль падения напряжения (U(, ) на охранных диодах. При этом по сигналам с блока 22 памяти происходит включение ключевого элемента 11 в блоке 10, который передает нулевой потенциал с блока 2 питающих напряжений на подложку ИС 33 ключевые элементы 12, 13 и 14 разомкнуты, В коммутационном блоке 15 по очереди включаются ключевые элементы 30,1 - 30, h соответствующие вьшодам, имеющим охранный диод, и через них осуществляется подача тока заданной величины с генератора 8 тока через контакты 7,2 реле 7 на.соответствующий ИС 33,

При наличии контакта зондов к подложке и вьшоду ИС 33 в результате протекания тока генератора создается падение напряжения на охранном диоде, которое поступает на входы двух компараторов 5 и 6 в измерительном блоке 4, Моменты работы компараторов 5 и 6 определяются стробами, постугающими с выхода од08555

новибратора 19, осуществляющего согласование во времени включения изме рительных цепей и монтажа измерений, В зависимости от значения вы- 5 ходньк сигналов компараторов 5 и 6 блок 23 анализа брака фиксирует результат измерений в триггерах 26 и 27.

Если контактирование выходов уст10 ройства с вьшодами ИС 33 отсутствует, то максимальный сигнал с генератора 8 тока поступает на входы компараторов 5 и 6, которые срабатывают, и на их выходах формируются еди-

15 ничные импульсы в момент строба от одновибратора 19, Триггер 27 не срабатывает, так как элемент 25 И заперт нулевым сигналом с элемента 24 НЕ, Триггер 26 изменяет свое состояние

20 по сигналу с компаратора 6, что приводит к прекращению подачи тактовых импульсов с генератора 21 так- товьк импульсов через элемент 20 И на счетчик 18 адреса и останову рабо25 ты устройства. При этом на блоке 1 индикации светятся индикаторы, ука- зьшающие вид отказа по сигналу с триггера 26 и контролируемый вьшод ИС 33 по сигналам с выходов блока 22

30 памяти. Для исключения гонки сигналов с выходов компараторов 5 и 6 имеется одновибратор 29, который строби- рует элемент 25 И в момент наличия на нем уже сформированных сигналов

с вьсходов компараторов 5 и 6.

При наличии контактирования на негодном охранном диоде в ИС 33 на этом диоде вьщеляется падение напря- . женил больше нормы, задаваемой по техническим условиям,

В этом случае компаратор 6 сра- батывает на его выходе формирует ся логический ноль, который созда45 ет на выходе элемента 24 НЕ логическую единицу. На выходе сработавшего компаратора 5 в момент строба одно- вибратором I9 формируется единичный импульс, который по стробу от

50 одновибратора 29 проходит через элемент 25 И на вход триггера 27, Триггер 27 фиксирует отказ. На блоке 1 индикации индицируется вид отказа по сигналу с триггера 27, С триг55 гера 27 формируется через элемент 28 ИЛИ-НЕ запрещающий сигнал на элемент 20 И, прекращая работу устройства.

Окончание контроля контактирова- кия фиксируется по сигналам, поступающим на выходы 31 и 32. На выход 32 поступает сигнал Брак с триггера 27, фиксируя брак ИС 33 и око чание контроля ИС 33. На выход 31 ; постзгпает сигнал с выхода блока 22 памяти, фиксируя окончание программы контроля с выдачей признака годности, в случае, если все из- мерения по всем вьшодам показали годность ИС 33 и компараторы 5 и 6 не сработали, С выхода блока 22 памяти поступают сигналы на блок 3 опорных напряжений, устанавливаю- щие полярность и величину опорных ,напряжений,задаваемых на блок 4.

В ИС 33 охранные диоды могут иметь различную полярность по от- ношению к подложке, поэтому в предлагаемом устройстве предусмотрена возможность подачи различных по направлению токов с двух генераторов тока 8 и 9. Выбор генератора тока 8 или 9 осуществляется по сигналу с блока 22 памяти, поступающему на обмотку 7.1 реле 7, что приводит к

тому или иному включению его контакта 7,2,

В случае проверки контактирования по вьгоодам ИС 33, не имеющим ох ранных диодов, осуществляется подача напряжения на вьшод питания ИС 33 (нулевой потенциал) через ключевой элемент 14, при этом ключевые элементы 11, 12 и 13 закрыты по сигналам с выходов блока 22 памяти,- Проверка контактирования, в этом случае аналогична ранее описанной за исключением иной формы браковки по напряжению, падающему на p-h-ne- реходах ИС 33 от шины питания до котактной площадки. Изменение нормы браковки осз ществляется по сигналам с выхода блока 22 памяти, постзшаю- щим на вход блока 3 опорных напря- жений который изменяет величину опорного напряжения, поступающего на вход компаратора 5,

Ключевые элементы 12 и 13 предусмотрены для того, чтобы задавать иную полярность напряжений на вьюо- ды ИС 33 (подложка и шина питания) в зависимости от вида проводимости р-канала или h-канала.

ВИНИЛИ

Тираж 673

Заказ 289/58 Подписное

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1348835A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство контроля интегральных схем | 1986 |

|

SU1370634A1 |

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| Устройство параметрического контроля интегральных схем | 1985 |

|

SU1287060A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1430914A1 |

| Устройство контроля интегральных схем | 1982 |

|

SU1049838A1 |

| Устройство для контроля импульсных трансформаторов в составе электронных блоков | 1987 |

|

SU1471158A1 |

| Цифровой стробоскопический преобразователь повторяющихся электрических сигналов | 1986 |

|

SU1386913A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ И ИЗМЕРЕНИЯ УГЛОВОЙ РАСХОДИМОСТИ ЛАЗЕРНОГО ИЗЛУЧЕНИЯ | 0 |

|

SU376851A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-30—Публикация

1984-07-05—Подача