жения функций в ряд Тейлора, (2т - 1) умножителей 3, комбинационный сумматор 4, первый вычитатель 5, сдвига- тель 6, второй вычитатель 7, блок 8 приоритетного формирования нулей, п элементов 9 задержки, где п - разрядность переменных, п схем 10 сравнения, два коммутатора 11 и 12, элемент ИЛИ 13, блок 14 формирования

1 Изобретение относится к цифровой

вычислительной технике и может быть « использовано в составе универсальных

или специализированных вычислительных машин для нахождения значений прямых и обратных функций.

Цель изобретения - расширение функциональных возможностей устройства за счет вычисления помимо прямых и обратных функций.

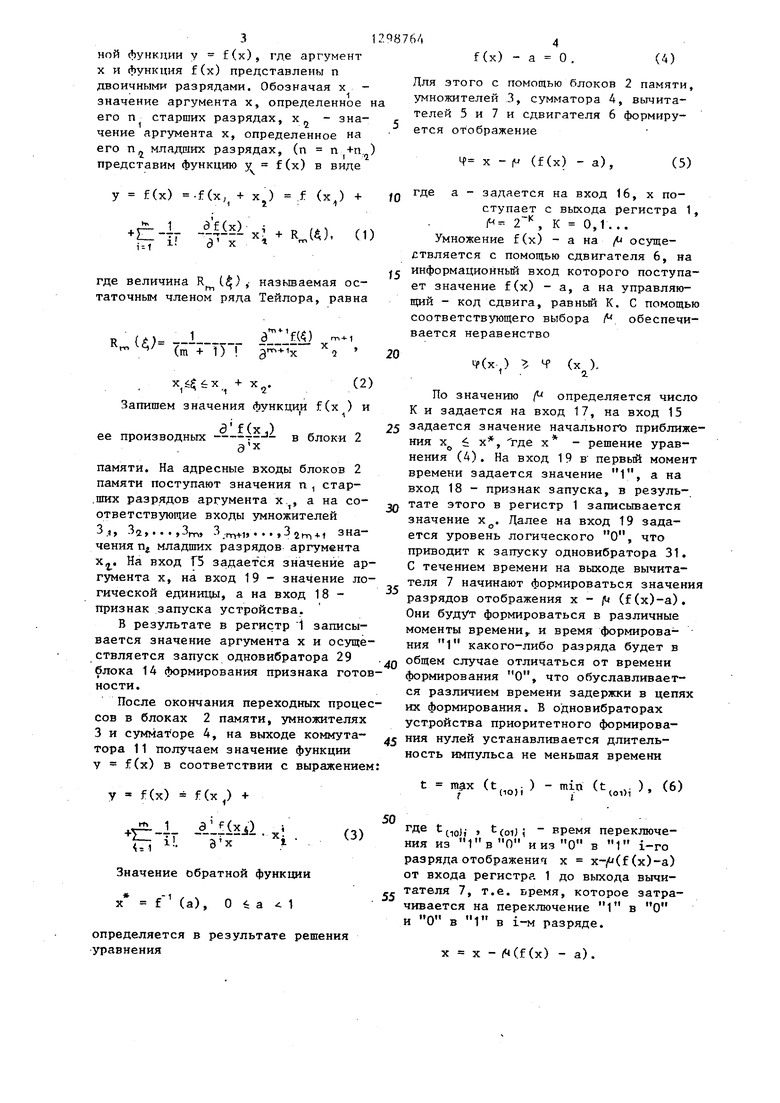

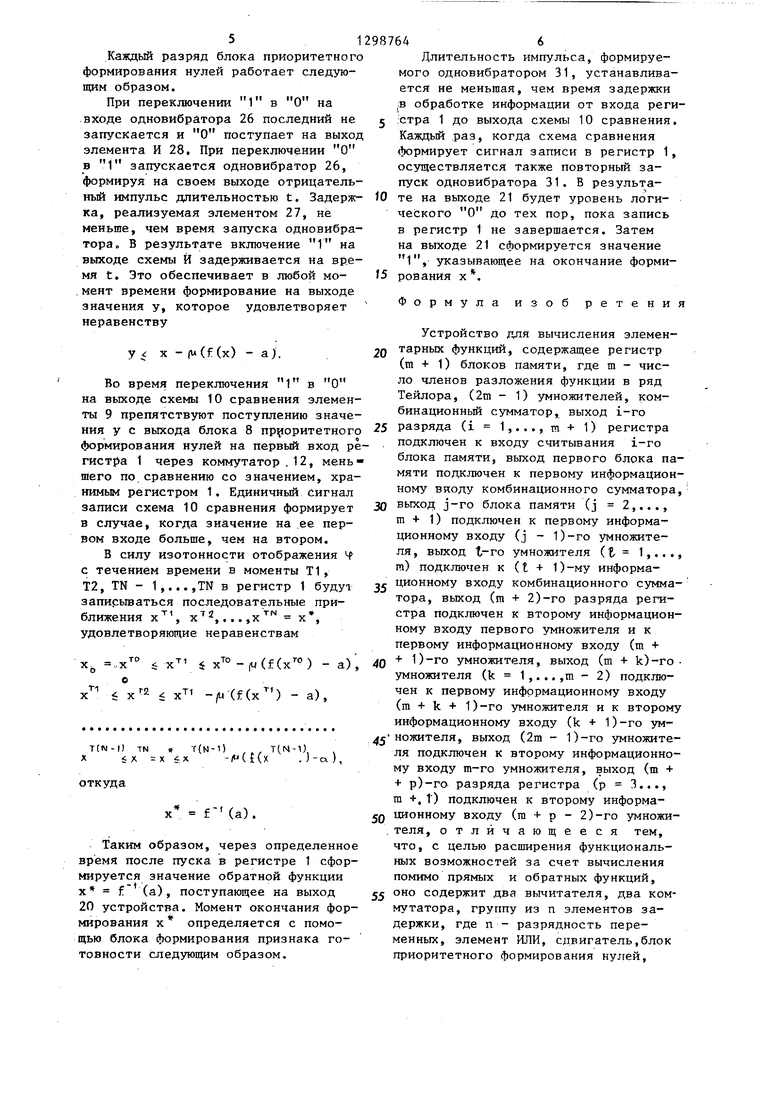

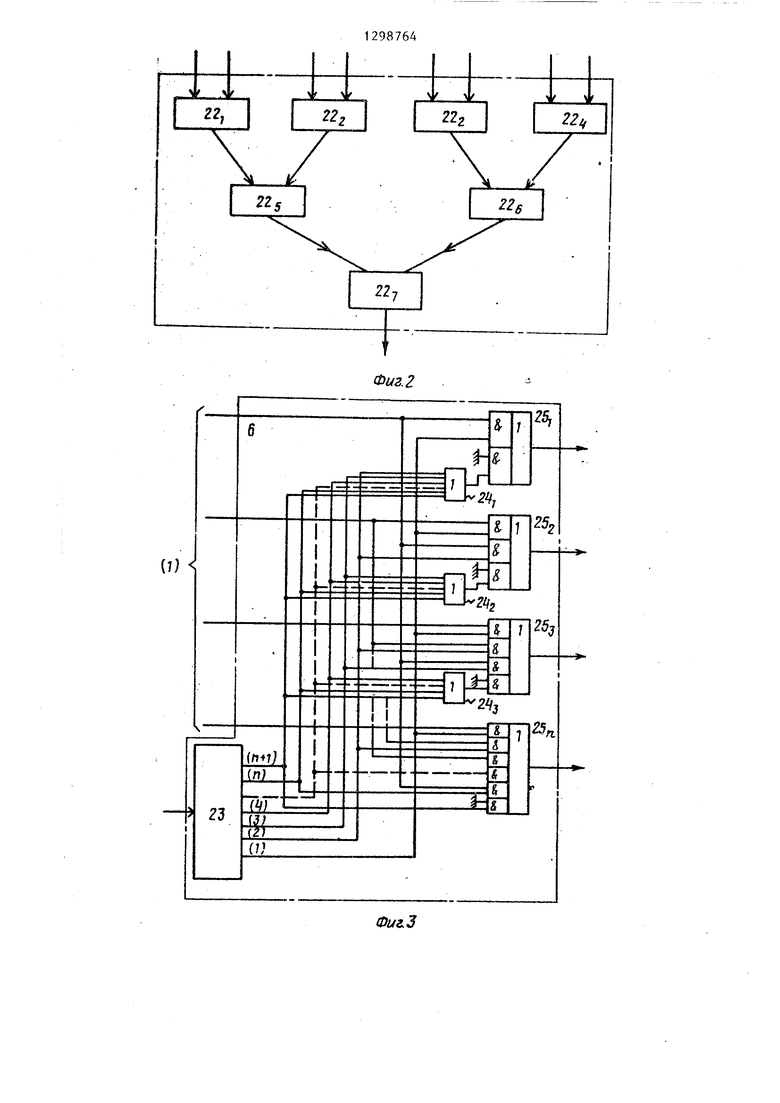

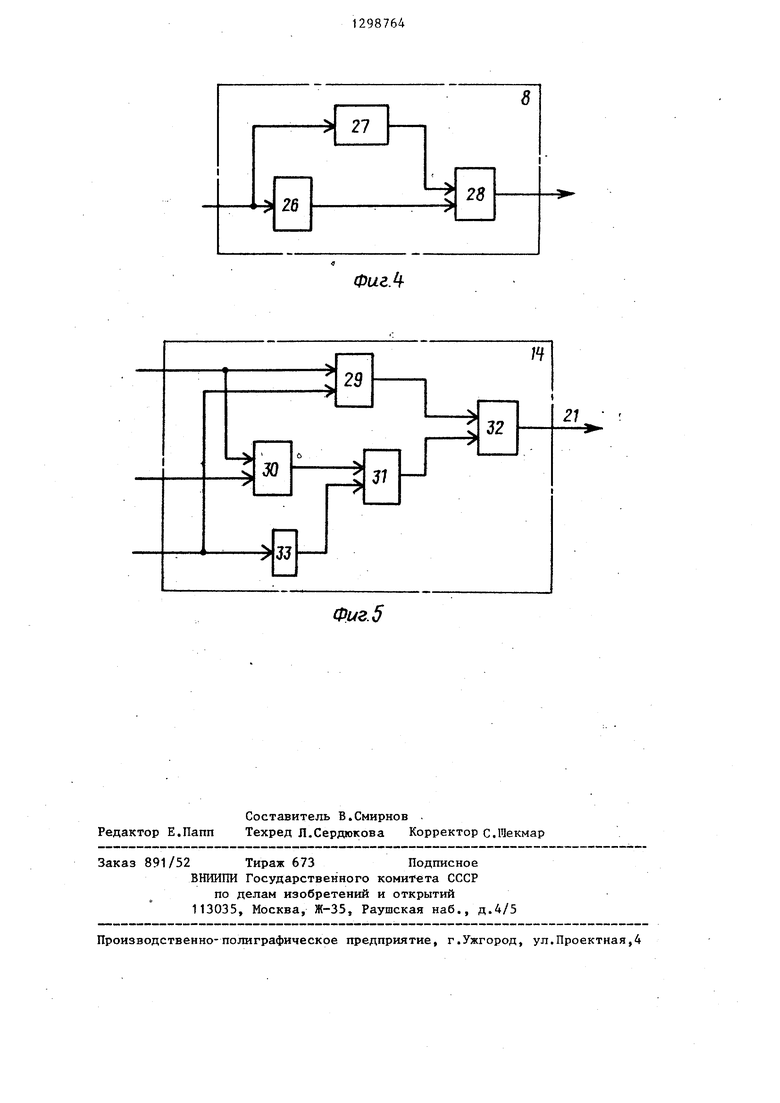

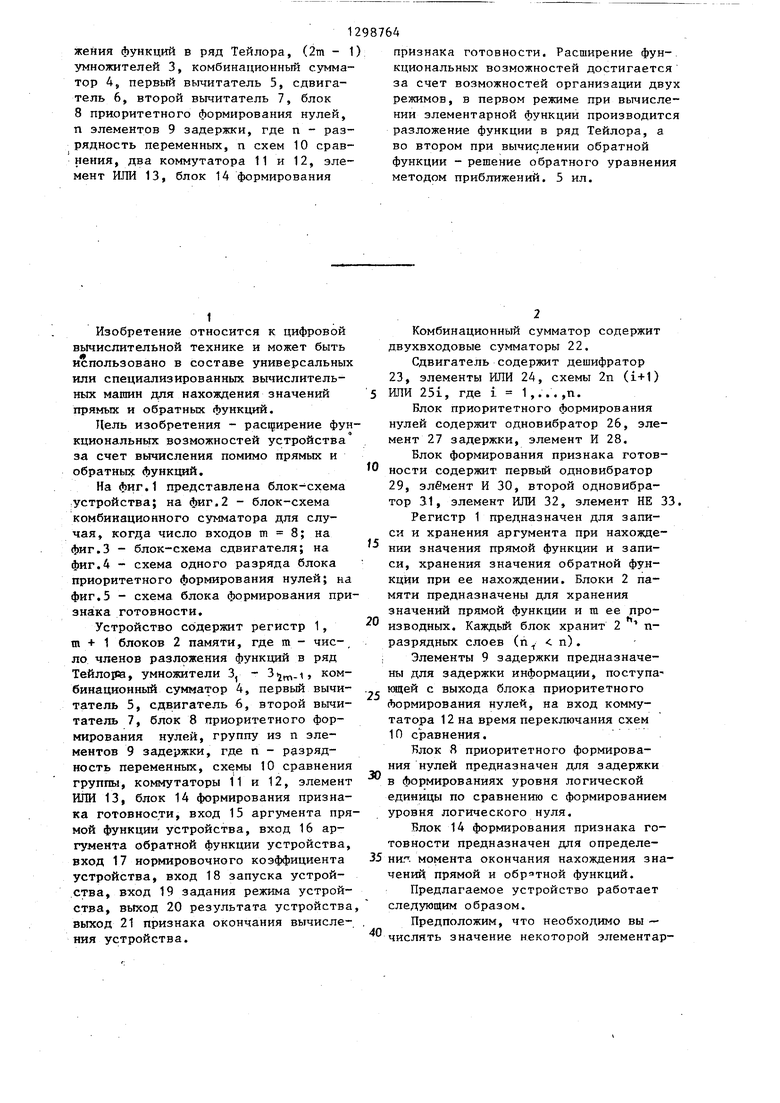

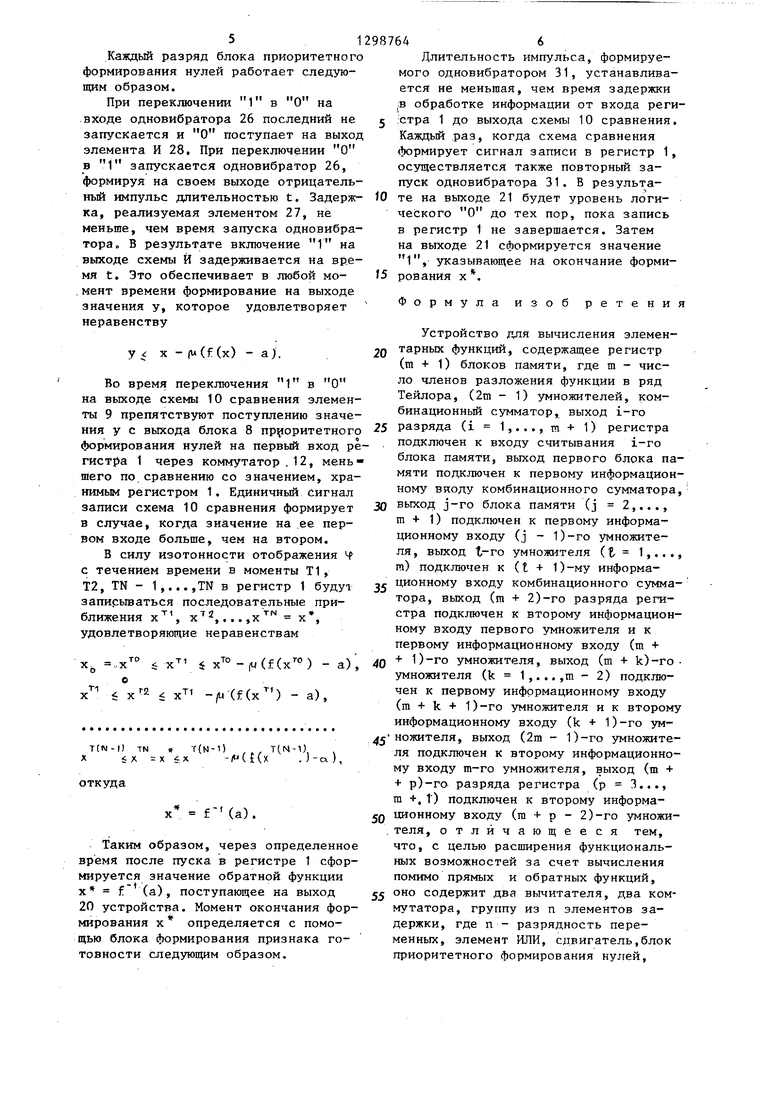

На фиг.1 представлена блок-схема устройства; на фиг.2 - блок-схема комбинационного сумматора для случая, когда число входов m 8; на фиг.З - блок-схема сдвигателя; на фиг.4 - схема одного разряда блока приоритетного формирования нулей; на фиг.З - схема блока формирования признака готовности.

Устройство содержит регистр 1, та + 1 блоков 2 памяти, где m - чис-, ло членов разложения функций в ряд Тейлора, умножители 3, - .i, комбинационный сумматор 4, первый вычитатель 5, сдвигатель 6, второй вычитатель 7, блок 8 приоритетного формирования нулей, группу из п элементов 9 задержки, где п - разрядность переменных, схемы 10 сравнения группы, коммутаторы 11 и 12, элемент ИЛИ 13, блок 14 формирования признака готовности, вход 15 аргумента прямой функции устройства, вход 16 аргумента обратной функции устройства, вход 17 нормировочного коэффициента устройства, вход 18 запуска устрой- .ства, вход 19 задания режима устройства, выход 20 результата устройства выход 21 признака окончания вычисле- ния устройства.

признака готовности. Расширение функциональных возможностей достигается за счет возможностей организации двух режимов, в первом режиме при вычислении элементарной функции производится разложение функции в ряд Тейлора, а во втором при вычислении обратной функции - решение обратного уравнения методом приближений, 5 ил.

o

5

0

5

0

5

0

Комбинационный сумматор содержит двухвходовые сумматоры 22.

Сдвигатель содержит дешифратор 23, элементы ИЛИ 24, схемы 2п (i+1) ИЛИ 251, где i 1,...,п.

Блок Приоритетного формирования нулей содержит одновибратор 26, элемент 27 задержки, элемент И 28.

Блок формирования признака готовности содержит первьй одновибратор 29, элемент И 30, второй одновибратор 31, элемент ИЛИ 32, элемент НЕ 33.

Регистр 1 предназначен для записи и хранения аргумента при нахождении значения прямой функции и записи, хранения значения обратной функции при ее нахождении. Блоки 2 памяти предназначены для хранения значений прямой функции и m ее производных. Кажд,ьй блок хранит 2 п- разрядных слоев (п п).

Элементы 9 задержки предназначены для задержки информации, поступа- няцей с выхода блока приоритетного (Нормирования нулей, на вход коммутатора 12 на время переключания схем 10 сравнения.

Блок Я приоритетного формирования нулей предназначен для задержки в формированиях уровня логической единицы по сравнению с формированием уровня логического нуля.

Блок 14 формирования признака готовности предназначен для определение, момента окончания нахождения значений прямой и обратной функций.

Предлагаемое устройство работает следующим образом.

Предположим, что необходимо вы - числять значение некоторой элементарной функции у f(x), где аргумент X и функция f(x) представлены п двоичными разрядами. Обозначая х - значение аргумента х, определенное его п старших разрядах, х - значение аргумента х, определенное на его Пл младиих разрядах, (п п |+п представим функцию у f (х) в виде

у f(x) .f(Х; +

Xj) f (

-.)

R(}, (1)

где величина R ($), назьшаемая осm

таточным членом ряда Тейлора, равна

U

1.

Tiii +

ТУТ

X 6 X + X

(4)

х

X

m-t-l

2

Запишем значения ФУНКЦИИ f(x ) и

1

a f(x,) „

- - в блоки 2

производных

Э х

памяти. На адресные входы блоков 2 памяти поступают значения п , стар- .ших разрядов аргумента х., а на соответствующие входы умножителей

J.« - Z t Jm - .rn-f-i ««-- йн -и на- чения n младпгах разрядов аргумента х. На вход Г5 задаемся значение аргумента X, на вход 19 - значение логической единицы, а на вход 18 - признак запуска устройства.

В результате в регистр i записывается значение аргумента х и осуществляется запуск одновибратора 29 блока 14 формирования признака готовности.

После окончания переходных процессов в блоках 2 памяти, умножителях 3 и сумматоре 4, на выходе коммутатора 11 получаем значение функции у f(x) в соответствии с выражением

У f(x)

f(xp +

1

э

xj)

Значение обратной функции

..-1

f (а), О 4 а 1

определяется уравнения

в результате решения

f(x) - а

4

0.

(4)

Для зтого с помощью блоков 2 памяти, умножителей 3, сумматора 4, вычита- телей 5 и 7 и сдвигателя 6 формируется отображение

4 X - 1 (f(х) - а).

(5)

где а - задается на вход 16, х поступает с выхода регистра 1, К 0,1...

(М 2

-к

Умножение f(x) - а на /tj осуществляется с помощью сдвигателя 6, на информационньй вход которого поступает значение f(x) - а, а на управляющий - код сдвига, равньй К. С помощью соответствующего выбора f, вается неравенство

обеспечи

:

30

35

40

20

Ч-Сх)

Ч).

По значению / определяется число К и задается на вход 17, на вход 15

25 задается значение начального приближения х X, где X - решение уравнения (4) . На вход 19 в первый момент времени задается значение 1, а на вход 18 - признак запуска, в результате этого в регистр 1 записьгоается значение х. Далее на вход 19 задается уровень логического О, что приводит к запуску одновибратора 31. С течением времени на выходе вычита- теля 7 начинают формироваться значения разрядов отображения х - |U (f(x)-a). Они будут формироваться в различные моменты времени,, и время формирования 1 какого-либо разряда будет в общем случае отличаться от времени формирования О, что обуславливается различием времени задержки в цепях их формирования. В одновибраторах устройства приоритетного формирова45 ния нулей устанавливается длительность импульса не меньшая времени

t f (,o,i

min i

(o,„). (6)

55

50

где t

CioJi

t(oi;i время переключения из в 1 i-ro разряда отображения х x-/f(f(x)-a) от входа регистр. 1 до выхода вычи- тателя 7, т.е. время, которое затрачивается на переключение 1 в О и О в 1 в i-M разряде.

X X - ((f (х) - а).

5

Каждый разряд блока приоритетног формирования нулей работает следующим образом.

При переключении 1 в О на входе одновибратора 26 последний не запускается и О поступает на выхо элемента И 28, При переключении О

в 1 запускается одновибратор 26, формируя на своем выходе отрицатель- ньй импульс длительностью t. Задержка, реализуемая элементом 27, не меньше, чем время запуска одновибра- тора В результате включение 1 на выходе схемы И задерживается на время t. Это обеспечивает в любой мо- .мент времени формирование на выходе значения у, которое удовлетворяет неравенству

у X - (u(f (х) - а).

10

Длительность импульса, формируемого одновибратором 31, устанавливается не меньшая, чем время задержки В обработке информации от входа реги- :стра 1 до выхода схемы 10 сравнения. Каждый раз, когда схема сравнения (Ъормирует сигнал записи в регистр 1, осуществляется также повторный запуск одновибратора 31. В результате на выходе 21 будет уровень логического О до тех пор, пока запись в регистр 1 не завершается. Затем на выходе 21 сформируется значение

111 ч

ts

, указывающее на окончание формирования X .

Формула изоб ретения

Устройство для вычисления элемен- 2Q тарных функций, содержащее регистр

(т + 1) блоков памяти, где m - число членов разложения функции в ряд Тейлора, (2т - 1) умножителей, комбинационный сумматор, выход i-ro

ния у с выхода блока 8 приоритетного 25 разряда (i 1,..., m + 1) регистра формирования нулей на первый вход ре- подключен к входу считывания i-ro гистра 1 через коммутатор . 12, мень- ° памяти, выход первого блока памяти подключен к первому информационно время переключения 1 в О на выходе схемы 10 сравнения элементы 9 препятствуют поступлению значешего по сравнению со значением, хранимым регистром 1. Единичньш Сигнал записи схема 10 сравнения формирует в случае, когда значение на ее первом входе больше, чем на втором.

В силу изотонности отображения Ч с течением времени в моменты Т1, Т2, TN - 1,...,TN в регистр 1 будут записываться последовательные приближения , х,... ,х X, удовлетворяющие неравенствам

ному вподу комбинационного сумматора,

30 выход j-ro блока памяти (j 2,..., m + 1) подключен к первому информационному входу (J - 1)-го умножителя, выход t-ro умножителя (t 1,..., га) подключен к (t + 1)-му информа,, ционному входу комбинационного сумматора, выход (т + 2)-го разряда регистра подключен к второму информационному входу первого умножителя и к первому информационному входу (ш +

T(N-) ТГ4 r{N-l)

X X X

-/f(Kx

T(N-4),

откуда

(а).

Таким образом, через определенное время после пуска в регистре 1 сформируется значение обратной функции X f (а), поступающее на выход 20 устройства. Момент окончания формирования X определяется с помощью блока формирования признака готовности Следующим образом.

Длительность импульса, формируемого одновибратором 31, устанавливается не меньшая, чем время задержки В обработке информации от входа реги- :стра 1 до выхода схемы 10 сравнения. Каждый раз, когда схема сравнения (Ъормирует сигнал записи в регистр 1, осуществляется также повторный запуск одновибратора 31. В результате на выходе 21 будет уровень логического О до тех пор, пока запись в регистр 1 не завершается. Затем на выходе 21 сформируется значение

111 ч

, указывающее на окончание формирования X .

Формула изоб ретения

Устройство для вычисления элемен- тарных функций, содержащее регистр

(т + 1) блоков памяти, где m - число членов разложения функции в ряд Тейлора, (2т - 1) умножителей, комбинационный сумматор, выход i-ro

ному вподу комбинационного сумматора,

выход j-ro блока памяти (j 2,..., m + 1) подключен к первому информационному входу (J - 1)-го умножителя, выход t-ro умножителя (t 1,..., га) подключен к (t + 1)-му информационному входу комбинационного сумматора, выход (т + 2)-го разряда регистра подключен к второму информационному входу первого умножителя и к первому информационному входу (ш +

О-го умножителя, выход (т + k)-ro умножителя (k 1,...,m - 2) подключен к первому информационному входу (т + k + 1)-го умножителя и к второму информационному входу (k + 1)-го умножителя, выход (2т - 1)-го умножителя подключен к второму информационному входу т-го умножителя, выход (т + + р)-го разряда регистра (р 3..., +, 1) подключен к второму информационному входу (ш + р - 2)-го умножи- теля, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычисления помимо прямых и обратных функций,

оно содержит два вычитателя, два коммутатора, группу из п элементов задержки, где п - разрядность переенных, элемент ИЛИ, сдвигатель,блок приоритетного формирования нулей.

группу из п схем сравнения, блок формирования признака готовности, вход аргумента прямой функции устройства подключен к первому информационному входу первого коммутатора, вход ар- гумента обратной функции устройства подключен к первому информационному входу первого вычитателя, вход нормированного коэффициента устройства подключен к входу кода сдвига сдвигателя, вход задания режима устройства подключен к управлякядим входам первого и второго коммутаторов и к первому входу блока формирования признака готовности, выход первого коммута-IS ка формирования признака готовности,

третий вход блока формирования признака готовности подключен к входу сброса первого одновибратора и к входу элемента НЕ блока формирования признака готовности, выход элемента И и выход элемента НЕ блока формирования признака готовности подключены соответственно к входам запуска и сброса второго одновибратора блока 25 формирования признака готов ности, вы- ;соды первого и второго одновибрато- ров блока формирования признака готовности подключены соответственно к первому и второму входам элемента ИЛИ блока формирования признака готовности, выход элемента ИЛИ блока формирования признака готовности подключен к выходу блока формирования признака готовности, при этом блок приоритеттора подключен к информационному входу регистра, выход комбинационного сумматора подключен к второму ин- фор14ационному входу первого вычитателя и к первому информационному входу 20 второго коммутатора, выход первого вычитателя подключен к информационному входу сдвигател5{, выход которого подключен к первому информационному . входу второго вычитателя, вход запуска устройства подключен к первому входу элемента ИЛИ и к второму входу блока формирования признака готовности, выход второго вычитателя под- ключей к информационному входу блока 30 приоритетного формирования нулей, выход которого подключен к входам элементов задержки группы и к первым входам схем сравнения группы, выходы

элементов задержки группы объединены 35 кого формирования нулей содержит п и подключены к второму информационно- одновиб1 аторов, п элементов задержки, му входу первого коммутатора, выходы схем сравнения группы подключены к. третьему входу блока формирования

п элементов И, q-й разряд входа блока приоритетного формирования нулей подключен к входу q-ro одновибратопризнака готовности и к второму входу40 ра и q-ro элемента задержки блока

элемента ИЛИ, выход которого подключен к йходу считьгоания регистра, выход регистра подключен к второму информационному входу второго коммутатора, к второму информационному входу второго вычитателя и к вторым входам схем сравнения группы, выход второго коммутатора подключен к выходу результата устройства, выход третьего коммутатора подключен к выходу признака окончания вычисления устройства, при этом блок формирования признака готовности содержит два одновибратора, элемент И, элемент ИЛИ, элемент НЕ, первый вход блока формирования признака готовности подключен к входу запуска первого одновибратора и к первому входу элемента И блока формирования признака готовности, второй вход блока формирования признака готовности подключен к второму входу элемента И блокого формирования нулей содержит п одновиб1 аторов, п элементов задержки,

п элементов И, q-й разряд входа блока приоритетного формирования нулей подключен к входу q-ro одновибратоприоритетного формирования нулей, выходы которых подключены соответственно к первому и второму входам q-ro элемента И блока приоритетного 45 формирования нулей, выход q-ro элемента И блока приоритетного формирования нулей подключен к q-му разряду выхода блока приоритетного формирования нулей.

±

22,

1298764

j

Фиг. 2

Фиг. 2

Фиг. 5

Редактор Е.Папп

Составитель В.Смирнов .

Техред Л.Сердюкова Корректор С.Шекмар

Заказ 891/52 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

ФигЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1254504A1 |

| Операционное устройство | 1987 |

|

SU1481740A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для вычисления тригонометрических функций | 1987 |

|

SU1427362A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для деления | 1984 |

|

SU1242935A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе универсальных или специализированных вычислительных, машин для нахождения значений прямых и обратных функций. Цель изобретения - расширение функциональ ных возможностей устройства за счет вычисления прямых и обратных функций. Цель достигается тем, что устройство содержит регистр 1, (т + 1) блоков 2 памяти, где m - число членов разло(Л с tsD CD ОО О5 Фиг-1

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электройное моделирование | |||

| - Киев: Наукова думка, 1983, № 4, с,65, рис.5. | |||

Авторы

Даты

1987-03-23—Публикация

1985-03-11—Подача