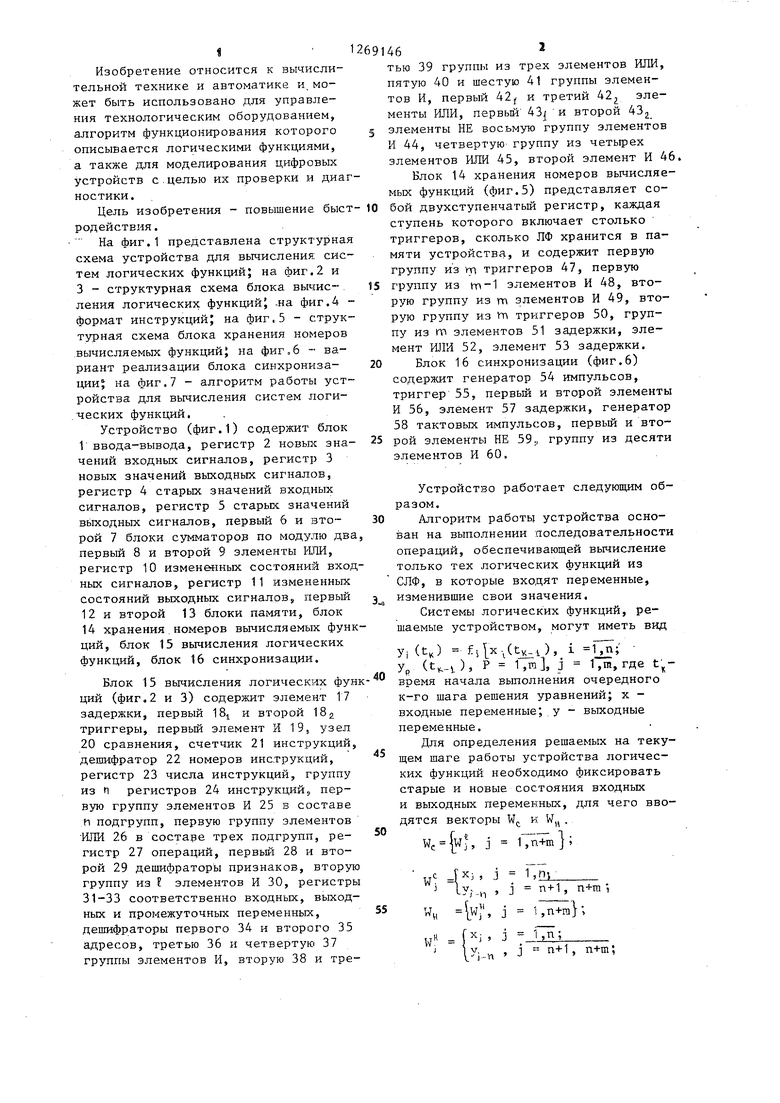

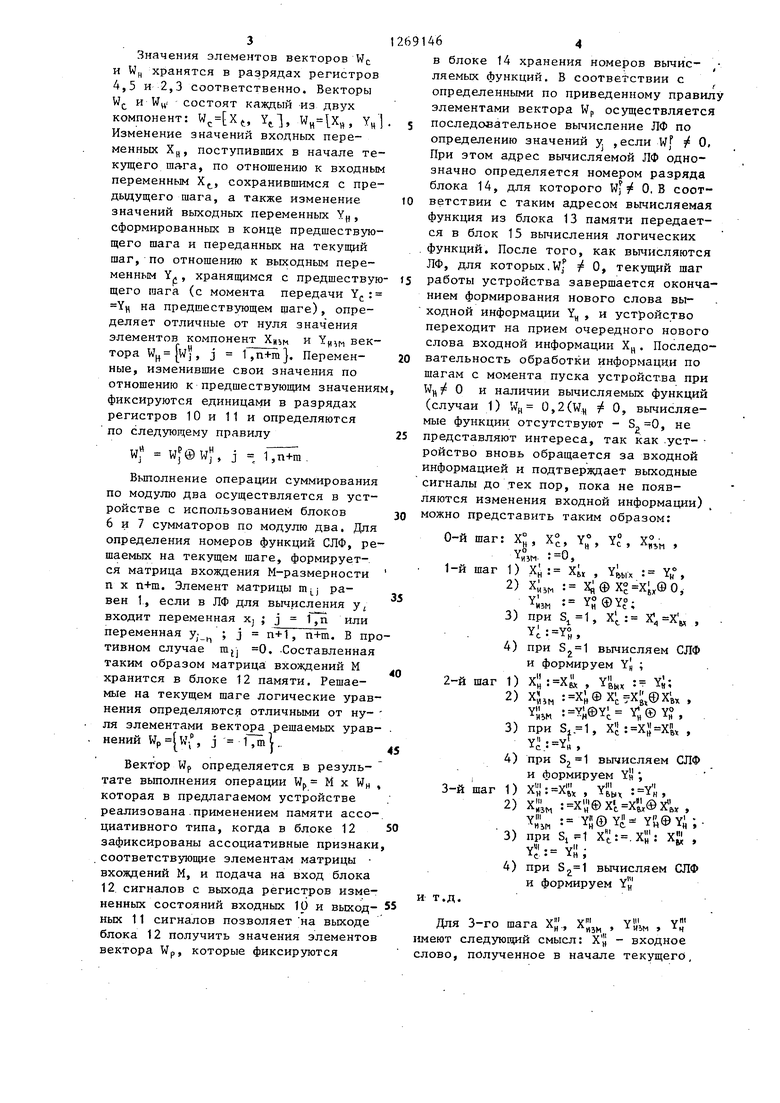

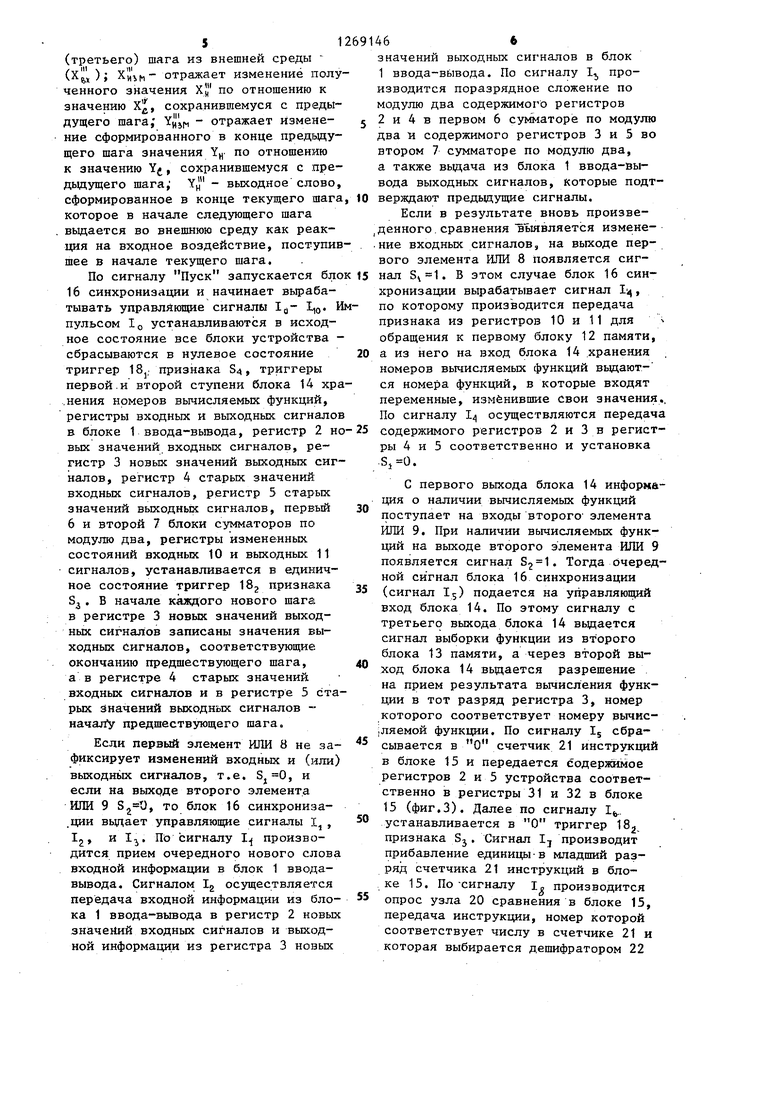

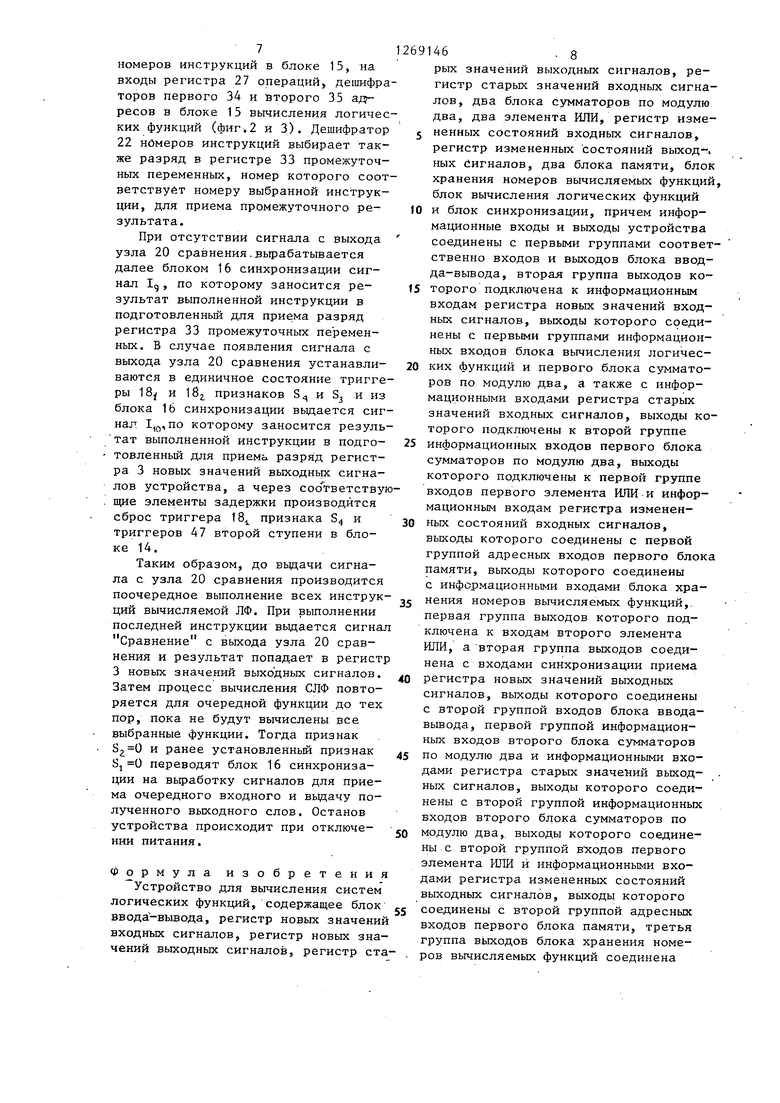

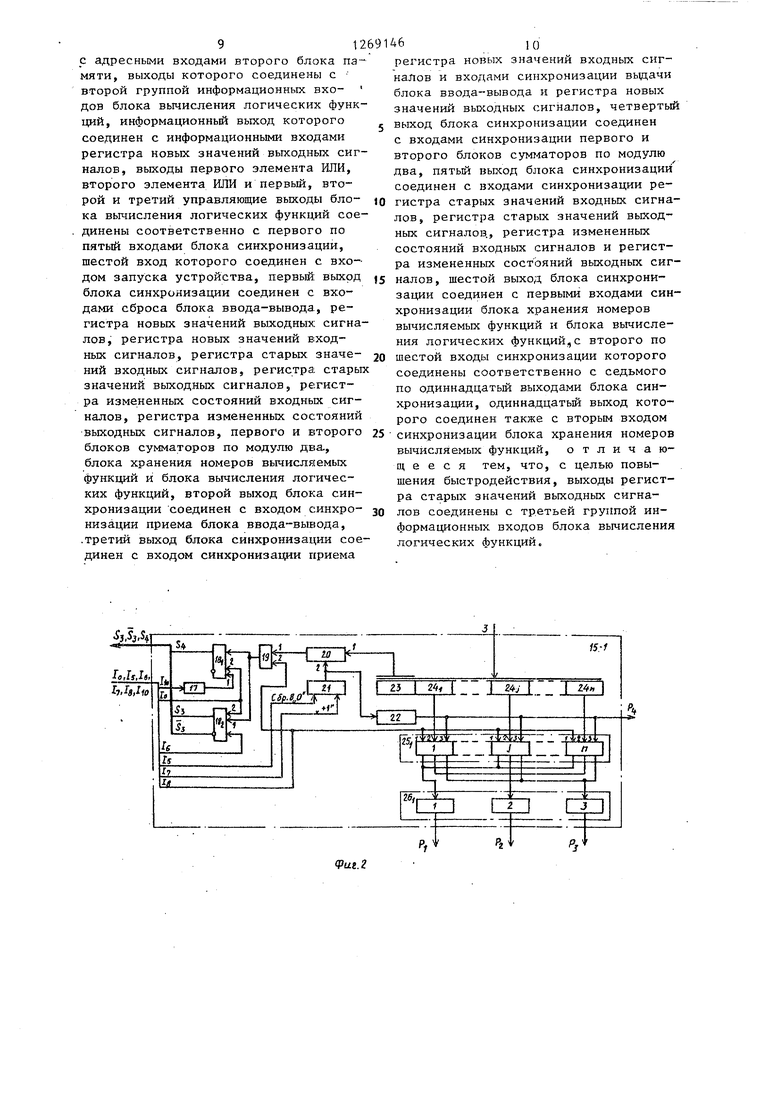

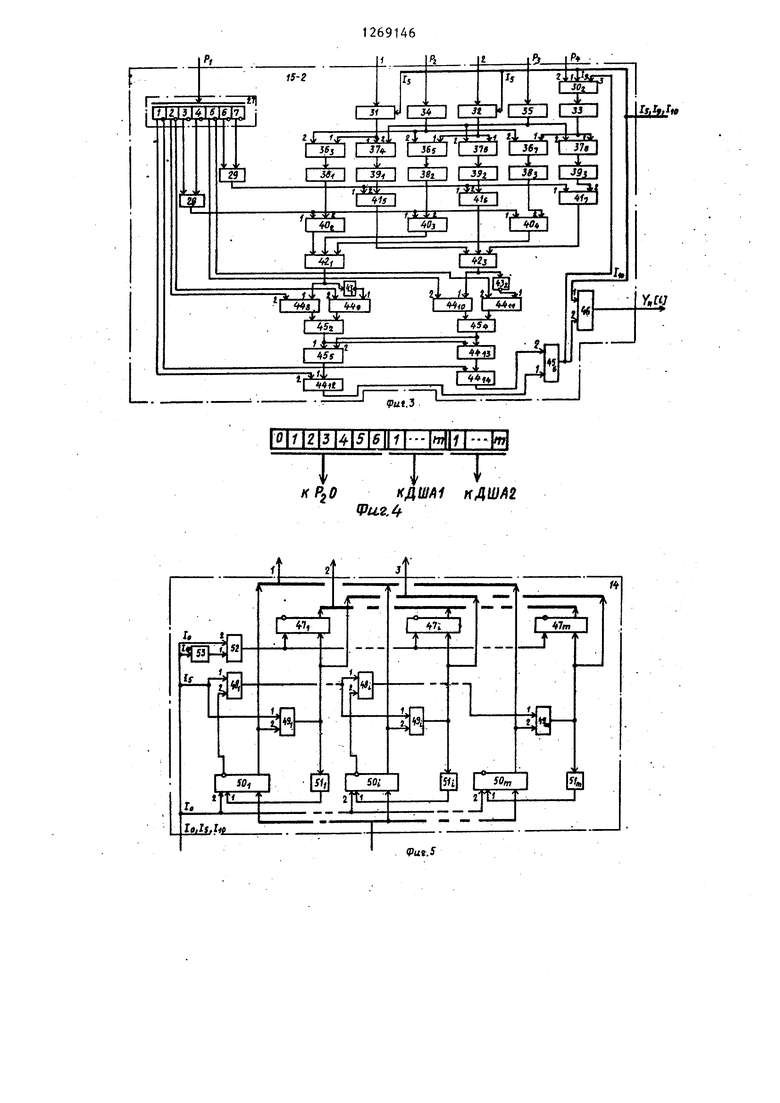

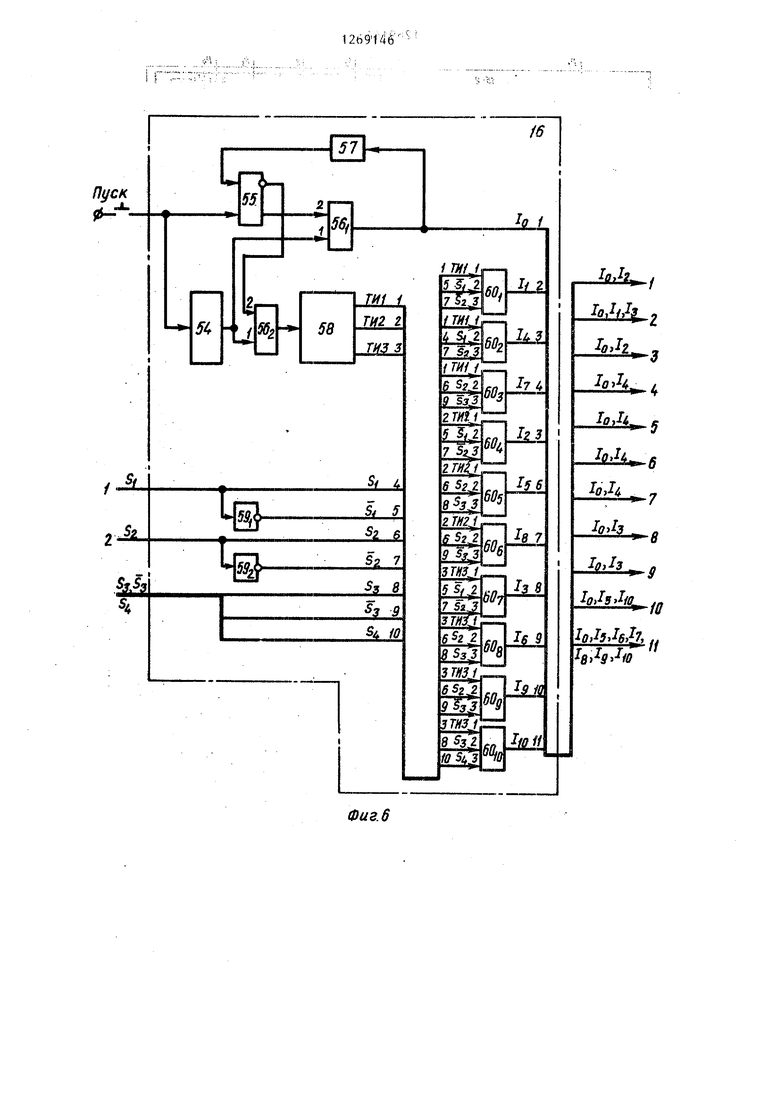

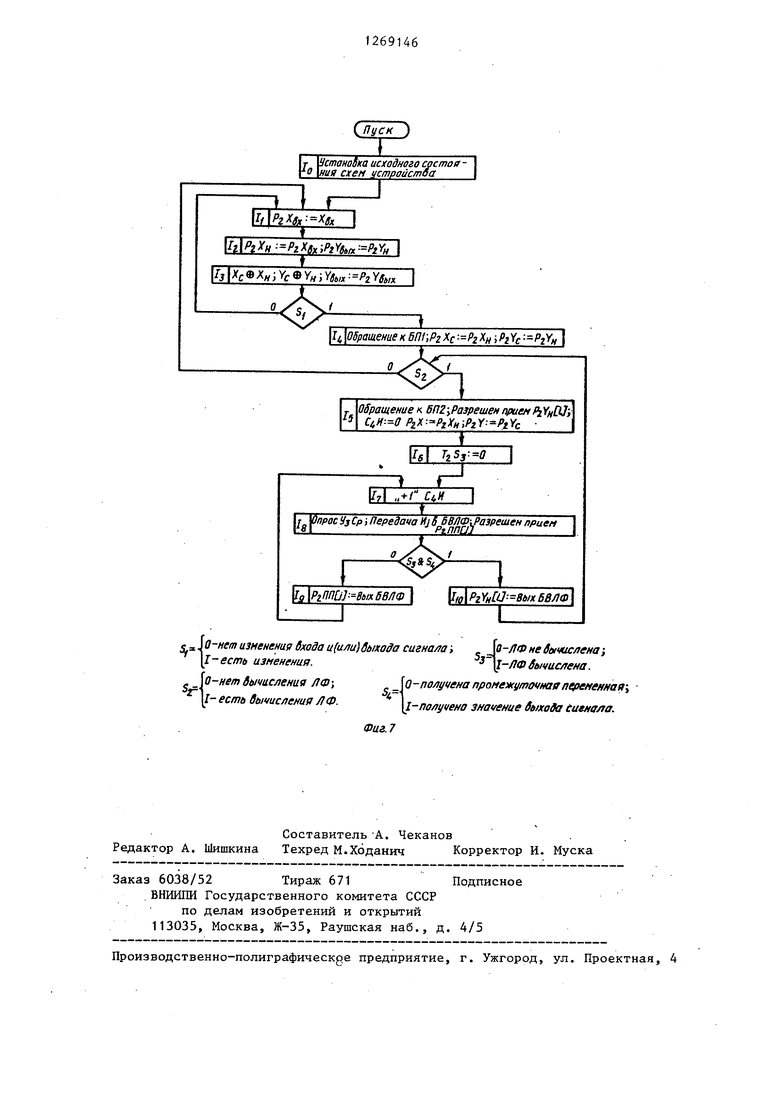

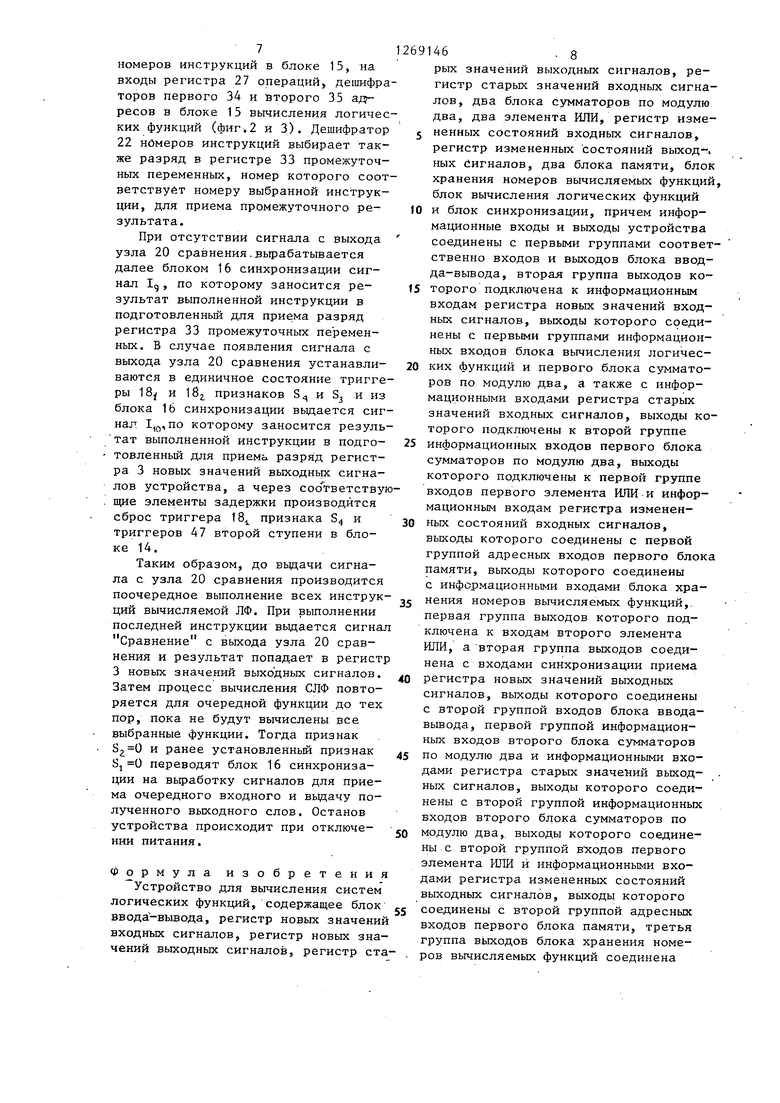

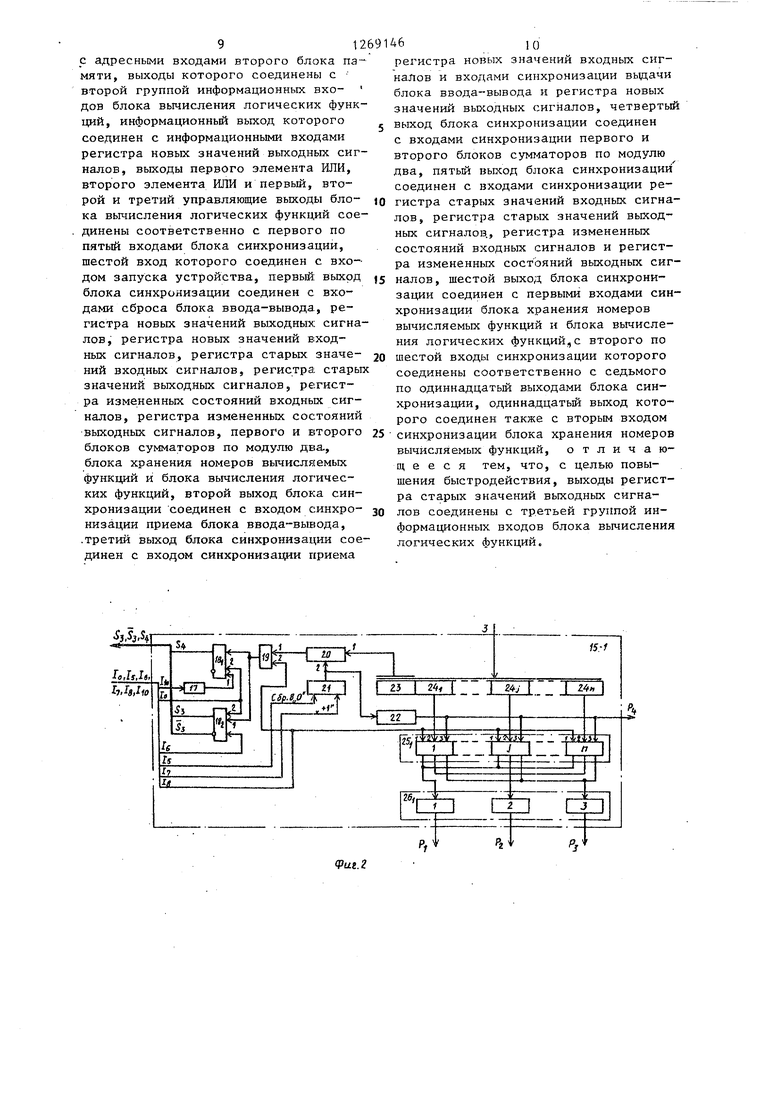

Изобретение относится к вычислительной технике и автоматике и может быть использовано для управления технологическим оборудованием, алгоритм функционрфования которого описывается логическими функциями, а также для моделирования цифровых устройств с.целью их проверки и диаг ностики. Цель изобретения - повышение быст родействия. На фиг.1 представлена структурная схема устройства для вычисления систем логических функций; на фиг.2 и 3 - структурная схема блока вычисления логических функций ,на фиг.4 формат инструкций; на фиг,5 - структурная схема блока хранения номеров .вычисляемых функций} на фиг,6 - вариант реализации блока синхронизации; на фиг.7 - алгоритм работы устройства для вычисления систем логи.ческих функций. Устройство (фиг.1) содержит блок 1 ввода-вывода, регистр 2 новьпс значений входных сигналов, регистр 3 новых значений выходных сигналов, регистр 4 старых значений входных сигналов, регистр 5 старых значений вьпсодных сигналов, первый 6 и зторой 7 блоки сумматоров по модулю два первый 8 и второй 9 элементы КОИ, регистр 10 измененных состояний вход ных сигналов, регистр 11 измененных состояний выходных сигналов, первьш 12 и второй 13 блоки памяти, блок 14 хранения номеров вычисляемых функ ций, блок 15 вычисления логических функций, блок 16 синхронизации. Блок 15 вычисления логических фун ций (фиг,2 и 3) содержит элемент 17 задержки, первый 18, и второй ISj триггеры, первьш элемент И 19, узел 20 сравнения, счетчик 21 инструкций, дешифратор 22 номеров инструкций, регистр 23 числа инструкций, группу из fi регистров 24 инструкций, первую группу элементов И 25 в составе и подгрупп, первую группу элементов ИЖ 26 в составе трех подгрупп, регистр 27 операций, первьй 28 и второй 29 дешифраторы признаков, вторую группу из элементов И 30, регистры 31-33 соответственно входных, выходных и промежуточных переменных, дешифраторы первого 34 и второго 35 адресов, третью 36 и четвертую 37 группы элементов И, вторую 38 и тре462тью 39 группы из трех элементов ИЛИ, пятую 40 и шестую 41 группы элементов И, первый 42 и третий 42 элементы ИЛИ, первый второй 43 элементы НЕ восьмую группу элементов И 44, четвертую группу из четырех элементов ИЛИ 45, второй элемент И 46. Блок 14 хранения номеров вычисляемых функций (фиг.5) представляет собой двухступенчатый регистр, каждая ступень которого включает столько триггеров, сколько ЛФ хранится в памяти устройства, и содержит первую группу из УТ1 триггеров 47, первую группу из try-l элементов И 48, вторую группу из т элементов И 49, вторую группу из VT триггеров 50, группу из m элементов 51 задержки, элемент ИЛИ 52, элемент 53 задержки. Блок 16 синхронизации (фиг.6) содержит генератор 54 импульсов, триггер 55, первый и второй элементы И 56, элемент 57 задержки, генератор 58 тактовых импульсов, первый и второй элементы НЕ 59,, группу из десяти элементов И 60, Устройство работает следующим образом. Алгоритм работы устройства основан на выполнении последовательности операций, обеспечивающей вычисление только тех логических функций из СЛФ, в которые входят переменные, изменившие свои значения. Системы логических функций, решаемые устройством, могут иметь вид У (Ьк) ), i 1jJ}; Ур (t.-i) Р 1.m, j 1,m, где f время начала выполнения очередного к-го шага решения уравнений; х входные переменные; у - выходные переменные. Для определения решаемых на текущем шаге работы устройства логических функций необходимо фиксировать старые и новые состояния входных и выходных переменных, для чего вводятся векторы W,. и W.. . Wc w-, j 1,n+m}; JXj , j 1, j n-bl, n-fm i 1 ,n+m}; IJnj П+1, n+m; 3 Значения элементов векторов W(. и Ыц хранятся в разрядах регистров 4,5 и 2,3 соответственно. Векторы W и состоят каждый из двух компонент: (,, Ytl. „ Хн, Уц Изменение значений входных переменных Хц, поступивших в начале текущего шага, по отношению к входным переменным Х, сохранившимся с предьщущего шага, а также изменение значений выходных переменных Y, сформированных в конце предшествующего шага и переданных на текущий шаг, по отношению к выходным переменным Y,, , хранящимся с предшествую щего шага (с момента передачи Y(.: YH на предшествующем шаге), определяет отличные от нуля значения элементов компонент XHIM и ., вектора , j 1 ,n+m}. Переменные, изменившие свои значения по отношению к предшествующим значения фиксируются единицами в разрядах регистров 10 и 11 и определяются по следующему правилу Выполнение операции суммирования по модулю два осуществляется в устройстве с использованием блоков 6 и 7 сумматоров по модулю два. Для определения номеров функций СЛФ, ре шаемых на текущем шаге, формируется матрица вхождения М-размерности п X n+m. Элемент матрицы равен 1, если в ЛФ для вычисления у входит переменная Xj ; j l7n или переменная у- ; j п+1, n+m. В пр тивном случае 0, -Составленная таким образом матрица вхождений М хранится в блоке 12 памяти. Решаемые на текущем шаге логические урав нения определяются отличными от нуля элементами вектора решаемых урав нений , j 1,mi.. Вектор Wp определяется в результате выполнения операции Wp М х WH которая в предлагаемом устройстве реализована.применением памяти ассоциативного типа, когда в блоке 12 зафиксированы ассоциативные признаки соответствующие элементам матрицы вхождений М, и подача на вход блока 12 сигналов с выхода регистров измененньпс состояний входных 10 и выходных 11 сигналов позволяет на выходе блока 12 получить значения элементов вектора Wp, которые фиксируются 64 в блоке 14 хранения номеров вычис- ляемых функций, В соответствии с определенными по приведенному правилу элементами вектора Wp осуществляется последовательное вычисление ЛФ по определению значений у. ,если W О, При этом адрес вычисляемой ЛФ однозначно определяется номером разряда блока 14, для которого V О, В соответствии с таким адресом вычисляемая функция из блока 13 памяти передается в блок 15 вычисления логических функций. После того, как вычисляются ЛФ, для которых,Wj О, текущий шаг работы устройства завершается окончанием формирования нового слова выходной информации Y,, , и устройство переходит на прием очередного нового слова входной информации Х,, Последовательность обработки информации по шагам с момента пуска устройства при УН 7 О и наличии вычисляемых функций (случаи 1) WH 0,2(Wц О, вычисляемые функции отсутствуют - , не представляют интереса, так как .уст- ройство вновь обращается за входной информацией и подтверждает выходные сигналы до тех пор, пока не появяются изменения входной информации) ожно представить таким образом: 0-й шаг: Х° X у -п 1и5М- - 1-й шаг 1) X : х;, , Y;bix : Y,% 2) х;, : ,®о, Y;, : Y°©Y,°; при , Х,: Х,Х;„ , у уо t н 4) при вычисляем СЛФ и формируем Yj, ; 2-й шаг 1) , Y,, : 2)XJ, : Х;®Х,Х,ФХ,, , YlliM : Y;©Y , 3)при S,1, , , Y -гУ АС/ 4)при вычисляем СЛФ и формируем YH; 3-й шаг 1) , , Y , 2) х;;; , Yi : Y YI:,©Y;; 3) при Sj 1 Xt: .XS: Xjl , Y«: Yll; 4) при вычисляем СЛФ и формируем Y™ и т.д. Для 3-го шага ХЦ., X меют следующий смысл: Х,, - входное лово, полученное в начале текущего,

(третьего) шага из внешней среды (, ); ,- отражает изменение полуенного значения по отношению к значению Х, сохранившемуся с предыущего шага; - отражает измене- j ие сформированного в конце предьщуего шага значения по отношению значению Y, сохранившемуся с преыдущего шага, Y - выходное слово, сформированное в конце текущего шага, 10 которое в начале следующего шага вьщается во внешнюю среду как реакция на входное воздействие, поступившее в начале текущего шага.

По сигналу Пуск запускается блок 15 16 синхронизации и начинает вырабатывать управляющие сигналы 1,о пульсом IQ устанавливаются в исходное состояние все блоки устройства - сбрасываются в нулевое состояние 20 триггер 18j, признака 84, триггеры первой.и второй ступени блока 14 хранения номеров вычисляемых функций, регистры входных и выходных сигналов в блоке 1 ввода-вьшода, регистр 2 но-25 вых значений входных сигналов, регистр 3 новых значений выходных сигналов, регистр 4 старых значений входных сигналов, регистр 5 старых значений выходных сигналов, первый 30 6 и второй 7 блоки сумматоров по модулю два, регистры измененных состояний входных 10 и выходных 11 сигналов, устанавливается в единичное состояние триггер ISj признака 35 Sj. В начале каждого нового шага в регистре 3 новых значений выходных сигналов записаны значения выходных Сигналов, соответствующие окончанию предшествующего шага, дО а в регистре 4 старых значений входных сигналов и в регистре 5 старых значений выходных сигналов началу предшествзгющего шага.

Если первый элемент ИЛИ 8 не зафиксирует изменений входных и (или) выходньк сигналов, т.е. Sj 0, и если на выходе второго элемента ИЛИ 9 , то блок 16 синхрониза.ции вьщает управляющие сигналы 1, 50 Ij, и Ij. По сигналу 1 производится прием очередного нового слова входной информации в блок 1 вводавывода. Сигналом Ig осуществляется передача входной информации из (Зло- 55 ка 1 ввода-вьтода в регистр 2 новых значений входных сигналов и выходной информации из регистра 3 новых

значений выходных сигналов в блок

1ввода-вывода. По сигналу I,, производится поразрядное сложение по модулю два содержимого регистров

2и 4 в первом 6 сумматоре, по модулю два и содержимого регистров 3 и 5 во втором 7 сумматоре по модулю два,

а также выдача из блока 1 ввода-вывода выходных сигналов, которые подтверждают предыдущие сигналы.

Если в результате вновь произве,денного.сравнения вьшвляется измене.ние входных сигналов, на выходе первого элемента ИЛИ 8 Появляется сигнал . В этом случае блок 16 синхронизации вырабатывает сигнал 1ц, по которому производится передача признака из регистров 10 и 11 для обращения к первому блоку 12 памяти, а из него на вход блока 14 хранения номеров вычисляемых функций вьщаются номера функций, в которые входят переменные, изменившие Свои значения По сигналу 1 осуществляются передач содержимого регистров 2 и 3 в регистры 4 и 5 соответственно и установка ..

С первого вьпсода блока 14 информация о наличии вычисляемых функций поступает на входы второго элемента ИЛИ 9. При наличии вычисляемых функций на выходе второго элемента ИЛИ 9 появляется сигнал . Тогда очередной сигнал блока 16 синхронизации (сигнал Ij) подается на управляющий вход блока 14. По этому сигналу с третьего выхода блока 14 вьщается сигнал выборки функции из второго блока 13 памяти, а через второй выход блока 14 вьщается разрешение на прием результата вычисления функции в тот разряд регистра 3, номер которого соответствует номеру вычис.ляемой функции. По сигналу Ij сбрасывается в О счетчик 21 инструкций в блоке 15 и передается содержимое регистров 2 и 5 устройства соответственно в регистры 31 и 32 в блоке 15 (фиг.З). Далее по сигналу 1. устанавливается в О триггер 18 признака 8j. Сигнал Ij производит прибавление единицыв младший разряд счетчика 21 инструкций в блоке 15. По-сигналу i производится опрос узла 20 сравнения в блоке 15, передача инструкции, номер которой соответствует числу в счетчике 21 и которая выбирается дешифратором 22 7 номеров инструкций в блоке 15, на входы регистра 27 операций, дешифра торов первого 34 и ьторого 35 адресов в блоке 15 вычисления логичес ких функций (фиг,2 и 3). Дешифратор 22 нймеров инструкций выбирает также разряд в регистре 33 промежуточных переменных, номер которого соот ветствует номеру выбранной инструкции, для приема промежуточного результата. При отсутствии сигнала с выхода узла 20 сравнения.вырабатывается далее блоком 16 синхронизации сигнал Ig, по которому заносится результат выполненной инструкции в подготовленный для приема разряд регистра 33 промежуточных переменных. В случае появления сигнала с выхода узла 20 сравнения устанавливаются в единичное состояние тригге ры 18 и 182 признаков S, и S и из блока 16 синхронизации выдается сиг нал 1(,,по которому заносится резуль тат выполненной инструкции в подготовленный для приема разряд регистра 3 новых значений выходных сигналов устройства, а через соответству щие элементы задержки производится сброс триггера IS,; признака S и триггеров 47 второй ступени в блоке 14. Таким образом, до вьщачи сигнала с узла 20 сравнения производится поочередное выполнение всех инструк ций вычисляемой ЛФ. При выполнении последней инструкции выдается сигна Сравнение с выхода узла 20 сравнения и результат попадает в регист 3 новых значений выходных сигналов. Затем процесс вычисления СЛФ повторяется для очередной функции до тех пор, пока не будут вычислены все выбранные функции. Тогда признак и ранее установленный признак переводят блок 16 синхронизации на выработку сигналов для приема очередного входного и выдачу полученного выходного слов. Останов устройства происходит при отключении питания. Формула изобретени Устройство для вычисления систем логических функций, содержащее блок ввода-вывода, регистр новых значени входных сигналов, регистр новых зна чений выходных сигналов, регистр ст 146. 8 рык значений выходных сигналов, регистр старых значений входных сигналов, два блока сумматоров по модулю два, два элемента ИЛИ, регистр измененных состояний входных сигналов, регистр измененных состояний выход-. ных Сигналов, два блока памяти, блок хранения номеров вычисляемых функций, блок вычисления логических функций и блок синхронизации, причем информационные входы и выходы устройства соединены с первыми группами соответственно входов и выходов блока вводда-вывода, вторая группа выходов которого подключена к информационным входам регистра новых значений входных сигналов, выходы которого соединены с первыми группами информационных входов блока вычисления логических функций и первого блока сумматоров по модулю два, а также с информационными входами регистра старых значений входных сигналов, выходы которого подключены к второй группе информационных входов первого блока сумматоров по модулю два, выходы которого подключены к первой группе входов первого элемента ИЛИ и информационным входам регистра измененных состояний входных сигналов, выходы которого соединены с первой группой адресных входов первого блока памяти, выходы которого соединены с информационными входами блока хранения номеров вычисляемых функций,, первая группа выходов которого подключена к входам второго элемента ИЛИ, а вторая группа выходов соединена с входами синхронизации приема регистра новых значений выходных сигналов, выходы которого соединены с второй группой входов блока вводавывода, первой группой информационных входов второго блока сумматоров по модулю два и информационными входами регистра старых значений выход- . ных сигналов, выходы которого соединены с второй группой информационных входов второго блока сумматоров по модулю два,, выходы которого соединены с второй группой выходов первого элемента ИЛИ и информационными входами регистра измененных состояний выходных сигналов, выходы которого соединены с второй группой адресных входов первого блока памяти, третья группа выходов блока хранения номеров вычисляемых функций соединена

с адресными входами второго блока памяти, выходы которого соединены с второй группой информационных вхо- дов блока вьиисления логических функций, информационный выход которого соединен с инфopмaциoнньnv и входами регистра новых значений выходных сигналов, выходы первого элемента ИЛИ, второго элемента ИЛИ и первый, второй и третий управляющие выходы блока вычисления логических функций соединены соответственно с первого по пятый входами блока синхронизации, шестой вход которого соединен с вхо-дом запуска устройства, первый: выход блока синхронизации соединен с входами сброса блока ввода-вывода, регистра новых значений выходных сигналов, регистра новых значений входных сигналов, регистра старых значеНИИ входных сигналов, регистра старых значений выходных сигналов, регистра измененных состояний входных сигналов, регистра измененных состояний выходных сигналов, первого и второго блоков сумматоров по модулю два., блока хранения номеров вычисляемых функций и блока вычисления логических функций, второй выход блока синхронизации соединен с входом синхронизации приема блока ввода-вьшода, .третий выход блока синхронизации соединен с входом синхронизации приема

регистра новых значений входных сигналов и входами синхронизации выдачи блока ввода-вывода и регистра новых значений вьосодных сигналов, четвертый выход блока синхронизации соединен с входами синхронизации первого и второго блоков сумматоров по модулю два, пятьй выход блока синхронизации соединен с входами синхронизации регистра старых значений входных сигналов, регистра старых значений выходных сигналов., регистра измененных состояний входных сигналов и регистра измененных состояний выходных сигналов , шестой выход блока синхронизации соединен с первыми входами синхронизации блока хранения номеров вычисляемых функций и блока вычисления логических функций,с второго по шестой входы синхронизации которого соединены соответственно с седьмого по одиннадцатьш выходами блока синхронизации, одиннадцатьй выход которого соединен также с вторым входом синхронизации блока хранения номеров вычисляемых функций, отличаю0; е е с я тем, что, с целью повышения быстродействия, выходы регистра старых значений выходных сигналов соединены с третьей группой информационных входов блока вычисления логических функций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логических функций | 1983 |

|

SU1233160A1 |

| Устройство для реализации логических функций | 1983 |

|

SU1257658A2 |

| Устройство для реализации логических функций | 1981 |

|

SU1164724A1 |

| Функциональный аналого-цифровой преобразователь | 1990 |

|

SU1809532A1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1543232A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для определения весовых функций | 1987 |

|

SU1501087A1 |

| Устройство для решения системы алгебраических уравнений | 1981 |

|

SU966702A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления технологическим оборудованием, алгоритм функционирования которого описы вается логическими функциями, а также для моделирования цифровых устройств с целью их проверки и диагносМ..Л./1 тики. Цель изобретения - повьшение быстродействия. Устройство содержит блок 1 ввода-вывода, регистр 2 новьк значений входных сигналов, регистр 3 новых значений выходньгх сигналов, регистр 4 старых значений входных сигналов, регистр 5 старых значений выходных сигналов, два бло ка.6,7 сумматоров по модулю два, два элемента ИЛИ 8,9, регистр 10 измененньк состояний входных сигналов, ;регистр 11 измененных состояний выходных сигналов, два блока 12,13 памяти,, блок 14 хранения номеров вычисляемых функций, блок 15 вычисi ления логических функций, блок 16 синхронизации. Цель изобретения (Л достигается за счет соединения, выходов регистра старых значений выходных сигналов с .третьей группой информационных входов блока вычисления логических функций. 7 ил. IC О) , Хча х 4 У: t,.S..S.

.3,%

ro|/i2|3|4l5|gHf{-.-NlfI..q

Т

кР ОКДША1 НДША2 |Р

т

т

AL

fpueA ff ffifte

ToJ/Jl

/

ff

IsMiS iQ

Фиг. 6

Б

Устанодка исходного состния схем устройстба

1

1

и/|Яг Дг- й )8х РгУбь«-- Р1Ун 1

зг

l jl cgX/ jVcgy iy y - zy

Пуск ) 1

|I4 05рашение к 6Ш;Рг f-c-h n h УС

1 О

I г просУзСр i Передача HjS бВЛФ Разрешен прием 1

Г

Обращение к. 6П2 Разрешен прием f YnOJ} .o Р1Х- РгХн;РгУ- РгУс

. .

I

Уб 1г ZH

1/7 П

zr

а РгПЛШ-- Вью(бВЛФ |/й;1 РгУнСи-Вь/х6ВЛФ

0-нет изменения входа u(u/ u et txoda сигна/га

1-есть изменения. 0-нет вычи.сленая ЛФ;

I-есть 0(„числетя ЛФ. i-получено значение бшода Немала.

5 не вычислена;

Мь ЛФ вычислена.

Q-получена пронежуточнаапеременнаяИ

Фиг. 7

| Устройство для реализации логических функций | 1977 |

|

SU732878A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1164724A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1982-11-26—Подача