.Изобретение относится к цифровой вычислительной технике и может быть использовано в системах прерывания вычислительных систем, в том числе в управляюр1их вычислительных машинах и комплексах.

Цель изобретения - улучшение помехозащищенности устройства,

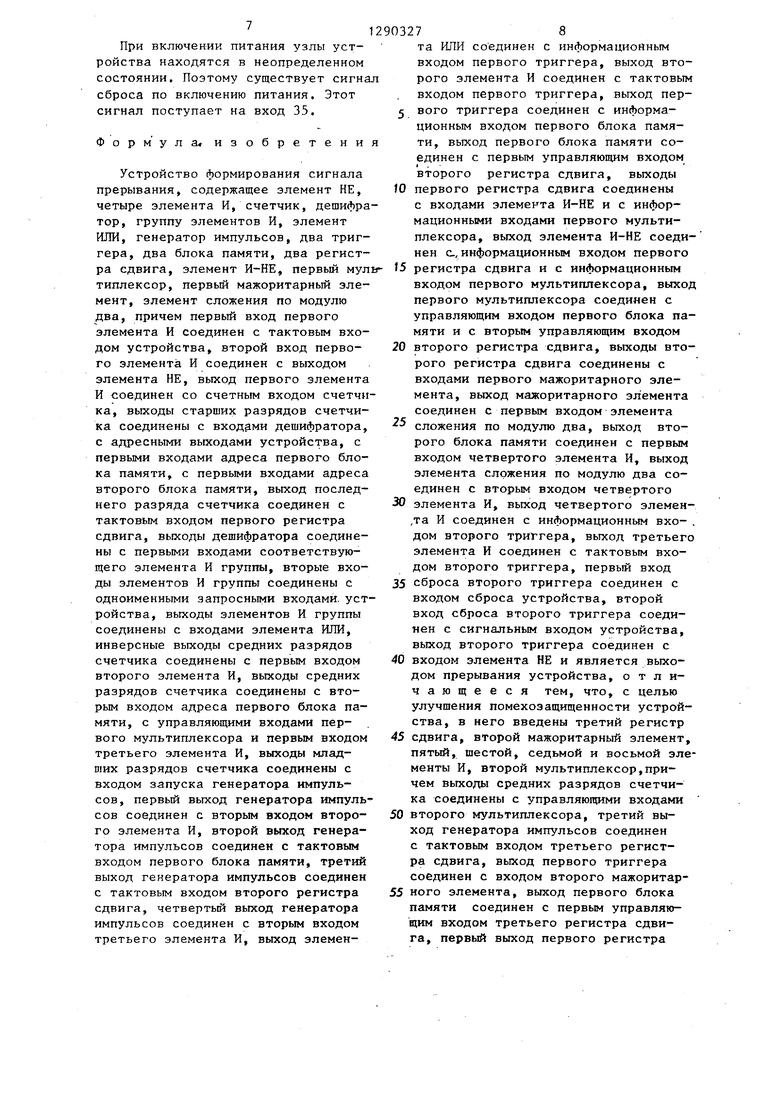

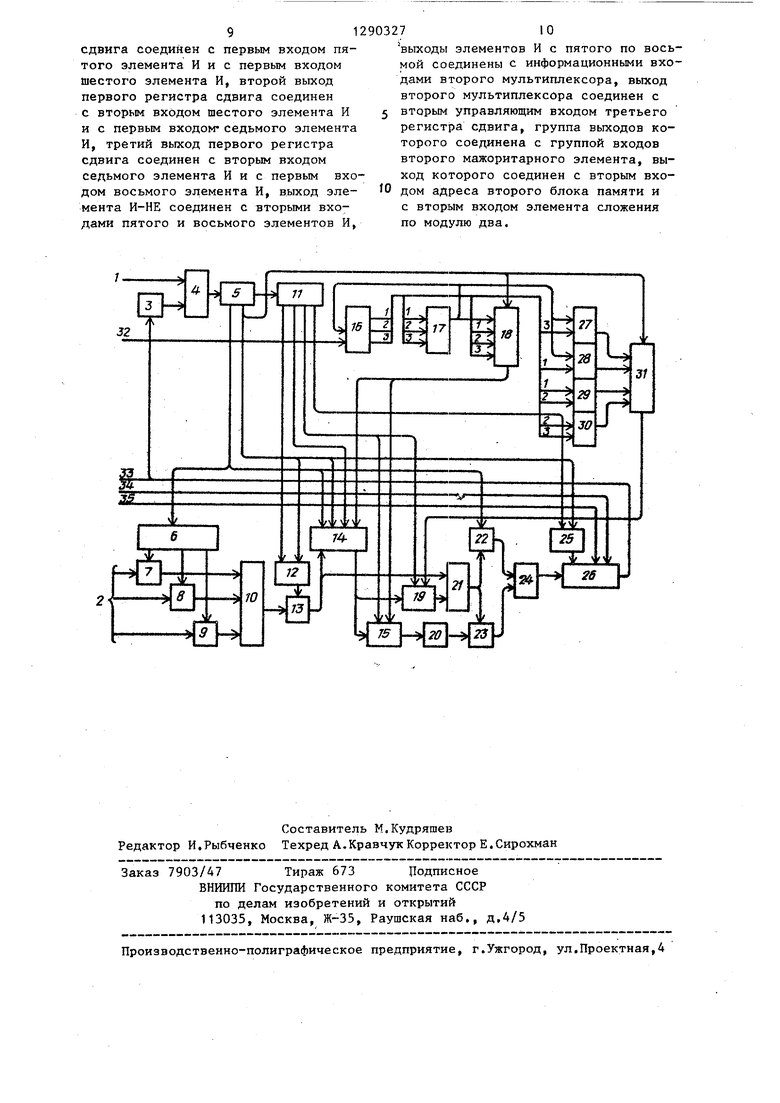

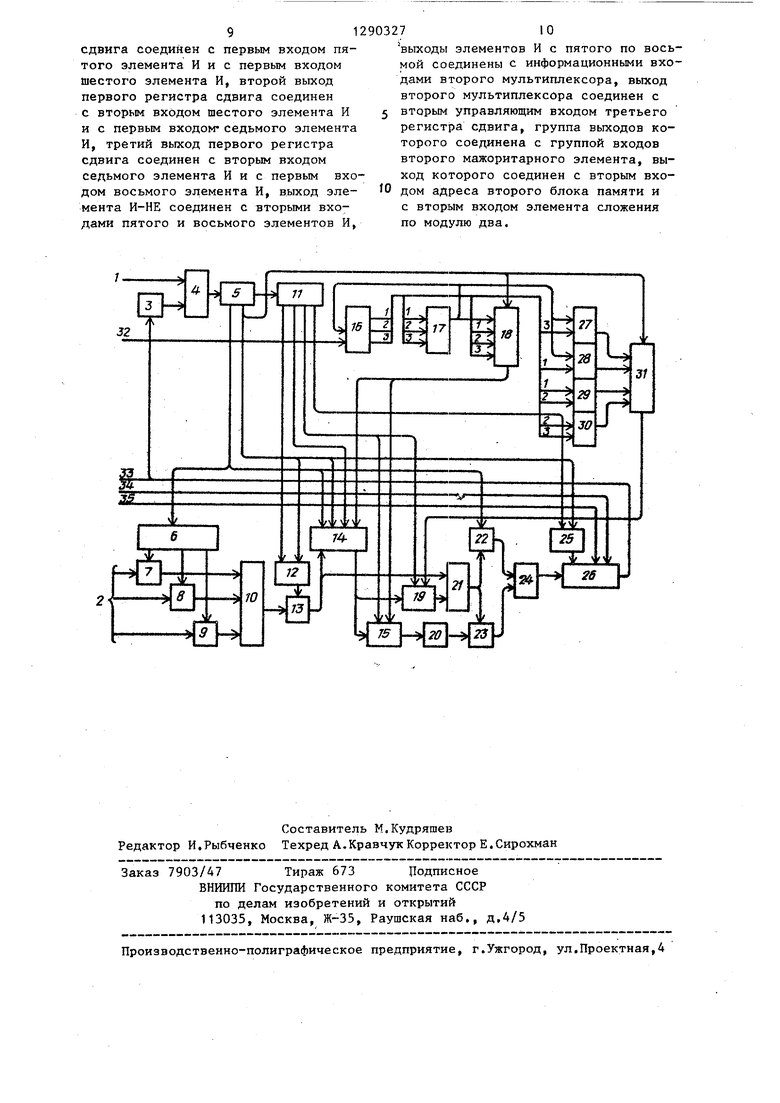

На чертеже представлена структурная схема устройства.

Устройство содержит тактовый вход 1, запросные входы 2, элемент НЕ 3, элемент И 4, счетчик 5, дешифратор 6, элементы И 7 - 9 группы, элемент ИЛИ 10, генератор 11 импульсов, элемент И 12,триггер 13, блок 14 памяти, регистры 15 и 16 сдвига, элемент И-НЕ 17, мультиплексор 18, регистр 19 сдвига, мажоритарные элементы 20 и 21, блок 22 памяти, элемент 23 сложения по модулю два, элементы И 24 и 25, триггер 26, элементы.И 27- 30, мультиплексор 31, адресные выходы 32 устройства, выход 33 прерывания, сигнальный вход 34, вход 35 сброса.

Устройство работает следующим образом.

Двоичн151й счетчик 5, на который с некоторой частотой поступают импульсы по входу 1, при помощи дешифратора 6 и группы элементов И 7-9 в каждом такте проверки наличия за- проср на входах 2 проверяет уровень прерывания, номер которого совпадает с содержимым старших разрядов двоичного счетчика 5, поступающих в первый дешифратор 6 со старших разрядов двоичного счетчика 5. Эта проверка уровня прерывания заключается в сравнении значений запроса за три предыдущих периода проверки, хранящихся в блоке 14 памяти, с текущим значением запроса и определении факта изменения значения запроса. Если в данном уровне прерывания нет изменения значения запроса, то через некоторое время происходит изменение . на единицу старших разрядов двоичного счетчика 5 и проверяется следующи по порядку уровень прерывания. Если имеется изменение значения запроса, просмотр прекращается, устанавливается в 1 триггер 26 и на выход 33 подается сигнал прерывания, а содержимое двоичного счетчика 5 используется для формирования начального адреса прерывающей программы на вы

5

0

5

ходах 32, Сигнал с выхода триггера 26 поступает также на элемент НЕ 3 и запрещает прохождение импульсов с выхода 1 через элемент И 4 на счетный вход двоичного счетчика 5, фиксируя его состояние. После передачи управления прерывающей программы с входа 34 поступает сигнал, сбрасывающий второй триггер 26 и процедура поиска запросов возобновляется.

Через некоторое время происходит изменение на единицу старших разрядов двоичного счетчика 5 и проверяется следующий по порядку уровень прерывания.

Проверка уровней прерывания для формирования сигнала прерывания заключается в сравнении значения сигнала запроса за три предыдущих периода проверки, хранящихся в блоке 14 памяти, с текущим значением запроса и определении факта изменения значения запроса. Поясним работу первого блока 14 памяти. Первьй блок 14 памяти - это оперативное запоминающее устройство ( ОЗУ) с организацией 1 разряд к М слов.

В первом блоке 14 памяти каждому уровню прерывания отведена зона из четырех одноразрядных слов, идущих подряд одно за другим. Зона первого блока 14 памяти определяется старшими разрядами двоичного счетчика 5, ее номер совпадает с номером уровня прерывания.

В течение периода поиска по всем уровням проверка значения запроса выполняется в стандартном такте проверки. В этот такт проверки выполняется одна операция записи информации в блок 14 памяти и три операции считывания информации из первого блока 14 памяти. Обращение к че5 тырем словам зоны первого блока 14 памяти выполняется с помощью двух средних разрядов двоичного счетчика 5. Это обращение к словам первого блока 14 памяти выполняется по

0 очереди, т.е. вначале к первому слову зоны, далее к второму, третьему и затем к четвертому. Для какого слова выполняется операция записи информации, определяет управляющая

5 информация, поступающая из мультиплексора 18 на управляющий вход блока 14 памяти.

Для данного периода поиска по всем уровням прерывания номер слова

0

5

0

в зоне блока 14 памяти, в которое выполняется запись информации, один и тот же.

В конце периода поиска этот номер изменяется циклически, т.е. если в данный период поиска запись выполняется в слово зон блока 14 памяти номер четыре, то в следующий период запись информации выполняется в слово зон номер один, а по прошествии еще двух периодов поиска - .снова в слово номер четыре и т.д.

Номер слова зон первого блока 14 памяти, в которое выполняется запись информации, формируется совмест- -5ода проверки в регистр 19 сдвига, заной работой регистра 16 сдвига,эле-писи сигнала прерывания с выхода элемента И-НЕ 17, мультиплексора 18.мента И 24 в триггер 26. Строб запи- На тактовый вход первого регистраси информации в триггер 13 формирует- 16 сдвига поступает самый старший ся элементом И 12 по совпадению двух разряд двоичного счетчика 5, по зад- 20инверсных значений средних разрядов

нему фронту которого выполняется операция записи информации в первый регистр 16 сдвига. Все выходы первого регистра 16 сдвига соединяются между собой через элемент И-НЕ 17, выход которого подключен к входу данных регистра 16 сдвига. Поэтому до тех пор, пока на одном из выходо регистра 16 сдвига имеется О, в него записываются сигналы 1. Пос- ле трех периодов поиска по всем уровням прерывания элемент И-НЕ 17 переключается, после чего в течение периода поиска на управляющем входе первого регистра 16 сдвига появляется О. Благодаря этому.О присутствует только на одном выходе регистра сдвига или на выходе эле- :мента И-НЕ 17. Выходу элемента И-НЕ 17 поставлены в соответствие все первые слова зон первого блока 14 памяти. Трем выходам регистра 16 сдвига поставлены в соответствие все вторые, третьи и четвертые слова зон первого блока 14 памяти соответственно. Опрос значений выходо регистра 16 сдвига и выхода элемент И-НЕ 17 выполняет мультиплексор 18, на управляющий вход которого поступают два средних разряда двоичного счетчика 5. На выходе мультиплексора 18 появляется признак, указывающ выполнять первому блоку 14 памяти операцию записи или считывания данного слова.

Адрес обращения к слову в блоке 14 памяти образуется объединением старших и средних разрядов двоичного счетчика 5,

Такт проверки изменения значения запроса в данном уровне прерывания одинаков для всех зон первого блока

14памяти. Он состоит из подачи кода уровня прерывания на дешифратор 6 и второй адресный вход блока 14 памяти, операции записи текущего значения запроса с выхода элемента ИЛИ 10 в триггер 13, четырех операций обращения к блоку 14 памяти, трех операций записи значения запроса за три предыдущих периода проверки в регистр

15сдвига, двух операций записи значения-, запроса за два предьщущих пери

двоичного счетчика 5 и строба, присутствующего на первом выходе генератора 11 импульсов, С выхода элемента И 12 строб поступает на тактовый вход триггера 13. При этом последний фиксирует значение запроса, поступившее на его вход, на весь такт поиска.Это обеспечивает возможность асинхронной работы источников запросов по отношению к устройству. Значение запроса с выхода триггера 13 поступает на информационный вход блока 14 памяти, Эта информация записывается в блок 14 памяти при поступлении с выхода

мультиплексора 18 признака записи. После записи значения запроса в триггер 13 выполняются четыре операции обращения к блоку 14 памяти, каждая из которых сопровождается

признаком записи или считывания, поступающим из мультиплексора 18,Этот же признак поступает,и на управляющий вход регистра 15 сдвига, который во время операции записи в блок 14

памяти пропускает такт записи информации. Операции записи значения запроса с выхода блока 14 памяти в регистр 15 сдвига выполняются во время трех операций считывания информации из блока 14 памяти.

Регистр 19 сдвига пропускает два такта записи информации. Первый пропущенный такт - такт операции записи в блок 14 памяти, как и в регистре 15 сдвига. Второй пропущенный такт- это такт считывания информации из того слова зоны блока 14, которое было записано раньше двух других

слов и которое в следующий такт проверки будет обновлено.

Мультиплексор определяет, в какие два обращения к словам зоны блока 14 выполнять запись информации, а в какие - не выполнять запись информации в регистр 19 сдвига. Это достигается путем совместной работы регистра 16 сдвига, элемента И-НЕ 17, элементов И 27 - 30 и мультиплексора 31. Как отмечено вьппе, О присутствует только на одном выходе регистра 16 сдвига или на выходе элемента И-НЕ 17. Данные с выхода первого регистра 16 сдвига и элемента И-НЕ 17 подаются на входы элементов И 27-30 при этом на выходах двух из четырех элементов И 27 - 30 присутствуют сигналы 1, а на выходах двух других - .О. Опрос значений выходов элементов И 27 - 30 выполняет мультиплексор 31, на управляющие входы которого поступают два средних разряда двоичного счетчика 5 (так же, как на управляющие входы мультиплексора 18). На выходе мультиплексора 31 появляется признак, указывающий, выполнять регистру сдвига запись данных, присутствующих на выходе блока 14, или пропустить такт записи информации.

Синхронизацию работы блока 14 памяти, триггера 13 и регистров 15, 19 сдвига выполняет генератор 11 импульсов . I

В блок 14 памяти значение запроса записывается с выхода триггера 13,что обеспечивает использование значения запроса в следующие пери- . оды проверки.

После четырех операций обращения к блоку 14 памяти в регистре 15 сдвига имеем трехразрядное слово, содержащее значения запроса за три предыдущих периода проверки, а в регистре 19 сдвига - двухразрядное слово, содержащее значения запроса за два предыдущих периода проверки. Информация с выхода регистра 15 сдвига параллельным трехразрядным кодом поступает на мажоритарный элемент 20. Информация с выхода регистра 19 сдвига параллельным двухразрядным кодом поступает на мажоритарный элемент 21, на который поступает также информация с выхода триггера 13. С, выходов первого и второго мажоритарных элементов 20 и 21 сигналы поступают на входы элемента 23 сложения по модулю два, который их сравнивает и формирует на выходе сигнал разрешения (1) в случае несовпадения

сигналов на его входах и сигнал запрета (О) в случае совпадения.

Блок 22 памяти - это постоянное запоминающее устройство (ПЗУ) с организацией 1 разряд X Р слов, который

содержит признаки разрешения формирования прерывания по появлению и/или по снятию запросов.

Адрес обращения к слову блока 22 памяти образуется слиянием старших

разрядов двоичного счетчика и информации на выходе мажоритарного элемента 21.

В блоке 22 памяти в слове, соответствующем данной зоне первого блока 14 памяти и значению запроса, полученного на выходе мажоритарного элемента 21, хранится информация раз-решения (1, если разрешено формирование сигнала прерывания по снятию

или появлению запроса) и запрета (О в противном случае).

Элемент И 24 формирует значение сигнала прерывания (1) при появлении СИГ1-1ЛЛОВ разрешения на выходе блока 22 памяти и элемента 23 сложения по модулю два и значение О в противном случае,

Информация с- выхода элемента И 24 поступает на информацирнный вход триггера 26. Строб записи информации в триггер 26 поступает на его тактовый вход и формируется третьим элементом И 25 по совпадению двух прямых значе- НИИ разрядов двоичного счетчика 5 и строба, присутствующего на четвертом выходе генерач;ора 11 импульсов.

Запись информации в регистры 15 и 19 сдвига выполняется по стробу, присутствующему на третьем выходе генератора 11 импульсов.

Генератор 11 импульсов обеспечивает синхронную работу узлов устройст- ва, вырабатывая на своих выходах импульсы таким образом, что импульс на первом выходе начинается раньше,чем на втором, на втором выходе - раньше, чем на третьем, на третьем выходе - раньше, чем на четвертом. Генератор 11 импульсов построен на основе ре- гистра сдвига, управляемого двумя младшими разрядами двоичного счетчика 5,

При включении питания узлы устройства находятся в неопределенном состоянии. Поэтому существует сигна сброса по включению питания. Этот сигнал поступает на вход 35.

Формула, изобретени

Устройство формирования сигнала прерывания, содержащее элемент НЕ, четыре элемента И, счетчик, дешифратор, группу элементов И, элемент ИЛИ, генератор импульсов, два триггера, два блока памяти, два регистра сдвига, элемент И-НЕ, первый мултиплексор, первый мажоритарный элемент, элемент сложения по модулю два, причем первый вход первого элемента И соединен с тактовым входом устройства, второй вход первого элемента И соединен с выходом элемента НЕ, выход первого элемента И соединен со счетным входом счетчика, выходы старших разрядов счетчика соединены с входами дешифратора, с адресными выходами устройства, с первыми входами адреса первого блока памяти, с первыми входами адреса второго блока памяти, выход последнего разряда счетчика соединен с тактовым входом первого регистра сдвига, выходы дешифратора соединены с первыми входами соответствующего элемента И группы, вторые входы элементов И группы соединены с одноименными запросными входами, устройства, выходы элементов И группы соединены с входами элемента ИЛИ, инверсные выходы средних разрядов счетчика соединены с первым входом второго элемента И, выходы средних разрядов счетчика соединены с вторым входом адреса первого блока памяти, с управляющими входами первого мультиплексора и первым входом третьего элемента И, выходы младших разрядов счетчика соединены с входом запуска генератора импульсов, первый выход генератора импуль сов соединен с вторым входом второго элемента И, второй выход генератора импульсов соединен с тактовым входом первого блока памяти, третий выход генератора импульсов соединен с тактовым входом второго регистра сдвига, четвертый выход генератора импульсов соединен с вторым входом третьего элемента И, выход элемен0

5

та ИЛИ со единен с информационным входом первого триггера, выход второго элемента И соединен с тактовым входом первого триггера, выход пер- вого триггера соединен с информационным входом первого блока памяти, выход первого блока памяти соединен с первым управляющим входом I . второго регистра сдвига, выходы

0 первого регистра сдвига соединены с входами элемента И-НЕ и с информационными входами первого мультиплексора, выход элемента И-НЕ соеди- нен с., информационным входом первого

5 регистра сдвига и с информационным входом первого мультиплексора, выход первого мультиплексора соединен с управляющим входом первого блока памяти и с вторым управляющим входом второго регистра сдвига, выходы второго регистра сдвига соединены с входами первого мажоритарного элемента, выход мажоритарного элемента соединен с первым входом элемента сложения по модулю два, выход второго блока памяти соединен с первым входом четвертого элемента И, выход элемента сложения по модулю два соединен с вторым входом четвертого

0 элемента И, выход четвертого элемен- ,та И соединен с информационным вхо- . дом второго триггера, выход третьего элемента И соединен с тактовым входом второго триггера, первый вход

5 сброса второго триггера соединен с входом сброса устройства, второй вход сброса второго триггера соединен с сигнальным входом устройства, выход второго триггера соединен с

0 входом элемента НЕ и является выходом прерывания устройства, отличающееся тем, что, с целью улучшения помехозащищенности устройства, в него введены третий регистр

5 сдвига, второй мажоритарный элемент, пятый, шестой, седьмой и восьмой элементы И, второй мультиплексор,причем выходы средних разрядов счетчика соединены с управляющими входами

0 второго мультиплексора, третий выход генератора импульсов соединен с тактовым входом третьего регистра сдвига, выход первого триггера соединен с входом второго мажоритар5 ного элемента, выход первого блока памяти соединен с первым управляющим входом третьего регистра сдвига, первый выход первого регистра

сдвига соединен с первым входом пятого элемента И и с первым входом шестого элемента И, второй выход первого регистра сдвига соединен с вторым входом шестого элемента И и с первым входом- седьмого элемента И, третий выход первого регистра сдвига соединен с вторым входом седьмого элемента И и с первым входом восьмого элемента И, выход элемента И-НЕ соединен с вторыми входами пятого и восьмого элементов И,

выходы элементов И с пятого по восьмой соединены с информационными входами второго мультиплексора, выход второго мультиплексора соединен с вторым управляющим входом третьего регистра сдвига, группа выходов которого соединена с группой входов второго мажоритарного элемента, выход которого соединен с вторым входом адреса второго блока памяти и с вторым входом элемента сложения по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в системах прерывания вычислительных систем, в том числе в управляющих вычислительных машинах и комплексах. Целые изобретения является улучшение помехозащищенности устройства. Устройство содержит три регистра сдвига, два мажоритарных элемента, восемь элементов И, два мультиплексора, элемент НЕ, счетчик, дешифратор, группу элементов И, элемент ИЛИ, генератор импульсов, два триггера, два блока памяти, элемент И-НЕ, элемент сложения по модулю два. В устройстве происходит запрет формирования запроса прерывания от помех, отстоящих друг от друга точно на три периода опроса. 1 ил. (Л

Составитель М.Кудряшев Редактор И.Рыбченко Техред А.Кравчук Корректор Е.Сирохман

заказ 7903/47 Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Каган Б.М | |||

| Электронные вычислительные машины и системы | |||

| М.: Энергия, 1979, с.298, рис.8-16 | |||

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-08-22—Подача