1

Изобретение относится к области цифровой вычислительной техники.

Известны вычислительные системы с двухуровневой памятью с произвольной выборкой, содержащие устройства ввода-вывода, каналы, центральный процессор и основное и вспомогательное онеративпые запоминающие устройства (ОЗУ) с произвольной выборкой, где вспомогательное ОЗУ связано цепями двустороннего обмена с осг1овным ОЗУ.

Существенным недостатком известных систем является необходимость буферизации входных и выходных массивов ииформации в основном ОЗУ, что уменьщает объем основного ОЗУ для активных, т. е. хранящихся в основном ОЗУ, частей программ.

Кроме того, простои в работе центрального процессора вследствие конфликтных ситуаций, когда центральный процессор и каналы пытаются обратиться одновременно к одному и тому же блоку основного ОЗУ с произвольной выборкой, значительны, так как все запросы ввода-вывода идут в основное ОЗУ.

Целью изобретения является увеличение объема основного ОЗУ для хранения активных программ и уменьшепие простоев в работе центрального процессора.

Предлагаемая вычислительная система отличается от известных 1ем, что в ией установлены два коммутатора, выход первого из которых соединен со входами каналов, одни входы этого коммутатора соединены с выходами вспомогательного ОЗУ, а другие входы - с выходами основного ОЗУ. Выход второго

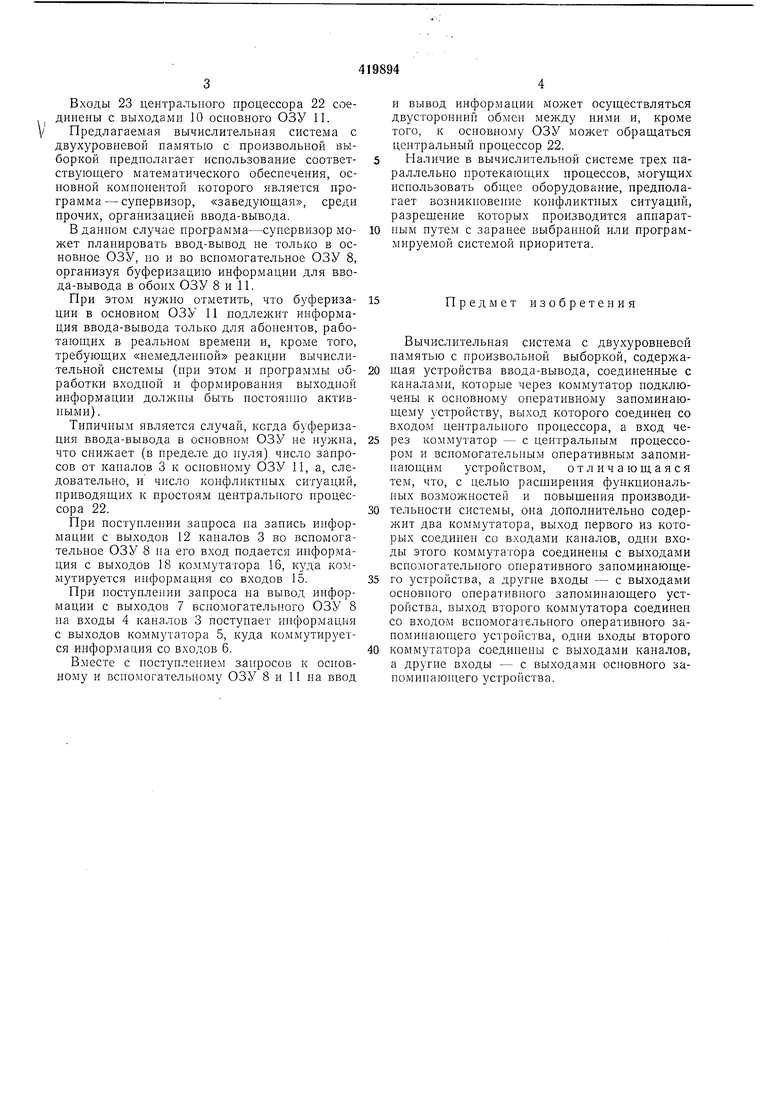

коммутатора соединен со входом вспомогательного ОЗУ. Одни входы второго коммутатора соедннепы с выходами каналов, а другие входы - с выходами основного ОЗУ. На чертеже приведена структурная схе.ма

предлагаемой вычислительной системы с двухуровневой памятью с нроизвольиой выборкой. Вычислительная система содержит устройства ввода-вывода 1, связаиные цепями двустороннего обмена 2 с каналамн 3. Входы 4

каналов 3 соединены с выходами коммутатора 5, одни входы 6 которого соедппепы с выходами 7 вспомогательного ОЗУ 8, а другие входы 9 - с выходами 10 основного ОЗУ II.

Выходы 12 каналов 3 поданы на входы 13

коммутатора 14 и иа входы 15 коммутатора

16, входы 17 которого соединены с выходами

10 основного ОЗУ 11.

Выходы 18 коммутатора 16 поданы на входы вспомогательного ОЗУ 8.

Выходы 19 коммутатора 14 поданы па входы основного ОЗУ 11, в то время как входы 20 и 21 соединены с выходамн 7 вспомогательного ОЗУ 8 и с выходами центрального

процессора 22 соответствеиио.

Входы 23 центрального процессора 22 соединены с выходами 10 основного ОЗУ И.

Предлагаемая вычислительная система с двухуровневой памятью с произвольной выборкой предполагает использование соответствующего математического обеспечения, осповпой компонентой которого является программа- супервизор, «заведующая, средп прочих, организацией ввода-вывода.

В данном случае программа-супервизор может плаппровать ввод-вывод не только в основное ОЗУ, но и во вспомогательное ОЗУ 8, организуя буферизацию информации для ввода-вывода в обоих ОЗУ 8 и И.

При этом нужно отметить, что буферизации в основном ОЗУ 11 подлежит информация ввода-вывода только для абонентов, работающих в реальном времени и, кроме того, требующих «немедленной реакции вычислительной системы (прп этом и программы обработки ВХО/1ПОЙ п формирования выходной информации должны быть постоянно активными) .

Типичным является случай, когда буферизация ввода-вывода в основном ОЗУ не нужна, что (в пределе до нуля) число запросов от каналов 3 к основному ОЗУ 11, а, следовательно, и число конфликтных ситуаций, приводящих к простоям центрального процессора 22.

При поступлении запроса на запись информации с выходов 12 каналов 3 во вспомогательное ОЗУ 8 на его вход подается информация с выходов 18 коммутатора 16, куда коммутируется информация со входов 15.

При поступлении запроса на вывод информации с выходов 7 вспомогательного ОЗУ 8 на входы 4 каналов 3 поступает ипформация с выходов коммутатора 5, куда коммутируется информация со входов 6.

Вместе с поступлением запросов к основному и вспомогательному ОЗУ 8 и 11 на ввод

и вывод информации может осуществляться двусторонний обмен между ними и, кроме того, к основному ОЗУ может обращаться центральный процессор 22.

Наличие в вычислительной системе трех параллельно протекающих процессов, могущих использовать общее оборудование, предполагает возникновение конфликтных ситуаций, разрещение которых производится аппаратным путем с заранее выбранной или программируемой системой приоритета.

Предмет изобретения

Вычислительная система с двухуровневой памятью с произвольной выборкой, содержащая устройства ввода-вывода, соединенные с каналами, которые через коммутатор подключены к основному оперативному запоминающему устройству, выход которого соединен со входом центрального процессора, а вход через коммутатор - с центральным процессором и вспомогательным оперативным запоминающим устройством, отличающаяся тем, что, с целью расщирения функциональных возможностей и повыщепия производительности системы, она дополнительно содержит два коммутатора, выход первого из которых соединен со входами каналов, одпи входы этого коммутатора соединены с выходами вспомогательпого оперативного запоминающего устройства, а другие входы - с выходами основного оперативного запоминающего устройства, выход второго коммутатора соединен со входом вспомогательного оперативного запоминающего устройства, одни входы второго

коммутатора соединены с выходами каналов, а другие входы - с выходами основного заноминаю1цего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1977 |

|

SU692400A1 |

| ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2007 |

|

RU2344472C1 |

| Процессор цифровой вычислительной системы | 1971 |

|

SU475897A1 |

| Устройство оперативной связи с управляющими программами | 1981 |

|

SU970351A1 |

| Система для испытания двигателей внутреннего сгорания | 1987 |

|

SU1575081A1 |

| Вычислительная система | 1977 |

|

SU670936A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

Даты

1974-03-15—Публикация

1971-05-18—Подача