Изобретение относится к автоматическому управлению и может быть использовано при построении распределенных систем управления технологи- ческими комплексами.

Целью изобретения является повышение пропускной способности линий связи за счет уменьшения времени ожидания передачи для каждого локального о устройства управления.

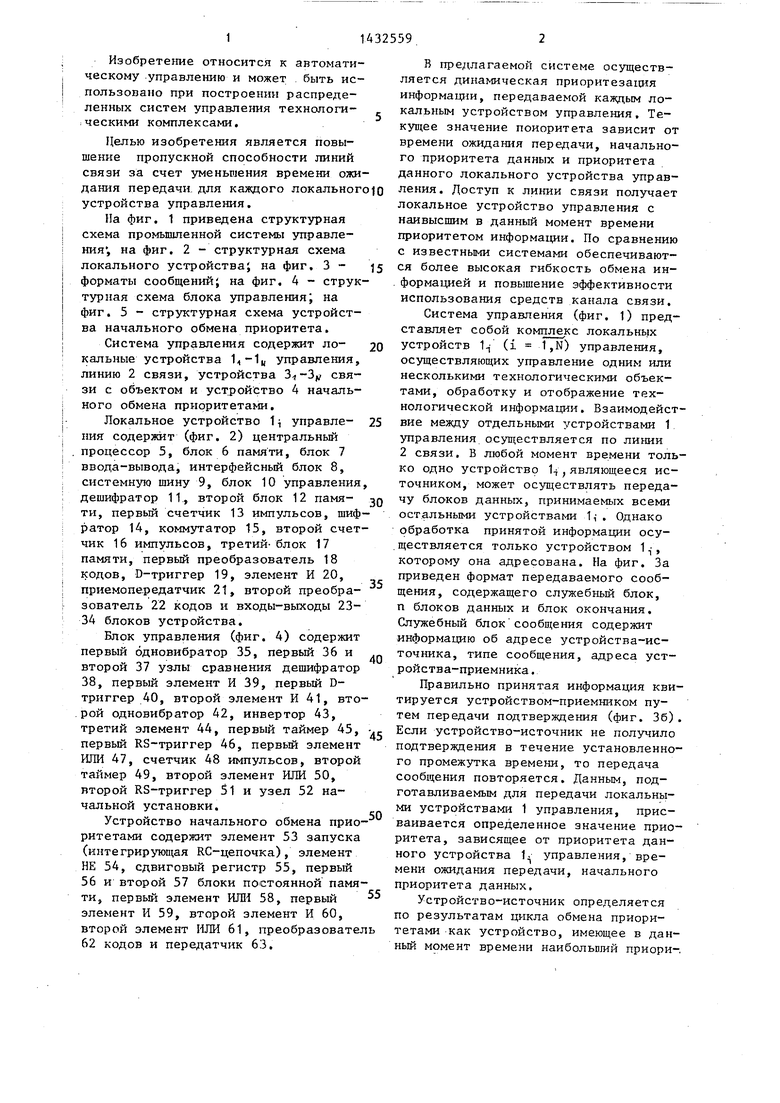

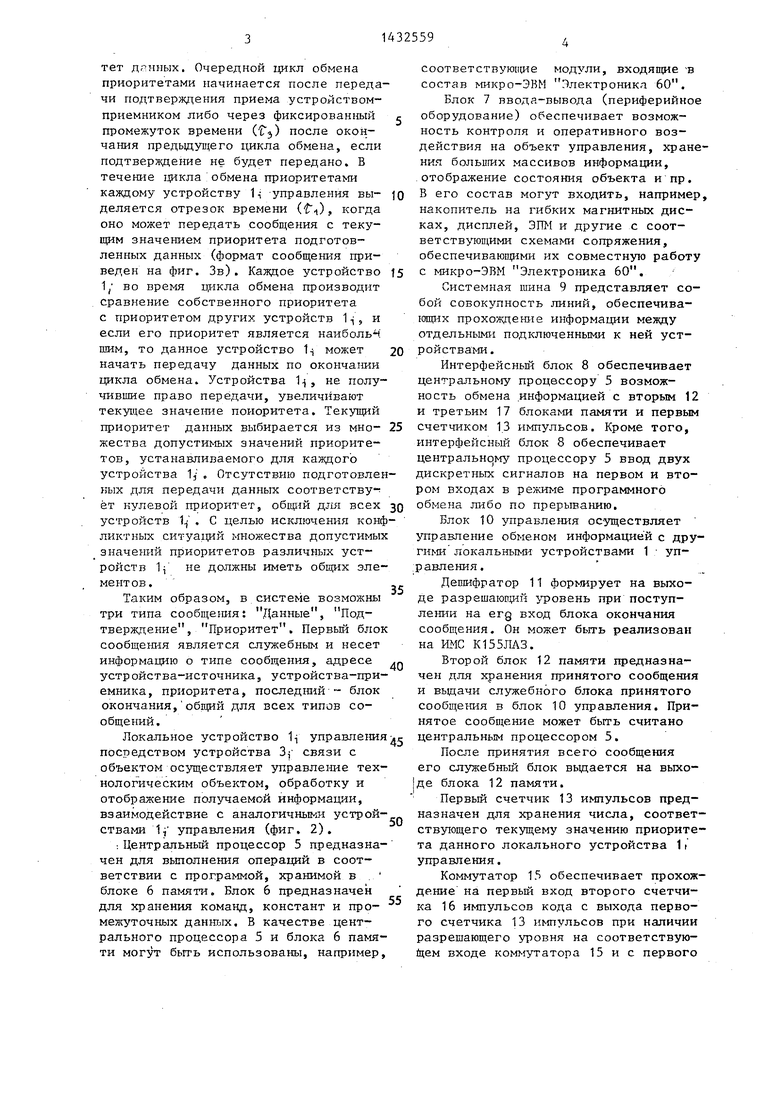

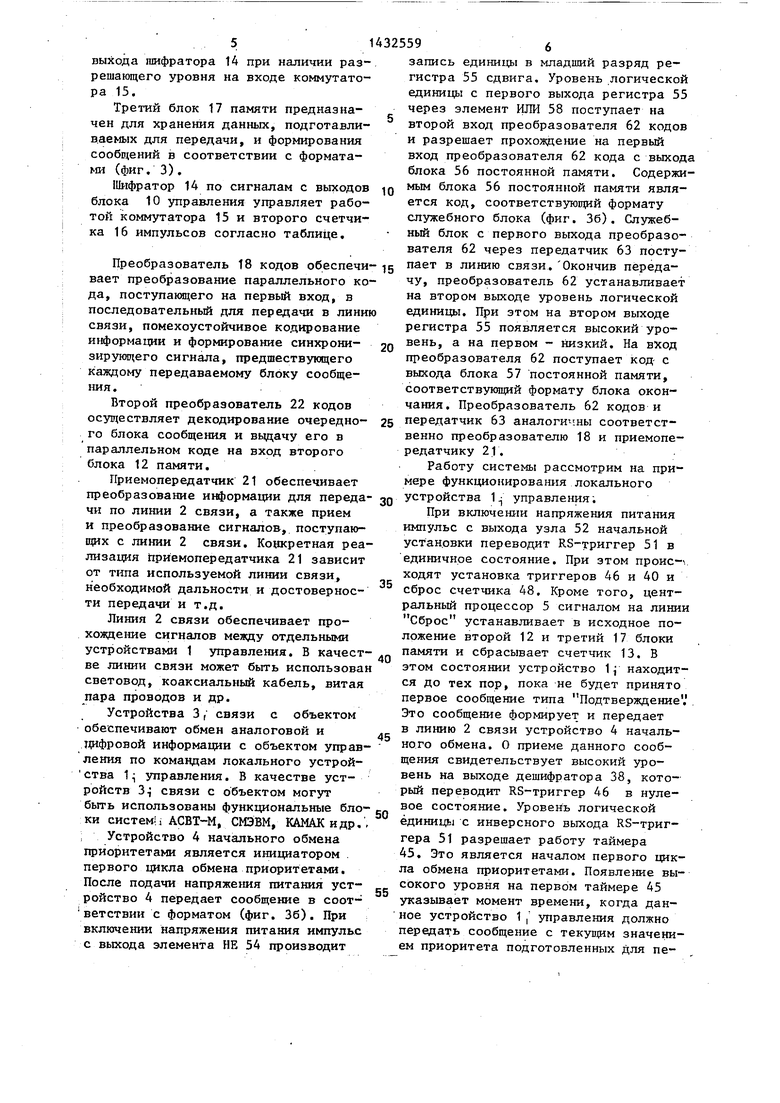

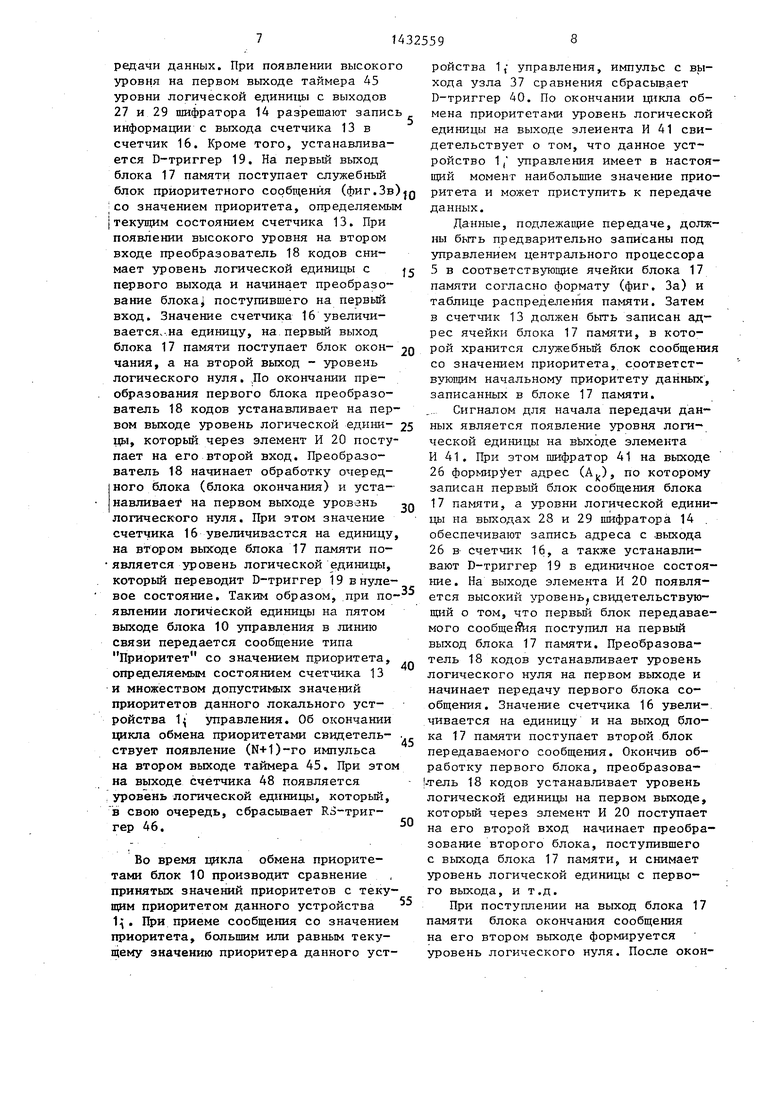

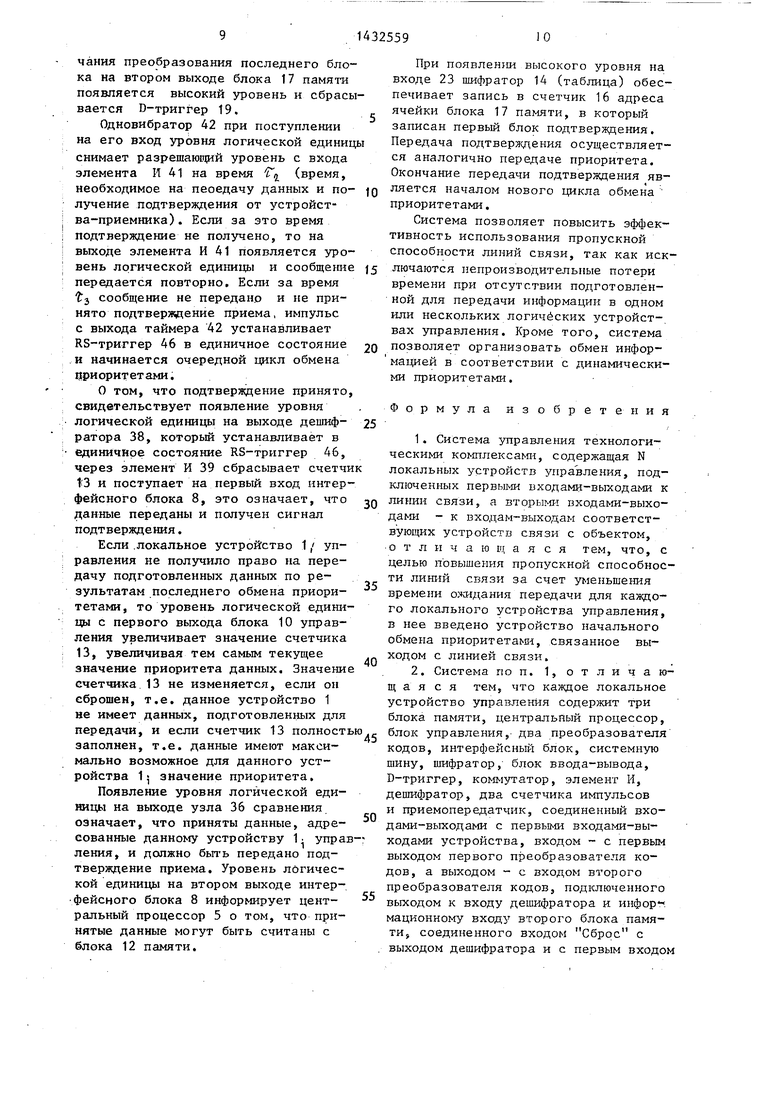

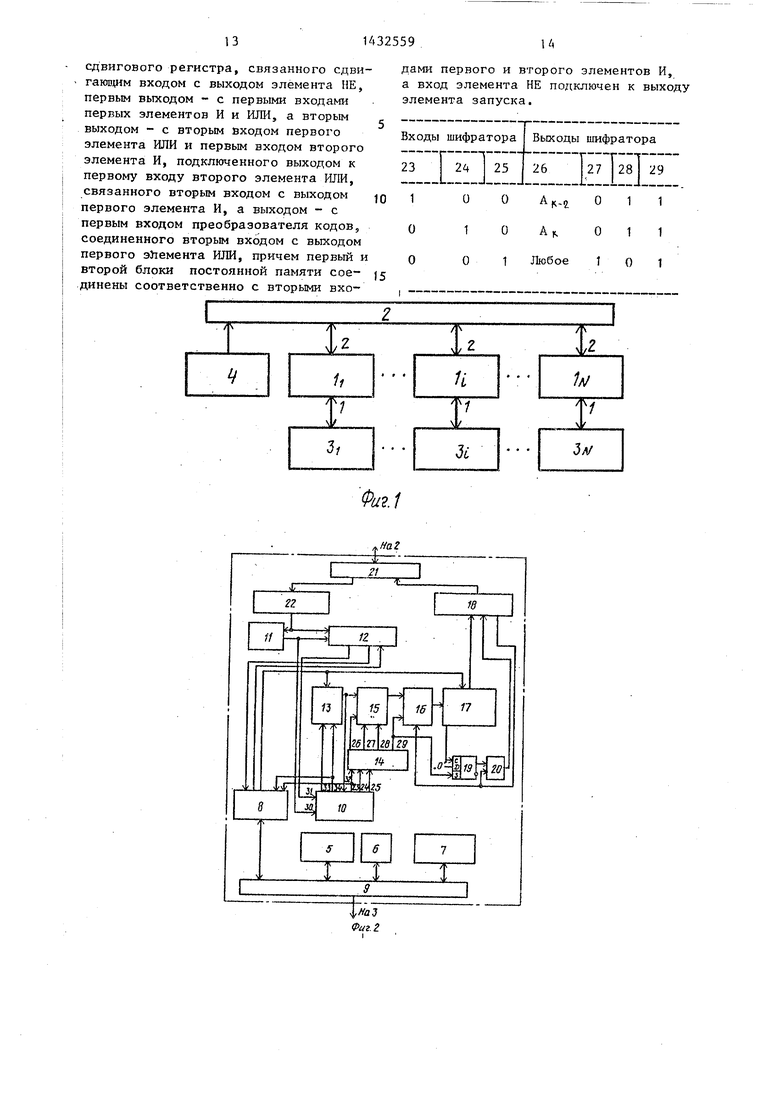

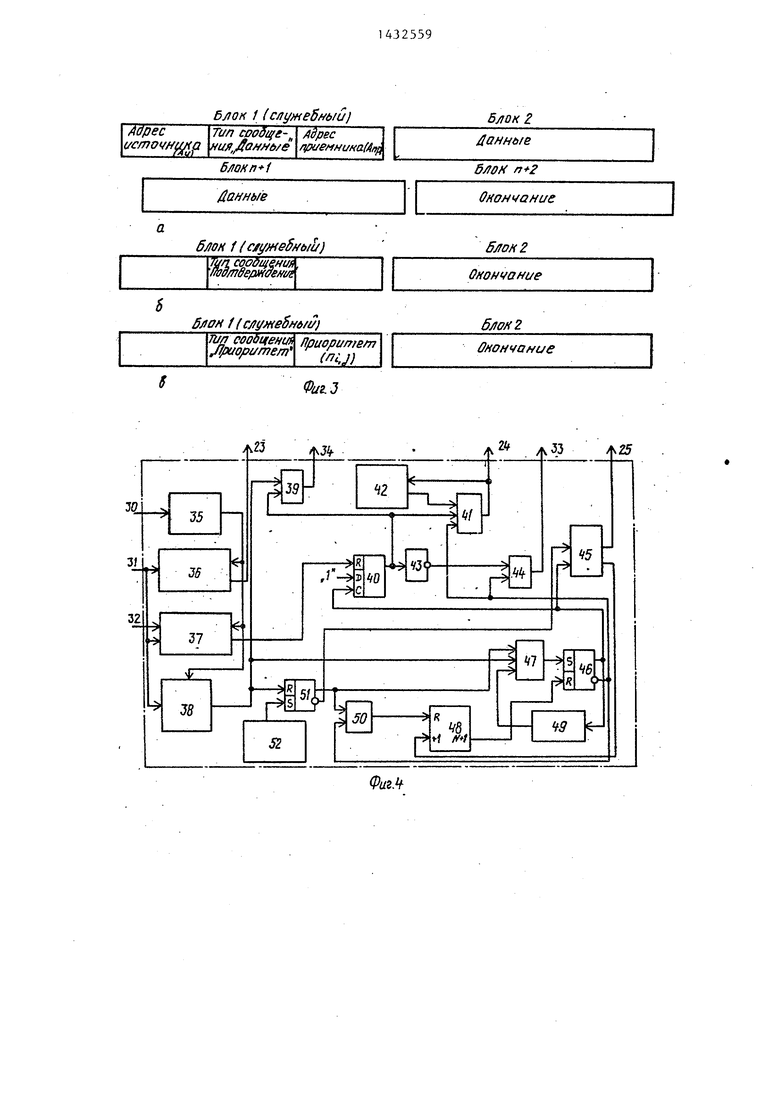

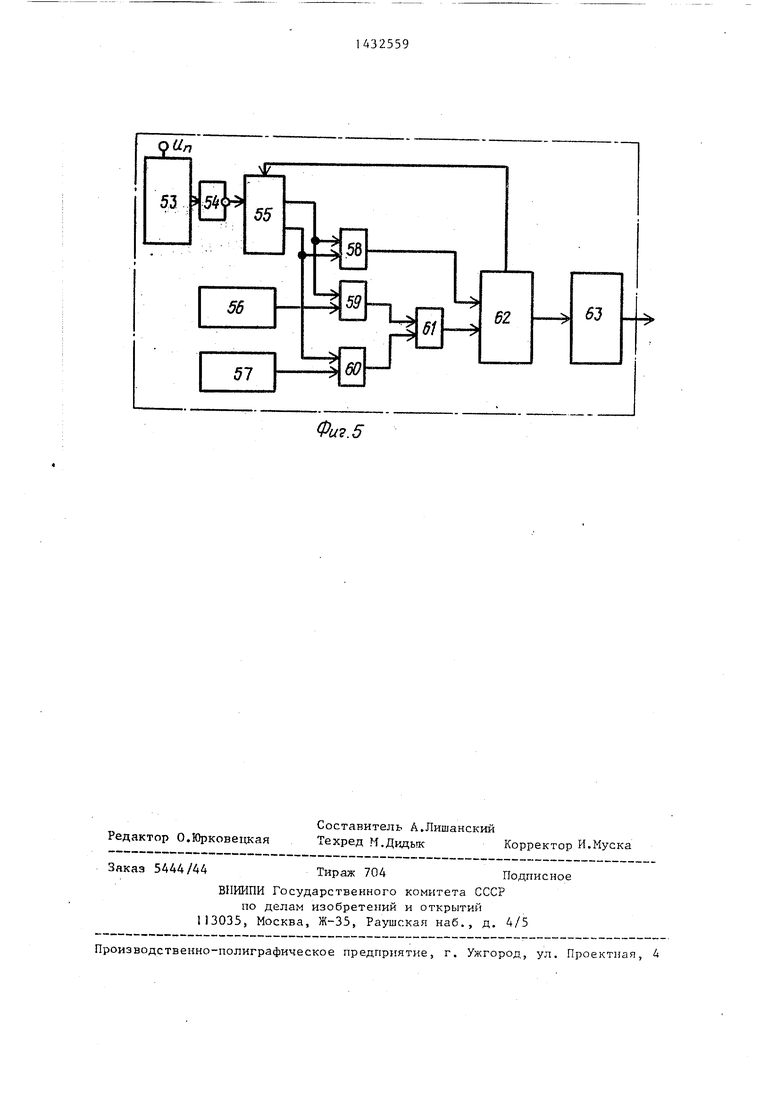

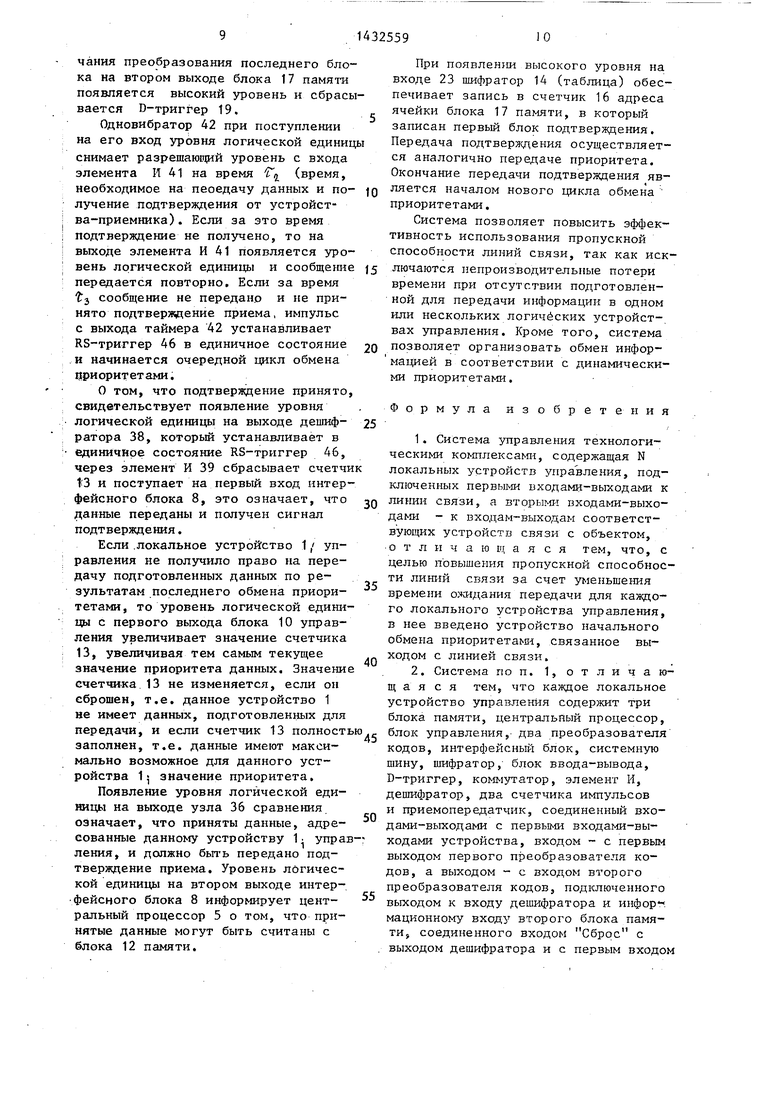

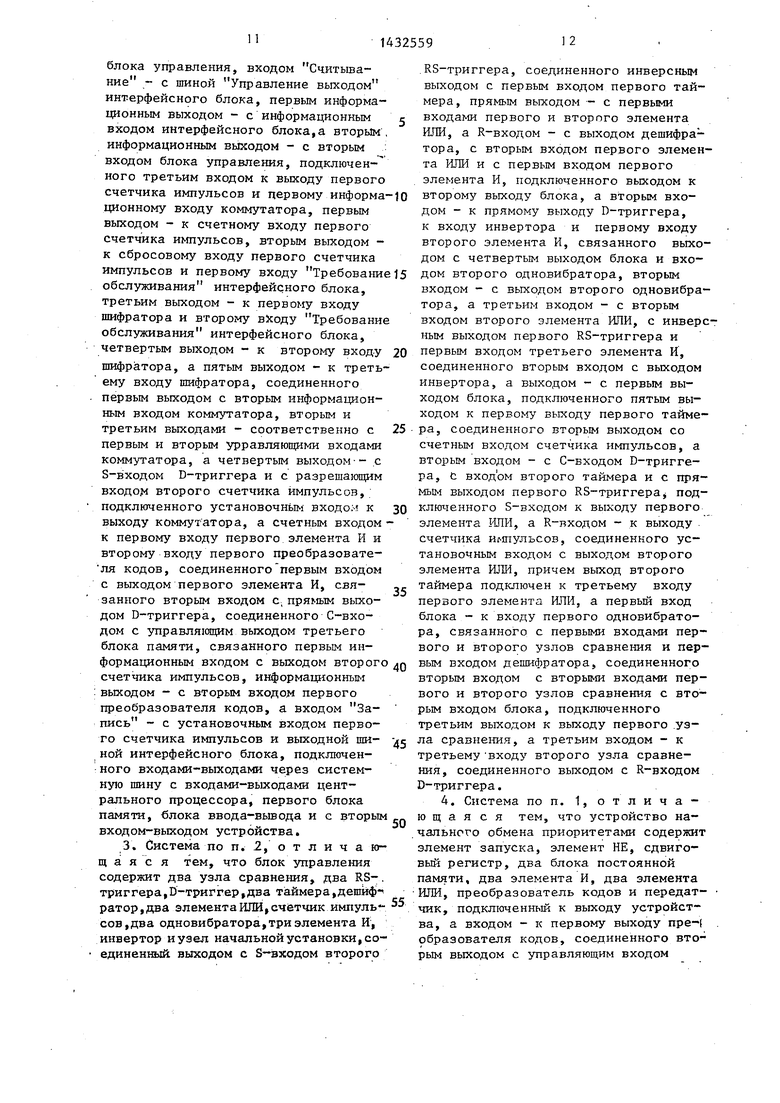

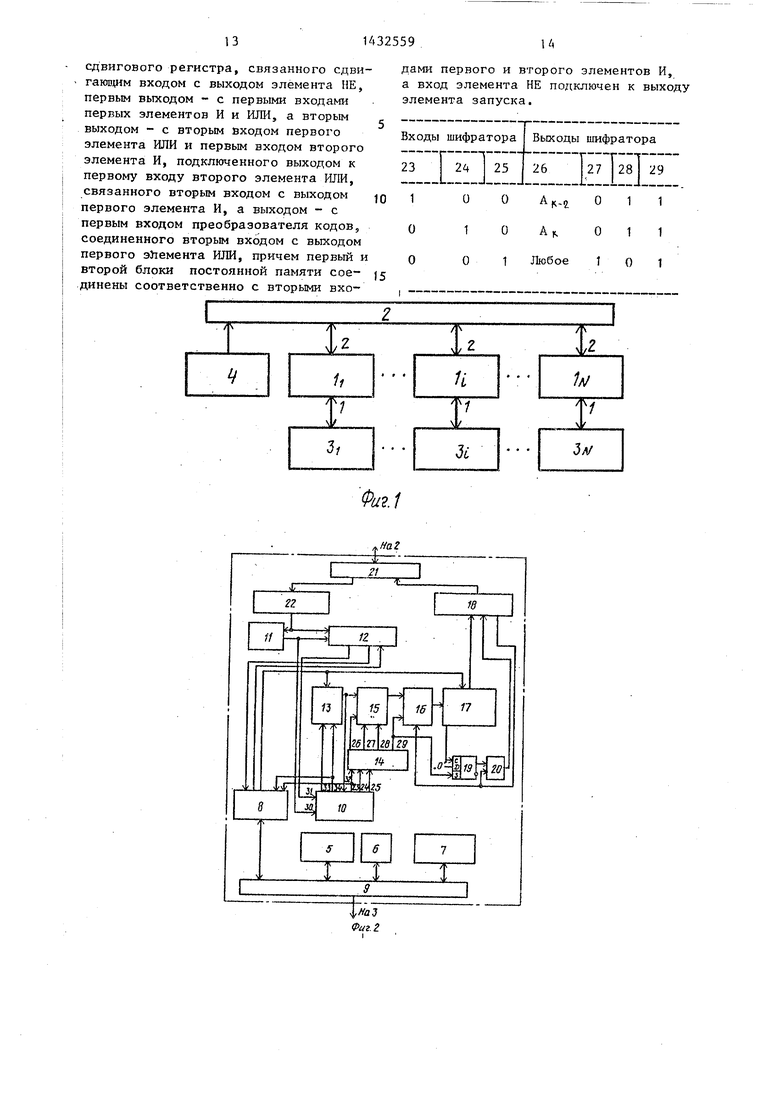

Па фиг. 1 приведена структурная схема промьшшенной системы управления, на фиг. 2 - структурная схема локального устройства; на фиг. 3 - 5 форматы сообщений; на фиг, 4 - структурная схема блока управления; на фиг. 5 - структурная схема устройства начального обмена приоритета.

Система управления содержит ло- 20 кальные устройства управления, линию 2 связи, устройства 3-,-3 связи с объектом и устройство 4 начального обмена приоритетами.

Локальное устройство 1, управле- 25 ния содержит (фиг. 2) центральный процессор 5, блок 6 памяти, блок 7 ввода-вывода, интерфейсный блок 8, системную шину 9, блок 10 управления, дешифратор 11, второй блок 12 памя- -JQ ти, первый счетчик 13 импульсов, шифратор 14, коммутатор 15, второй счетчик 16 импульсов, третий-блок 17 памяти, первый преобразователь 18 кодов, D-триггер 19, элемент И 20, приемопередатчик 21, второй преобразователь 22 кодов и входы-выходы 23- 34 блоков устройства.

Блок управления (фиг. 4) содержит первый одновибратор 35, первый 36 и . второй 37 узлы сравнения дешифратор 38, первый элемент И 39, первый D- триггер 40, второй элемент И 41, вто- рой одновибратор 42, инвертор 43, третий элемент 44, первый таймер 45, -.с первый RS-триггер 46, первый элемент ИЛИ 47, счетчик 48 импульсов, второй таймер 49, второй элемент ИЛИ 50, второй RS-триггер 51 и узел 52 начальной установки.

Устройство начального обмена приоритетами содержит элемент 53 запуска (интегрир тощая RC-цепочка) , элемент НЕ 54, сдвиговый регистр 55, первый 56 и второй 57 блоки постоянной памяти, первый элемент ИЛИ 58, первый элемент И 59, второй элемент И 60, второй элемент ИЛИ 61, преобразователь 62 кодов и передатчик 63.

35

50

о

5

0

5 Q

. .с

5

0

В предлагаемой системе осуществляется динамическая приоритезагшя информации, передаваемой каждым локальным устройством управления, Те- куп;ее значение поиоритета зависит от времени ожидания передачи, начального приоритета данных и приоритета данного локального устройства управления . Доступ к линии связи получает локальное устройство управления с наивысшим в данный момент времени приоритетом информантки. По сравнению с известными системами обеспечиваются более высокая гибкость обмена ин- . форма1дией и повышение эффективности использования средств канала связи.

Система управления (фиг. 1) представляет собой комплекс локальных устройств (i 1,N) управления, осуществляющих управление одним или несколькими технологическими объектами, обработку и отображение технологической информации. Взаимодействие между отдельными устройствами 1 управления, осуп ествляется по линии 2 связи, В любой момент времени только одно устройство 1т , являющееся источником, может осуществлять передачу блоков данных, принимаемых всеми остальными устройствами 1,- . Однако обработка принятой информации осу- .ществляется только устройством , которому она адресована. На фиг. За приведен формат передаваемого сообщения, содержащего служебный блок, п блоков данных и блок окончания. Служебный блок сообщения содержит информацию об адресе устройства-источника, типе сообщения, адреса устройства-приемника .

Правильно принятая информация квитируется устройством-приемником путем передачи подтверждения (фиг. 36). Если устройство-источник не получило подтверяздения в течение установленного промежутка времени, то передача сообщения повторяется. Данным, подготавливаемым для передачи локальными устройствами 1 управления, присваивается определенное значение приоритета, зависящее от приоритета данного устройства Ц управления, времени ожидания передачи, начального приоритета данных.

Устройство-источник определяется по результатам цикла обмена приоритетами как устройство, имеющее в данный момент времени наибольпшй приори-.

тет дан}1ых. Очередной гщкл обмена приоритетами начинается после передачи подтверждения приема устройством- приемником либо через фиксированный промежуток времени ( Гз) после окончания предьщуп его цикла обмена, если подтверждение не будет передано. В течение обмена приоритетами каждому устройству 1, управления вы- деляется отрезок времени (t), когда оно может передать сообщения с текущим значе шем приоритета подготовленных данных (формат сообщения приведен на фиг. Зв). Казвдое устройство во время щгкла обмена производит сравнение собственного приоритета с приоритетом других устройств 1-j , и если его приоритет является наиболь И: тим, то данное устройство 1 может начать передачу данных по окончании цикла обмена. Устройства 1, не получившие право передачи, увеличивают текупдее значе1ше поиоритета. Текущий приоритет данных выбирается из мно- жества допустимых значений приоритетов, устанавливаемого для каждого устройства 1j- . Отсутствию подготовленных для передачи данных соответствую ёт нулевой приоритет, обарш для всех устройств . С целью исключения конфликтных ситуахщй множества допустимых значений приоритетов различных устройств 1i не должны иметь общих элементов .

Таким образом, в.системе возможны три типа сообщегаш; Данные, Подтверждение , приоритет. Первый блок сообщения является служебньм и несет информацию о типе сообщения, гщресе устр ойства-источника, устройства-приемника, приоритета, последш-1й блок окончания, общий для всех типов сообщений.

Локальное устройство 1| управления посредством устройства 3j- связи с объектом осуществляет управление технологическим объектом, обработку и отображение получаемой информации, взаимодействие с аналогичными устрой ствами If управления (фиг. 2).

.Центральный процессор 5 предназначен для выполнения операций в соответствии с программой, хранимой в . блоке 6 памяти. Блок 6 предназначен для хранения команд, констант и промежуточных данных. В качестве центрального процессора 5 и блока 6 памяти могут быть использованы, например.

с Q 5 0 5 оQ

г

5

0

соответствующие модули, вxoдяп иe -в состав микро-ЭВМ Электроника 60.

Блок 7 ввода-вывода (периферийное оборудование) обеспечивает возможность контроля и оперативного воздействия на объект управления, хранения больигих массивов информации, отображение состояния объекта и пр. В его состав могут входить, например, накопитель на гибких магнитных дисках, дисплей, ЭПМ и другие с соот- ветствуюпщми схемами сопряжения, обеспечиваюпщми их совместную работу с микро-ЭВМ Электроника 60.

Системная шина 9 представляет собой совокупность линий, обеспечивающих прохождение информации между отдельными подключенными к ней устройствами.

Интерфейсный блок 8 обеспечивает цeнrpaльнo ry процессору 5 возможность обмена информацией с вторым 12 и третьим 17 блоками памяти и первым счетчиком 13 импульсов. Кроме того, интерфейсньш блок 8 обеспечивает центральнсэму процессору 5 ввод двух дискретных сигналов на первом и втором входах в режиме программного обмена либо по прерыванию.

Блок 10 управления осуществляет управление обменом информацией с другими локальными устройствами 1 ; управления.

Депмфратор 11 формирует на выходе разрешаюпщй уровень при поступлении на erg вход блока окончания сообщения. Он может быть реализован на ИМС К155ЛЛЗ.

Второй блок 12 памяти предназначен для хранения принятого сообщения и вьщачи служебного блока принятого сообщения в блок 10 управления. Принятое сообщение может быть считано центральным процессором 5.

После принятия всего сообщения его служебный блок вьщается на выходе блока 12 памяти.

Первый счетчик 13 импульсов предназначен для хранения числа, соответствующего текущему значению приоритета данного локального устройства 1t управления.

Коммутатор 15 обеспечивает прохождение на первый вход второго счетчика 16 импульсов кода с выхода первого счетчика 13 импульсов при наличии разрешающего уровня на соответствую- (цем входе коммутатора 15 и с первого

выхода шифратора 14 при наличии разрешающего уровня на входе коммутатора 15.

Третий блок 17 памяти предназначен для хранения данных, подготавливаемых для передачи, и формирования сооб0|ений в соответствии с форматами (фиг. 3).

Шифратор 14 по сигналам с выходов блока 10 управления управляет работой коммутатора 15 и второго счетчика 16 импульсов согласно таблице.

запись eдиниIJ ы в младший разряд регистра 55 сдвига. Уровень логической единицы с первого выхода регистра 55 через элемент ИЛИ 58 поступает на второй вход преобразователя 62 кодов и разрешает прохождение на первый вход преобразователя 62 кода с выхода блока 56 постоянной памяти. Содержимым блока 56 постоянной памяти является код, соответствующий формату служебного блока (фиг. 36). Служебный блок с первого выхода преобразователя 62 через передатчик 63 посту

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2005 |

|

RU2286597C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| СПОСОБ ДОСТУПА К ШИНЕ ПЕРЕДАЧИ ДАННЫХ В ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 1989 |

|

RU2010320C1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Устройство для сопряжения | 1980 |

|

SU962906A2 |

Изобретение относится к автоматическому згправленню и может быть использовано при построении распределенных систем управления технологическими комплексами. Цель изобретения - повьшение пропускной способности линий связи за счет уменьшения времени ожидания передачи для каждого локального устройства управления. Система управления технологическими комплексами содержит N локальных устройств управлетгя, линию связи, N устройств связи с объектом и устройство начального обмена приоритетами . Локальное устройство управления посредством устройства связи с объектом осуществляет управление технологическим объектом, отображение получаемой информации, взаимодействие с аналогичными устройствами управления. Обмен информацией между отдельными локальными устройствами управления, осуществляется в соответствии с системой динамических приоритетов . Текущее значеи е приоритета информации зависит от в земени ожидания передачи, начального поиоритета информации и приоритета данного локального устройства управления. Доступ к линии связи получает локальное устройство управления с наивысшим в данный момент времени приоритетом информации. Устройство начального обмена является инициатором начала обмена между локальными устройствами куправления. Изобретение обеспечивает высокую гибкость обмена информацией в системе и повышение эффективности использования средств канала связи. 3 з.п. ф-лы, 5 ил., 1 табл. to (Л 4 СО ю ел ел со

20

Преобразователь 18 кодов обеспечи- 15 пает в линию связи. Окончив переда- вает преобразование параллельного кода, поступающего на первый вход, в последовательньй для передачи в линию связи, помехоустойчивое кодирование информации и формирование синхронизирующего сигнала, предшествующего каждому передаваемому блоку сообщения.

Второй преобразователь 22 кодов осуществляет декодирование очередного блока сообщения и вьщачу его в параллельном коде на вход второго блока 12 памяти.

25

чу, преобразователь 62 устанавливает на втором выходе уровень логической единицы. При этом на втором выходе регистра 55 появляется высокий уровень, а на первом - низкий. На вход преобразователя 62 поступает код с выхода блока 57 постоянной памяти, соответствующий формату блока окончания. Преобразователь 62 кодов и передатчик 63 аналогичны соответственно преобразователю 18 и приемопередатчику 21.

Работу системы рассмотрим на примере функционирования локального

Приемопередатчик 21 обеспечивает

Работу системы рассмотр мере функционирования лока

преобразование информации для переда- о устройства 1 управления;

При включении напряжени импульс с выхода узла 52 н установки переводит RS-три единичное состояние. При э ходят установка триггеров сброс счетчика 48. Кроме т ральный процессор 5 сигнал Сброс устанавливает в ис ложение второй 12 и третий памяти и сбрасывает счетчи этом состоянии устройство ся до тех пор, пока не буд первое сообщение типа Под Это сообщение формирует и в линию 2 связи устройство ного обмена. О приеме данн щения свидетельствует высо вень на выходе дешифратора рый переводит RS-триггер 4 вое состояние. Уровень лог единицы с инверсного выход гера 51 разрешает работу т 45. Это является началом п ла обмена приоритетами. По сокого уровня на первом та указывает момент времени, ное устройство 1 / управлен передать сообщение с текуп ем приоритета подготовленн

35

40

чи по линии / связи, а также прием и преобразование сигналов, поступающих с линии 2 связи. Конкретная реализация приемопередатчика 21 зависит от типа используемой линии связи, необходимой дальности и достоверности передачи и т.д.

Линия 2 связи обеспечивает прохождение сигналов между отдельными устройствами 1 управления. В качестве линии связи может быть использован световод, коаксиальный кабель, витая пара проводов и др.

Устройства 3, связи с объектом обеспечивают обмен аналоговой и 1ЩФРОВОЙ информации с объектом управения по командам локального устрой- ства 1 т управления. В качестве устройств 3, связи с объектом могут быть использованы функциональные бло- g ки систем i АСВТ-М, СМЭВМ, КАМАК идр,, Устройство 4 начального обмена приоритетами является инициатором первого цикла обмена приоритетами. После подачи напряжения питания устройство 4 передает сообщение в соот- ветствии с форматом (фиг. 36). При включении напряжения питания импульс с выхода элемента НЕ 54 производит

45

55

пает в линию связи. Окончив переда-

чу, преобразователь 62 устанавливает на втором выходе уровень логической единицы. При этом на втором выходе регистра 55 появляется высокий уровень, а на первом - низкий. На вход преобразователя 62 поступает код с выхода блока 57 постоянной памяти, соответствующий формату блока окончания. Преобразователь 62 кодов и передатчик 63 аналогичны соответственно преобразователю 18 и приемопередатчику 21.

Работу системы рассмотрим на примере функционирования локального

о устройства 1 управления;

5

0

5

5

При включении напряжения питания импульс с выхода узла 52 начальной установки переводит RS-триггер 51 в единичное состояние. При этом проис-i ходят установка триггеров 46 и 40 и сброс счетчика 48. Кроме того, центральный процессор 5 сигналом на линии Сброс устанавливает в исходное положение второй 12 и третий 17 блоки памяти и сбрасывает счетчик 13. В этом состоянии устройство 1j находится до тех пор, пока не будет принято первое сообщение типа Подтверждение . Это сообщение формирует и передает в линию 2 связи устройство 4 начального обмена. О приеме данного сообщения свидетельствует высокий уровень на выходе дешифратора 38, который переводит RS-триггер 46 в нулевое состояние. Уровень логической единицы с инверсного выхода RS-триг- гера 51 разрешает работу таймера 45. Это является началом первого цикла обмена приоритетами. Появление высокого уровня на первом таймере 45 указывает момент времени, когда дан- ное устройство 1 / управления должно передать сообщение с текуп им значением приоритета подготовленных для передачи данных. При появлении высоког уровня на первом выходе таймера 45 уровни логической единицы с выходов 27 и 29 шифратора 14 разрешают запис информации с выхода счетчика 13 в счетчик 16. Кроме того, устанавливается D-триггер 19. На первый выход блока 17 памяти поступает служебный блок приоритетного сообщения (фиг.Зв ;со значением приоритета, определяемы I текущим состоянием счетчика 13. При появлении высокого уровня на втором входе преобразователь 18 кодов снимает уровень логической единицы с первого выхода и начинает преобразование блокад поступившего на первый вход. Значение счетчика 16 увеличивается.-на единицу, на первый выход блока 17 памяти поступает блок окон- чания, а на второй выход - уровень логического нуля. По окончании преобразования первого блока преобразователь 18 кодов устанавливает на первом выходе уровень логической едини- цы, который через элемент И 20 поступает на его второй вход. Преобразователь 18 начинает обработку очередного блока (блока окончания) и устанавливает на первом выходе уровень логического нуля. При этом значение счетчика 16 увеличивается на единицу на втором выходе блока 17 памяти по- является уровень логической единищ), который переводит D-триггер 19 в нулевое состояние. Таким образом, при по явлении логической единицы на пятом выходе блока 10 управления в линию связи передается сообщение типа Приоритет со значением приоритета, определяемым состоянием счетчика 13 и множеством допустимых значений приоритетов данного локального устройства 1{ управления. Об окончании цикла обмена приоритетами свидетель- ствует появление (N+1)-ro импульса на втором выходе таймера 45. При этом на выходе счетчика 48 появляется ,уровень логической единицы, который, в свою очередь, сбрасьшает RS-триг- гер 46.

Во время цикла обмена приоритетами блок 10 производит сравнение принятых значений приоритетов с теку

щим приоритетом данного устройства 1д. При приеме сообще шя со значением приоритета, большим или равным текущему значению приоритера данного устд о 5 эп

0

0

5

ройства 1,- управления, импульс с выхода узла 37 сравнения сбрасывает D-триггер 40. По окончании цикла обмена приоритетами уровень логической единицы на выходе элеиента И 41 свидетельствует о том, что данное устройство 1, управления имеет в настоящий момент наибольшие значение приоритета и может приступить к передаче данных.

Данные, подлежащие передаче, должны быть предварительно записаны под управлением центрального процессора 5 в COOT нет ств тощие ячейки блока 17 памяти согласно формату (фиг. За) и таблице распределения памяти. Затем в счетчик 13 должен быть записан адрес ячейки блока 17 памяти, в которой хранится служебный блок сообщения со значением приоритета, соответствующим начальному приоритету данных, записанных в блоке 17 памяти.

Сигналом для начала передачи данных является появление уровня логической единицы на вЬгходе элемента И 41. При этом шифратор 41 на выходе 26 формирует адрес (А,), по которому записан первый блок сообщения блока 17 памяти, а уровни логической единицы на выходах 28 и 29 шифратори 14 обеспечивают запись адреса с выхода 26 в- счетчик 16, а также устанавливают D-триггер 19 в единичное состоя- ше. На выходе элемента И 20 появляется высокий уровень,свидетельствующий о том, что первьш блок передаваемого сообщейия поступил на первый выход блока 17 памяти. Преобразователь 18 кодов устанавливает зфовень логического нуля на первом выходе и начинает передачу первого блока сообщения. Значение счетчика 16 увеличивается на единицу и на выход блока 17 памяти поступает второй блок передаваемого сообщения. Окончив обработку первого блока, преобразова- -тель 18 кодов устанавливает уровень логической единицы на первом выходе, который через элемент И 20 поступает на его второй вход начинает преобразование второго блока, поступившего с выхода блока 17 памяти, и снимает уровень логической единицы с первого выхода, и т.д.

При поступлении на выход блока 17 памяти блока окончания сообщения на его втором выходе формируется уровень логического нуля. После окончания преобразования последнего блока на втором выходе блока 17 памяти появляется высокий уровень и сбрасывается D-триггер 19.

Одновибратор 42 при поступлении на его вход уровня логической единиц снимает разрешаюпщй уровень с входа элемента И 41 на время Tj (время, необходимое на пеоедачу данных и по- лучение подтверждения от устройства-приемника). Если за это время подтверждение не получено, то на выходе элемента И 41 появляется уровень логической единицы и сообщега е передается повторно. Если за время 3 сообщение не передано и не принято подтверяадение приема, импульс с выхода таймера 42 устанавливает RS-триггер 46 в единичное состояние и начинается очередной цикл обмена приоритетами.

О том, что подтверяздение принято, свидетельствует появление уровня логической единицы на выходе дешиф- ратора 38, который устанавливает в единичное состояние RS-триггер 46, через элемент И 39 сбрасывает счетчи t;3 и поступает на первый вход интерфейсного блока 8, это означает, что данные переданы и получен сигнал подтверждения.

Если .локальное устройство 1/ управления не получило право на передачу подготовленных данных по результатам последнего обмена приоритетами, то уровень логической единицы с первого выхода блока 10 управления увеличивает значение счетчика 13, увеличивая тем самым текущее значение приоритета данных. Значение счетчи-ка. 13 не изменяется, если он сброшен, т.е. данное устройство 1 не имеет данных, подготовленных для передачи, и если счетчик 13 полность заполнен, т.е. данные имеют максимально возможное для данного устройства 1) значение приоритета.

Появление уровня логической единицы на выходе узла 36 сравнения означает, что приняты данные, адре- еованные данному устройству 1. управ ления, и должно бьп-ь передано подтверждение приема. Уровень логической единицы на втором выходе интер- фейсного блока 8 информирует цент- ральный процессор 5 о том, что принятые данные могут быть считаны с блока 12 памяти.

Q j 0

5 Q

.

5

При появленгш высокого уровня на входе 23 шифратор 14 (таблица) обеспечивает запись в счетчик 16 адреса ячейки блока 17 памяти, в который записан первый блок подтверждения. Передача подтверждения осуществляется аналогично передаче приоритета. Окончание передачи подтверждения является началом нового цикла обмена приоритетами.

Система позволяет повысить эффективность использования пропускной способности линий связи, так как исключаются непроизводительные потери времени при отсутствии подготовленной для передачи информации в одном или нескольких логических устройствах управления. Кроме того, система позволяет организовать обмен инфор- манией в соответствии с динамическими приоритетами.

Формула изобретения

о т л и ч а ю щ алея тем, что, с целью повышения пропускной способности линий связи за счет уменьшения времени ожидания передачи для каждого локального устройства управления, в нее введено устройство начального обмена приоритетами, связанное выходом с линией связи.

и приемопередатчик, соединенный входами-выходами с первыми входами-выходами устройства, входом с первым выходом первого преобразователя кодов, а выходом - с входом второго преобразователя кодов, подключенного выходом к входу дешифратора и инфор. мационному входу второго блока памяти, соединенного входом Сброс с выходом дешифратора и с первым входом

блока управления, входом Считьша- ние - с шиной Управление выходом интерфейсного блока, первым информационным выходом - с информационным входом интерфейсного блока,а вторым информационным выходом - с вторым входом блока управления, подключен- ного третьим входом к выходу первого счетчика импульсов и первому информа ционному входу коммутатора, первым выходом - к счетному входу первого счетчика импульсов, вторым выходом - к сбросовому входу первого счетчика импульсов и первому входу Требовани обслуживания интерфейсного блока, третьим выходом - к первому входу шифратора и второму входу Требовани обслуживания интерфейсного блока, четвертым выходом - к второму входу шифратора, а пятым выходом - к третьему входу шифратора, соединенного первым выходом с вторым информационным входом коммутатора, вторым и третьим выходами - соответственно с первым и вторым урравляющи и входами коммутатора, а четвертым выходом-- с S-входом D-триггера и с разрешающим входо 1 второго счетчика импульсов, подключенного установочньгм входом к выходу коммутатора, а счетным входом к первому входу первого элемента И и второму входу первого преобразовате ля кодов, соединенного первым входом с выходом первого элемента И, свя- занного вторьш входом с, пряьатм выходом D-триггера, соединенного С-вхо- дом с управлякщим выходом третьего блока памяти, связанного первым информационным входом с выходом второг счетчика импульсов, информационным

: выходом - с вторым входом первого преобразователя кодов, а входом Запись - с установочным входом первого счетчика импульсов и выходной ши- ной интерфейсного блока, подключен:ного входами-выходами через системную шину с входами-выходами центрального процессора, первого блока памяти, блока ввода-вьшода и е вторы входом-выходом устройства.

:

с, : -Ю е 15 е 20 25ЗО - о Q

-

м

. -

50

55

RS-триггера, соединенного инверсным выходом с первым входом первого таймера , прямым выходом - с первыми входами первого и второго элемента ИЛИ, а R-входом - с выходом дешифратора, с вторым входом первого элемента ИЛИ и с первым входом первого элемента И, подключенного выходом к второму выходу блока, а вторым входом - к прямому выходу D-триггера, к входу инвертора и первому входу второго элемента И, связанного выходом с четвертым выходом блока и входом второго одновибратора, вторым входом - с выходом второго одновибратора, а третьим входом - с вторым входом второго элемента ИЛИ, с инверсным выходом первого RS-триггера и первым входом третьего элемента И, соединенного вторым входом с выходом инвертора, а выходом - с первым выходом блока, подключенного пятым выходом к первому выходу первого таймера, соединенного вторьи выходом со счетным входом счетчика импульсов, а вторым входом - с С-входом D-триггера, С входом второго таймера и с прямым выходом первого RS-триггера подключенного S-входом к выходу первого элемента ИЛИ, а R-входом - к выходу . счетчика и myльcoв, соединенного установочным входом с выходом второго элемента ИЛИ, причем выход второго таймера подключен к третьему входу первого элемента ИЛИ, а первый вход блока - к входу первого одновибратора, связанного с первыми входами первого и второго узлов сравнения и первым входом дешифратора, соединенного вторым входом с вторыми входами первого и второго узлов сравнения с вторым входом блока, подключенного третьим выходом к выходу первого .узла сравнения, а третьим входом - к третьему входу второго узла сравнения, соединенного выходом с R-входом D-триггера.

сдвигового регистра, связанного сдви- гакш(им входом с выходом элемента НЕ, первым выходом - с первыми входами первых элементов И и ИЛИ, а вторым выходом - с вторым входом первого элемента ИЛИ и первым входом второго элемента И, подключенного выходом к первому входу второго элемента ИЛИ,

связанного вторым входом с выходом

первого элемента И, а выходом - с первым входом преобразователя кодов, соединенного вторым входом с выходом первого элемента ИЛИ, причем первый и второй блоки постоянной памяти сое-

дами первого и второго элементов И, а вход элемента НЕ подключен к выходу элемента запуска.

1 Любое

блок 1 (слу небный)

б/1ОКП- 1

/Данные

б/ioH { (c/{/ e5ftt}{l/)

б/ioM f (с/г /ме6мбШ)

Z

блон

Фи.5

| Патент США № 4347563, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США К 4362103, | |||

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-10-23—Публикация

1985-03-22—Подача