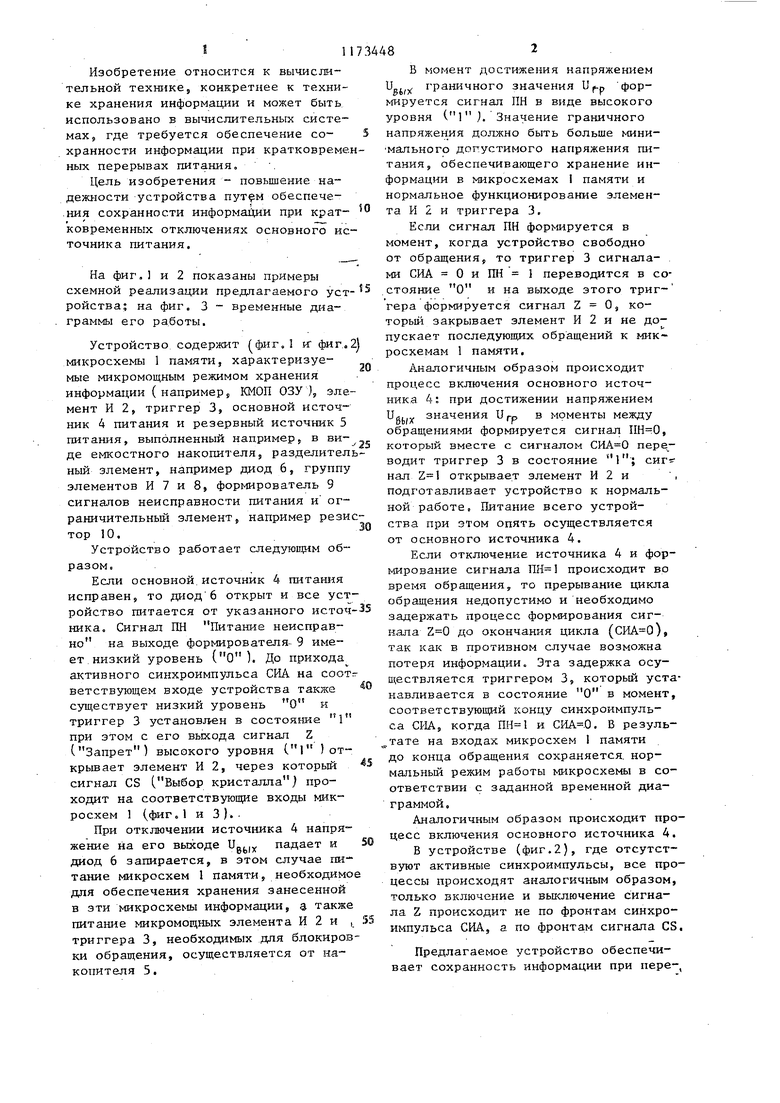

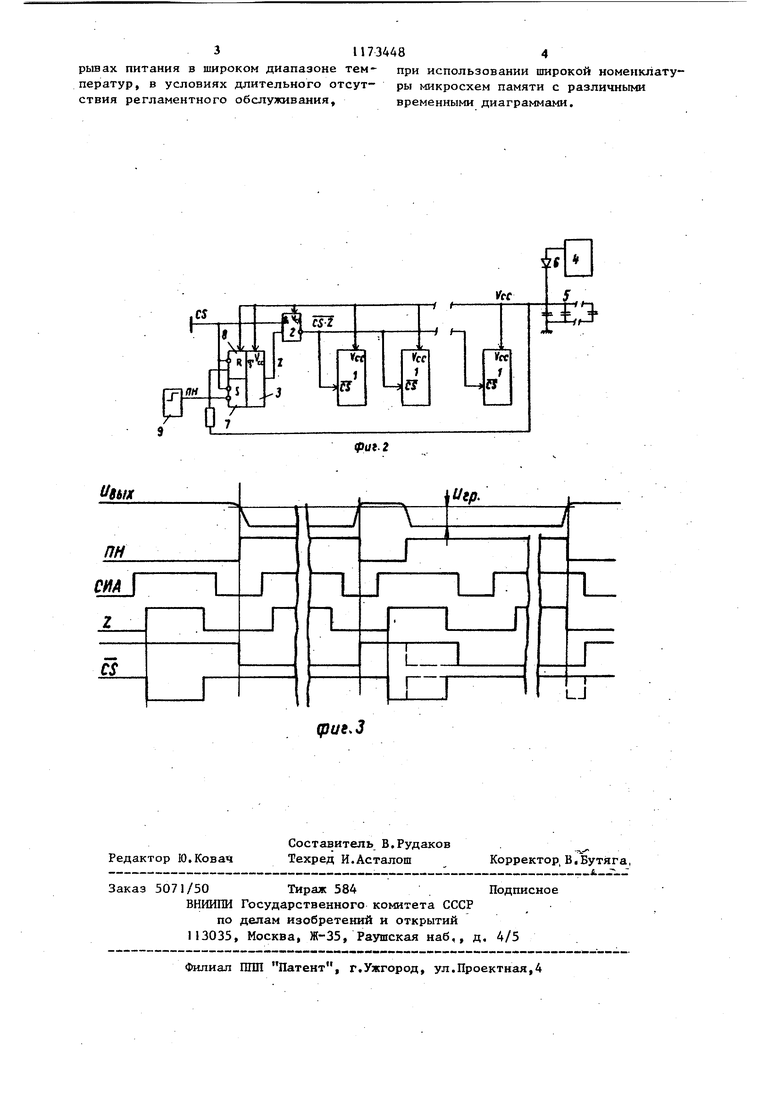

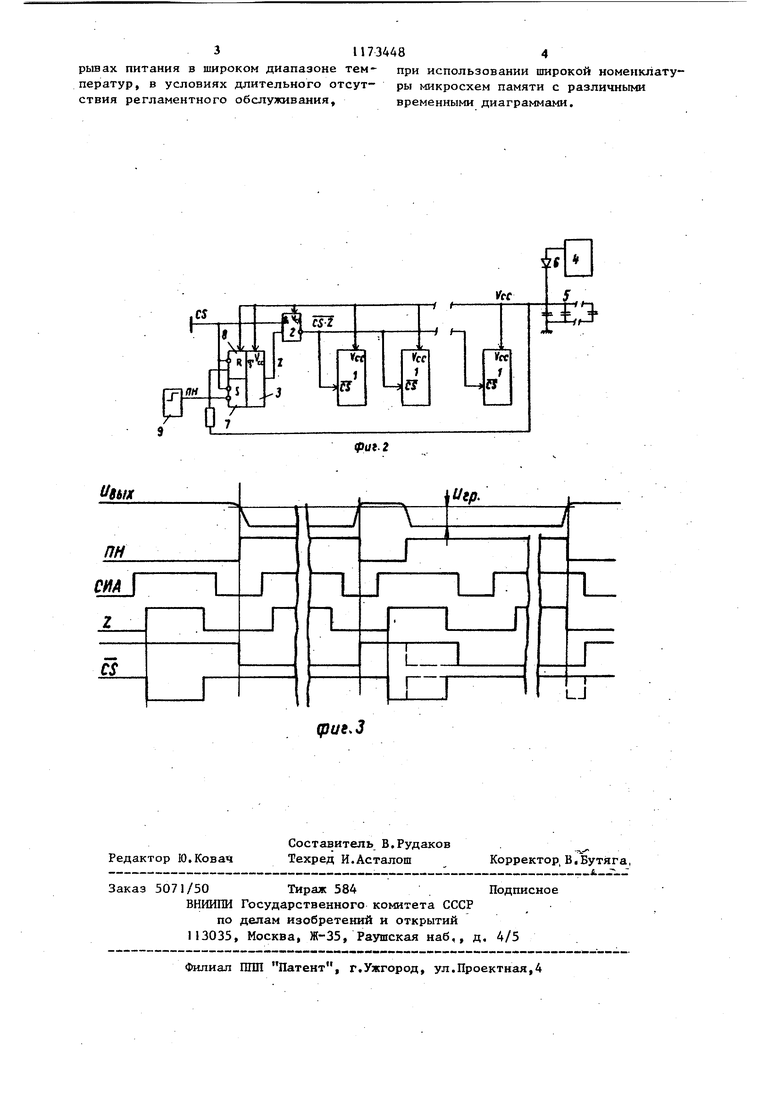

5П Изобретение относится к вычислительной технике, конЕретнее к технике хранения информации и может быть использовано в вычислительных системах, где требуется обеспечение сохранности информации при кратковреме ных перерывах питания. Цель изобретения - повышение надежности устройства обеспече.ния сохранности информации при кратковременных отключениях основного ис точника питания. На фиг.1 и 2 показаны примеры схемной реализации предлагаемого уст ронства; на фиг. 3 - временные диаграммы его работы. Устройство содержит фиг. 1 и фиг, микросхемы 1 памяти, характеризуемые микромощным режимом хранения информации (например, КМОП ОЗУ), эле мент И 2, триггер 3, основной источник 4 питания и резервный источник 5 питания, выполненный например в виде емкостного накопителя, разделител ный элемент, например диод 6, группу элементов И 7 и 8, формирователь 9 сигналов неисправности питания и ограничительный элемент, например рези тор 10. Устройство работает следующим образом. Если основной,источник 4 питания исправен, то диод6 открыт и все уст ройство питается от указанного источ ника. Сигнал ПН Питание неисправно на выходе формирователя- 9 имеет низкий уровень (О). До прихода активного синхроимпульса СИЛ на соот ветствующем входе устройства также существует низкий уровень О и триггер 3 установлен в состояние 1 при этом с его вьпсода сигнал Z (Запрет) высокого уровня (Г )открьшает элемент И 2, через который сигнал CS (Выбор кристалла) проходит на соответствующие входы микросхем 1 (фиг.1 и 3).. При отключении источника 4 напряжение на его выходе и„,,,, падает и вых падает диод 6 запирается, в этом случае тание микросхем 1 памяти, необходимо для обеспечения хранения занесенной в эти микросхемы информации, з также питание микромощных элемента И 2 и триггера 3, необходимых для блокиров ки обращения, осуществляется от накопителя 5. 8 В момент достижения напряжением гР чного значения формируется сигнал ПН в виде высокого уровня (1).Значение граничного напряжен ия должно быть больше минимальногр допустимого напряжения питания, обеспечивающего хранение информации в микросхемах 1 памяти и нормальное функционирование элемента И 2 и триггера 3. ЕС.ПИ сигнал ПН формируется в момент, когда устройство свободно от обращения, то триггер 3 сигналами СИА О и ПН 1 переводится в состояние О и на выходе этого триггера формируется сигнал Z О, который закрывает элемент И 2 и не допускает последующих обращений к микросхемам 1 памяти, Аналогичным образом происходит процесс включения основного источника 4: при достижении напряжением значения U в моменты между обращениями формируется сигнал , который вместе с сигналом nepejводит триггер 3 в состояние сиг нал открывает элемент И 2 и , подготавливает устройство к нормальной работе, Плтание всего устройства при этом опять осуществляется от основного источника 4. Если отключение источника 4 и формирование сигнала ПН происходит во время обращения, то прерывание цикла обращения недопустимо и необходимо задержать процесс формирования сигкала до окончания цикла (), так как в противном случае возможна потеря информации. Эта задержка осуществляется триггером 3, который устанавливается в состояние О в момент, соответствующий концу синхроимпульса CI-IA, когда и СИА.0. В результате на входах микросхем 1 памяти до конца обращения сохраняется, нормальный режим работы микросхемы в соответствии с заданной временной диаграммой. Аналогичным образом происходит процесс включения основного источника 4. В устройстве (фиг.2), где отсутствуют активные синхроимпульсы, все процессы происходят аналогичным образом, только включение и вьжлючение сигнала Z происходит не по фронтам синхроимпульса СИА, а по фронта,м сигнала CS, Предлагаемое устройство обеспечивает сохранность информации при пере-,

3П734484

рывах питания в широком диапазоне тем- при использовании широкой номеиклатуператур, в условиях длительного отсут- ры микросхем памяти с различными ствия регламентного обслуживания, временными диаграммами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Энергонезависимое запоминающее устройство с резервным источником питания | 1985 |

|

SU1381596A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для управления обращением к памяти | 1985 |

|

SU1262494A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Дешифратор | 1988 |

|

SU1596393A1 |

| Устройство для контроля записи информации в блоках памяти | 1982 |

|

SU1076954A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

1. ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МИКРОСХЕМАХ ПАМЯТИ, содержащее основной источник питания, шлход которого через разделительный элемент подключен к входам питания микросхем памяти и выходу резервно, то источника питания, формирователь сигналов неисправности питания и огJ рани 1ительный элемент, отличающееся тем, что, с целью повьшейия надежности устройства, в него в -введены триггер, группа элементов И и элемент И, выход которого подключен к входам выбора кристалла микросхем памяти, один из входов - к выходу триггера, входы которого соединены с выходами элементов И группы, прямой вход первого и первый инверсный вход второго элементов И группы t подключены к выходу формирователя сигналов неисправности питания и через ограничительный элемент соединены с выходом резервного источника пита-ния, причем инверсный вход первого и второй инверсный вход второго элементов И группы являются первым входом устройства, ВТорьм входом которого (. является второй вход элемента И, входы питания триггера и элементов И (Л .соединены с выходом резервного источника питания.I 2.Устройство по п. 1, отличающееся тем, что резервный источник питания выполнен в виде емкостного накопителя. 3,Устройство по п. 2, отличающееся тем, что первый и второй входы устройства объединены. оэ 4 4 СХ

qjue.e

| Огнетушитель | 0 |

|

SU91A1 |

| Под ред | |||

| А.Ю.Гордонова | |||

| М.: Радио и связь, 1981, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| У.Титце и Шенк Полупроводниковая схемотехника | |||

| М.: Мир, 1982, с | |||

| 395 | |||

Авторы

Даты

1985-08-15—Публикация

1983-07-01—Подача