Изобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации для приема последовательности двоичных сигналов, не разделенных паузой.

Целью изобретения является повышение точности приема последовательности двоичных сигналов при искаженных по длительности входных сигналах, .

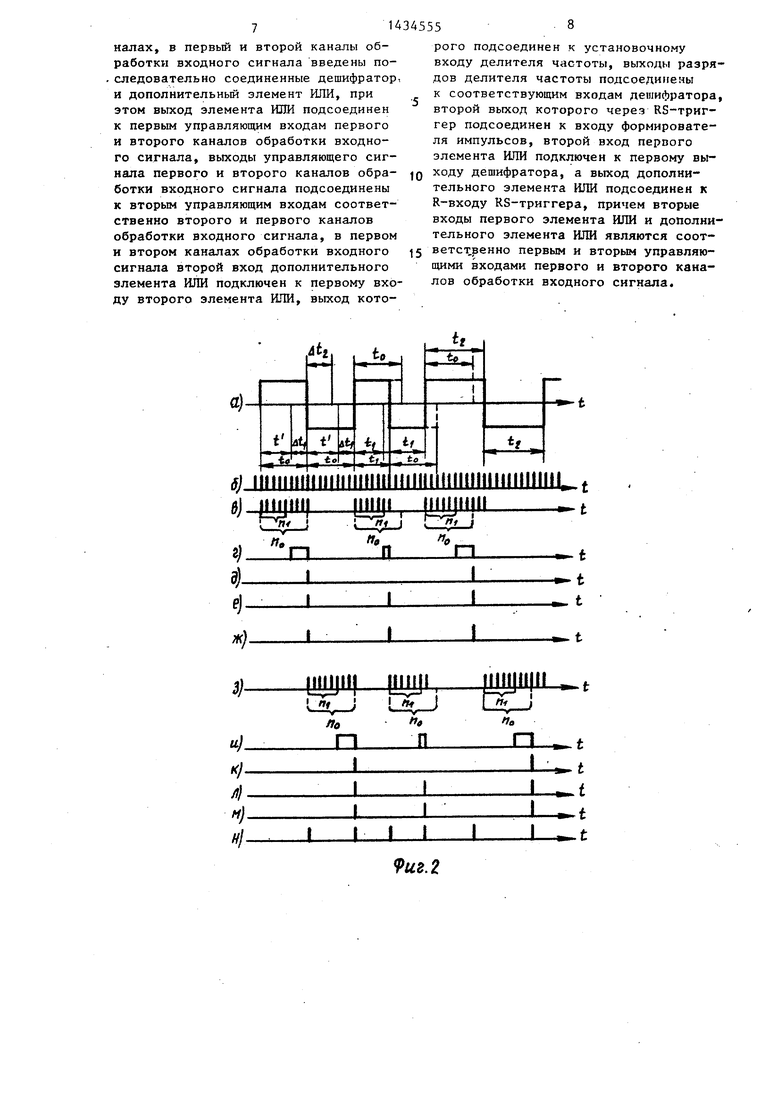

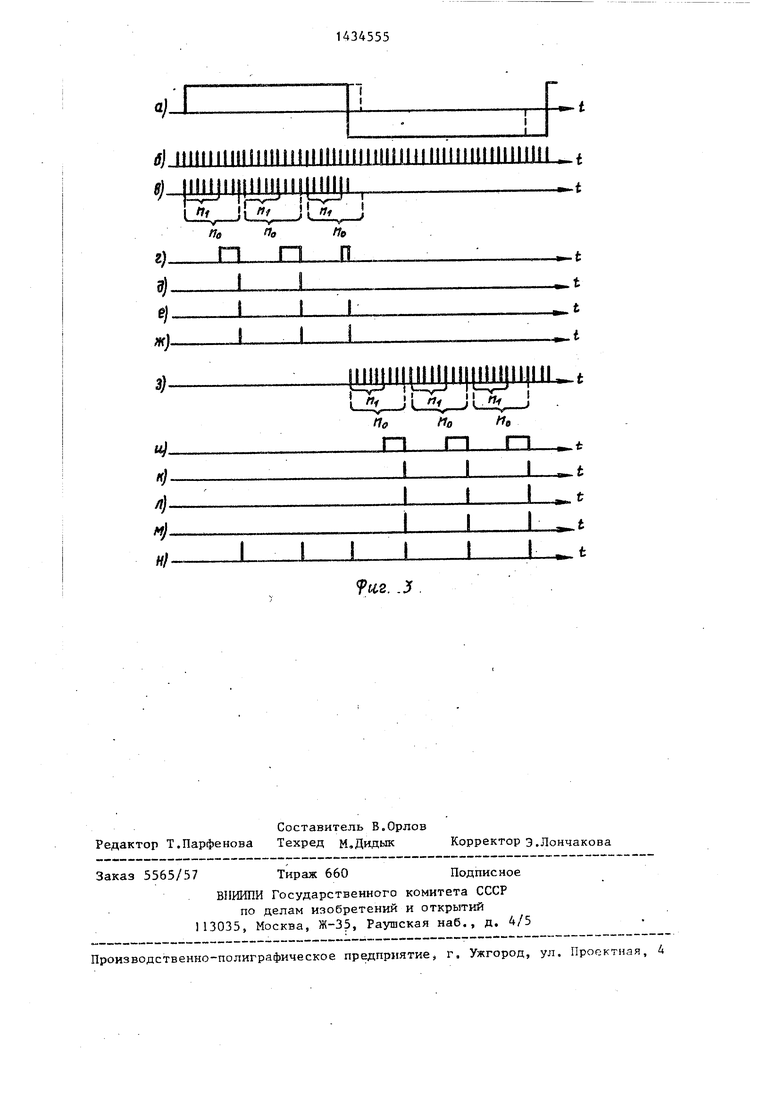

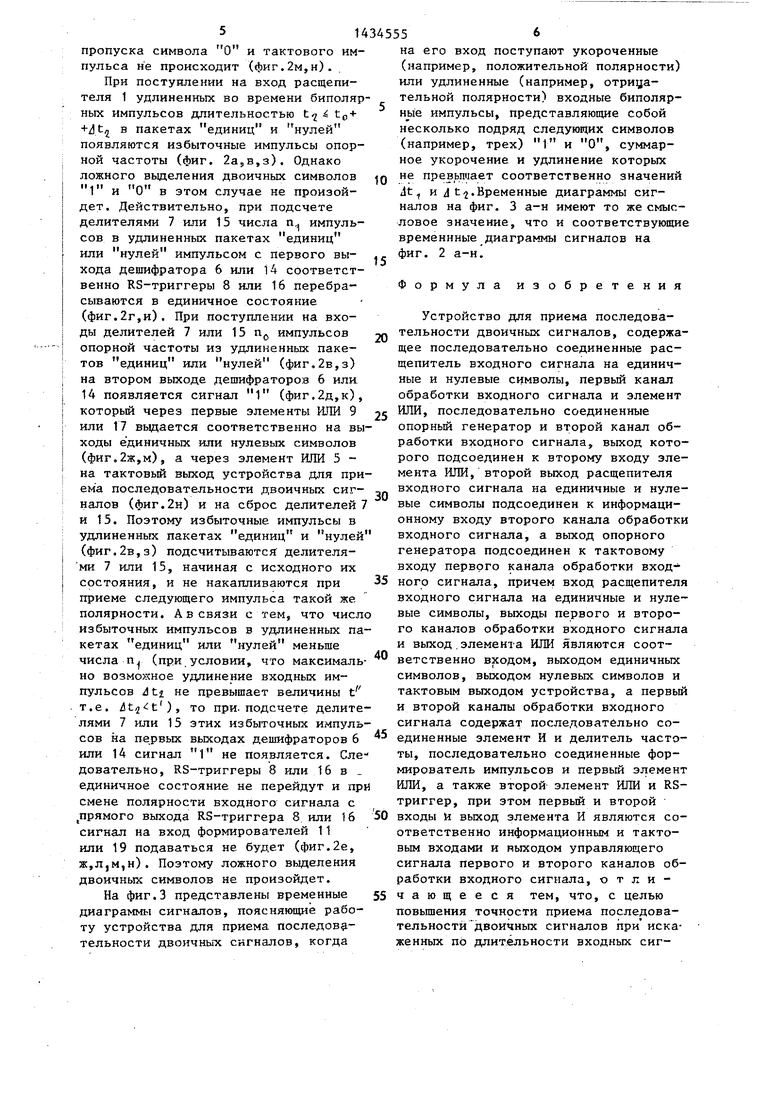

На фиг 1 представлена структурная электрическая схема предлагаемого устройства для приема последовательности двоичных сигналовJ на фиг. 2 и 3 временные диаграммы сигналов, поясняющие работу устройства для приема последовательности двоичных сиг- налов.

Устройство для приема последова- тельности двоичных сигналов содержит расщепитель 1 входного сигнала на единичные и нулевые символы, опорный генератор 2, первый и второй каналы 3 4 обработки входного сигнала, эле- мент ИЛИ 5.

Первый канал 3 обработки входного сигнала содержит дешифратор 6, делитель 7 частоты, RS-триггер 8, первый элемент ИЛИ 9, элемент И 10, фор- мирователь 11 импульсов второй и дополнительный элементы ИЛИ 12 и 13, Второй канал 4 обработки входного сигнала содержит дешифратор 14, делитель 15 частоты, RS-триггер 16, пер- вый элемент ИЛИ 17, элемент И 18, формирователь 19 импульсов, второй и дополнительный элементы ИЛИ 20 и 21.

Устройство для приема последовательности двоичных сигналов работает следующим образом.

На вход 1 асщепителя 1 поступают биполярные, не разделенные паузой, двоичные сигналы (фиг.2а), которые разделяются в нем по полярности. Снимаемые с расщепителя 1 сигналы обрабатываются в первом канале 3 (канале единиц) и во втором канале 4 (канале нулей) которые работают поочередно в зависимости от полярное™ ти поступающих на вход расщепителя 1 биполярных импульсов; При поступлении входного импульса положительной по лярности, соответствующего символу

1 принимаемого сигнала, с выхода единичных символов расщепителя 1 будет подаваться на элемент И 10 сиг нал 1, длительность которого раина длительности входного импульса. На

с

Ю

15

20 5

30 5

0

-

0

5

второй вход элемента И 10 подаются импульсы опорной частоты (фиг.2б), вырабатываемое опорным генератором 2, При этом на: выходе элемента И 10 фор- ми руется пакет импульсов (фиг.2в) - пакет единиц, который поступает на тактобый вход делителя 7 и на первый и второй дополнительные элементы ИЛИ 20 и 21 второго канала 4. При этом первым импульсом пакета единиц RS- триггер 16 и делитель 15 сбрасывают-, ся в нулевое состояние.

Если на .вход расщепителя 1 поступает импульс отрицательной полярности, что соответствует принимаемому символу О, то сигнал 1 будет сниматься со второго выхода расщепителя 1 и подаваться на элемент И 18, на который тдкже поступают импульсы опорной частоты, На выходе элемента И 18 получается пакет -импульсов (фиг.2в) - пакет нулей, который поступает на тактовый вход делителя 15 и на второй и дополнительный элементы ИЛИ. 12 и 13 первого канала 3. При этом первым импульсом пакета нулей RS-триггер 8 и делитель 7 сбрасываются в нулевое состояние.

При поступлении на вход делителя 7 п импульсов опорной частоты из пакета единиц (фиг.2в) на первом вы- ходе дешифратора 6 появляется сигнал 1, который поступает на Б-вход RS- Триггера 8 и перебрасывает его в единичное состояние (фиг.2г). При этом с прямого выхода RS-триггера 8 поступает сигнал высокого уровня на вход формирователя.

Второй канал 4 работает аналогично первому каналу 3 при поступлении на вход расщепителя 1 импульса отрицательной полярности. А именно, при подсчете делителем 15 п импульсов из пакета нулей (фиг.2в) на первом выходе дешифратора 14 появляется сиг нал, который перебрасывает RS-триггер 16 в единичное состояние (фиг.2и) При этом с прямого вь1хода RS-триггера 16 на вход формирователя 19 поступает сигнал высокого уровня.

Количество импульсов п, содержащихся в пакетах единиц или пакетах нулей и отсчитываемых делителями 7 или 15, при котором на neiJabix выходах дешифраторов 6 или 14 появляется сигнал 1, определяется числом импульсов п опорной частоты (фиг.2в, з), которые укладываются на интернале времени t

(0,5-0,8)trt, где tn - номинальная

Вели- -f 5

15

20

, например, равном t Lg, где tp

.длительность входных импульсов, чина интервала времени t to-/lt выбирается, исходя из величины максимально возможного укорочения по времени ut входных импульсов (фиг.2а).

Сигнал 1 на вторых вькодах дешифраторов 6 или 14 появляется при по- Q отуплении на тактовые входы делителей 7 или 15 числа импульсов п опорной частоты (фиг.2в,э), укладывающихся на интервале времени t, Данный сигнал со вторых выходов дешифраторов 6 или 14 подается соответственно через элементы ИЛИ 9 и 17 на выходы первого канала 3 (фиг.2д) и второго канала 4 (фиг.2к) в качестве принятых символов 1 и О соответственно, а через дополнительные элементы ИЛИ 13 и 21 - на R-входы RS-тригге- ров 8 или 16, переводя их в нулевое

состояние. RS-триггер 8 переводится также из единичного состояния в нулевое (фиг.2г) при каждой смене полярности (с положительной на отрицательную) входного сигнала первым строб-импульсом из пакета нулей (фиг.2з), подаваемого с выхода элемента И 18 через элемент ИЖ 13 в момент приема импульса отрицательной полярности. Этим же строб-импульсом через второй элемент ИЛИ 12 делитель 7 сбрасывается в нулевое состояние. Аналогичным образом RS-триггер 16 также переводится из единичного в нулевое состояние при каждой смене полярности (с отрицательной на положительную) входного сигнала первым .« строб-импул ьсом из пакета единиц, подаваемого с выхода элемента И 10 через второй дополнительный элемент ИЛИ 21 в момент приема входного импульса положительной полярности.

Этим же строб-импульсом через второй элемент ИЛИ 20 делитель 15 сбрасывается в нулевое состояние.

При переходе RS-триггеров 8 или 16 из единичного в нулевое состояние на выходе формирователей 11 или 19 по- является сигнал 1 (фиг.2е,л), который через первые элементы ИЛИ 9 или 17 соответственно поступает на выходы первого и второго каналов 3 и 4. Таким образом, импульсы, появляющиеся на выходах первых элементов ИЛИ 9 и 17 (фиг.2ж,м), являются принимаемыми двоичными символами 1 и О со25

30

35

45

55

- 5

15

20

й

.«

6ответственно, которые на выходе элемента ИЛИ 5 образуют тактовые импульсы (фиг.2н). При этом каждым импульсом тактовой частоты через вторые элементы ШШ 12 и 20 делители 7 и 15 сбрасываются в нулевое состояние.

Если длительности.поступающих на вход расщепителя 1 импульсов (фиг.2а) равны номинальному значению t, то работа первого и второго каналов 3 и 4 происходит в соответствии с изложенным. При этом импульсы с выходов первых элементов ШШ 9 и 17, соответствующие принятым символам 1 и О (фиг.2ж,м), поступают на элемент ИЛИ 5, на выходе которого формируются тактовые импульсы (фиг.2н), являющиеся одновременно и импульсами сброса делителей 7 и 15 в нулевое состояние.

Если на вход расщепителя 1 поступает укороченный по времени входной импульс, например, положительной по- 25 лярности (фиг.2а), длительность кото30

35

45

55

единиц

рого t t, то в пакете (фиг.2п), поступающем на делитель 7, будет недоставать до числа Пд нескольких импульсов и поэтому на втором выходе дешифратора 6,и на выходе первого элемента ШШ 9 сигнал 1 появиться не может (фиг.2д). Однако пропуска символа 1 в этом случае не произойдет по следующей причине. При подсчете делителем 7 частоты числа п импульсов в укороченном пакете единиц (фиг.2в) на первом выходе дешифратора 6 появляется сигнап, который перебрасывая RS-триггер 8 в единичное состояние (фиг.2г), а так как при приеме следующего импульса (отрицательной полярности) происходит смена полярности входного сигнала с + на -, то первым строб-импульсом с выхода элемента И 18 (фиг.2з) RS-триггер 8 переходит в нулевое состояние. При этом с выхода формирователя 11 (фиг.2е) через элемент ИЛИ 9 выделяется символ 1 и тактовый импульс (фиг.2ж,н), а делители 7 и 15 сбрасываются в нулевое состояние.

Аналогичньм образом происходит выделение символа О и тактового импульса (фиг. 2л,м,н) во втором канале 4 при поступлении на вход рас- щепителя 1 укороченного по времени импульса отрицательной полярности (фиг.2а,з) длительностью t 7/t и

пропуска символа О и тактового импульса не происходит (фиг.2м,и).

При поступлении на вход расщепителя 1 удлиненных во времени биполярных импульсов длительностью t t(,+ +At в пакетах единиц и нулей появляются избыточные импульсы опорной частоты (фиг. 2а5В,з). Однако ложного выделения двоичных символов 1 и О в этом случае не произойдет. Действительно, при подсчете делителями 7 или 15 числа п импульсов в удлиненных пакетах единиц или нулей импульсом с первого выхода дешифратора 6 шш 14 соответственно RS-триггеры 8 или 16 перебрасываются в единичное состояние (фиг.2г,и). При поступлении на входы делителей 7 или 15 п импульсов

опорной частоты из удлиненных пакетов единиц или нулей (фиг.2в,з) на втором выходе дешифраторов 6 или. 14 появляется сигнал 1 (фиг.2д,к), который через первые элементы ИЛИ 9 или 17 вьщается соответственно на выходы е диничных или нулевых символов (фиг.2ж,м), а через элемент РШИ 5 - на тактовый выход устройства для приема последовательности двоичных сиг- налов (фиг.2н) и на сброс делителей 7 и 15. Поэтому избыточные импульсы в удлиненных пакетах единиц и нулей (фиг.2в,з) подсчитываются делителя- ми 7 или 15, начиная с исходного их состояния, и не накапливаются при приеме следующего импульса такой же полярности. А в связи с тем, что число избыточных импульсов в удлиненных пакетах единиц или нулей меньше числа п (при условии, что максимально возможное удлинение входных импульсов 1 ti не превышает величины t т.е. ), то при. подсчете делителями 7 или 15 этих избыточных импульсов на первых выходах дешифраторов 6 или 14 сигнал 1 не появляется. Следовательно, RS-триггеры 8 или 16 в единичное состояние не перейдут и при смене полярности входного сигнала с прямого выхода RS-триггера 8 или 16 сигнал на вход формирователей 11 или 19 подаваться не будет (фиг.2е, ж,л,м,н). Поэтому ложного выделения двоичных символов не произойдет.

На фиг.З представлены временные диаграммы сигналов, поясняющие работу устройства для приема последов - тельности двоичных сигналов, когда

5

0

5 5

0

5

0

5

на его вход поступают укороченные (например, положительной полярности) или удлиненные (например, отрицательной полярности) входные биполярные импульсы, представляющие собой несколько подряд следующих символов (например, трех) 1 и О, суммарное укорочение и удлинение которых не превышает соответственно значений At и Jt.Временные диаграммы сигналов на фиг. 3 а-н имеют то же смысловое значение, что и соответствующие временнные диаграммы сигналов на фиг. 2 а-н.

Формула изобретения

Устройство для приема последовательности двоичных сигналов, содержащее последовательно соединенные расщепитель входного сигнала на единичные и нулевые символы, первый канал обработки входного сигнала и элемент ИЛИ, последовательно соединенные опорный генератор и второй канал обработки входного сигнала, выход которого подсоединен к второму входу элемента ИЛИ, второй выход расщепителя входного сигнапа на единичные и нулевые символы подсоединен к информационному входу второго канала обработки входного сигнала, а выход опорного генератора подсоединен к тактовому входу первого канала обработки входного сигнала, причем вход расщепителя входного сигнала на единичные и нулевые символы, выходы первого и второго каналов обработки входного сигнала и выход.элемента ИЛИ являются соответственно входом, выходом единичных символов, выходом нулевых символов и тактовым выходом устройства, а первый и второй каналы обработки входного сигнала содержат последовательно соединенные элемент И и делитель частоты, последовательно соединенные формирователь импульсов и первый элемент ИЛИ, а также второй элемент ИЛИ и RS- триггер, при этом первый и второй входы и выход элемента И являются соответственно информационным и тактовым входами и выходом управляющего сигнапа первого и второго каналов обработки входного сигнала, отличающееся тем, что, с целью повьш1ения точности приема последовательности двоичных сигналов при искаженных по длительности входных сиг5

71А34555

налах, в первый и второй каналы обработки входного сигнала введены по- следовательно соединенные дешифратор, и дополнительный элемент ИЛИ, при этом выход элемента ИЛИ подсоединен к первым управляющим входам первого и второго каналов обработки входного сигнала, выходы управляющего сигнала первого и второго каналов обработки входного сигнала подсоединены к вторым управляющим входам соответственно второго и первого каналов обработки входного сигнала, в первом втором каналах обработки входного сигнала второй вход дополнительного лемента ИЛИ подключен к первому вхоу второго элемента ИЛИ, выход котовхдо к вт ге ля эл

10 О те Rвхте

15 ве ци ло

5

. 8

рого подсоединен к установочному входу делителя частоты, выходы раэря- дов делителя частоты подсоединены к соответствующим входам дешифратора, второй выход которого через RS-триг- гер подсоединен к входу формирователя импульсов, второй вход первого элемента ИЛИ подключен к первому дешифратора, а выход дополнительного элемента ИЛИ подсоединен к Rвходу RS-триггера, причем вторые входы первого элемента ИЛИ и дополнительного элемента ИЛИ являются соответст,ренно первым и вторьт управляю- цими входами первого и второго канаов обработки входного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема последовательности двоичных сигналов | 1985 |

|

SU1343557A1 |

| Устройство для контроля качества канала связи | 1979 |

|

SU856023A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ПОСЛЕДОВАТЕЛЬНОСТИ ДВОИЧНЫХ СИГНАЛОВ | 1970 |

|

SU261449A1 |

| Устройство для измерения характеристик дискретного канала связи | 1990 |

|

SU1741278A1 |

| Селектор импульсов по длительности | 1984 |

|

SU1221733A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

| Преобразователь двоичного сигнала в пятиуровневый сигнал | 1983 |

|

SU1172044A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Преобразователь кодов | 1987 |

|

SU1444957A1 |

| ВЕДОМСТВЕННАЯ СИСТЕМА ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА | 2016 |

|

RU2650191C1 |

Изобретение относится к электросвязи. Цель изобретения - повьшение точности приема последовательности двоичных сигналов при искаженных по длительности входных сигналах. Устр- во содержит расщепитель 1 входного сигнала на единичные и нулевые символы, опорный г-р 2, эл-т ИЛИ 5 и два канала 3 и 4 обработки входного сигнала, состоящие из дешифраторов 6 и 14, делителей 7 и 15 частоты, RS- триггеров 8 и 16, эл-тов ИЛИ 9, t2, 13 и 17, 20, 21, эл-тов И 10 и 18 и формирователей 11 и 19 импульсов. Цель достигается за счет устранения ложного выделения двоичных символов при поступлении на вход устр-ва укороченных (положительной полярности) или удлиненных (отрицательной полярности) биполярных импульсов, представляющих собой несколько подряд следующих символов (трех) 1 и О, су:-1марное укорочение и удлинение которых не превышает заданных значений. 3 ил. (Л с « ел О1 СП Фиг.1

9иг.2

tf) ItllllllinnitiiiHHillMilliiniHlHinitnilllllll ,

. .5

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 0 |

|

SU319096A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ПОСЛЕДОВАТЕЛЬНОСТИ ДВОИЧНЫХ СИГНАЛОВ | 0 |

|

SU261449A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-10-30—Публикация

1987-02-03—Подача