IT

(Л

Vffoy eHn jfumaffu

13-

4 00

00 Од

Фт1

Изобретение относится к области программного управления и может быть использовано для управления технологическим оборудованием.

Цель изобретения состоит в расширении функциональных возможностей устройства за счет увеличения разрядности кода управления.

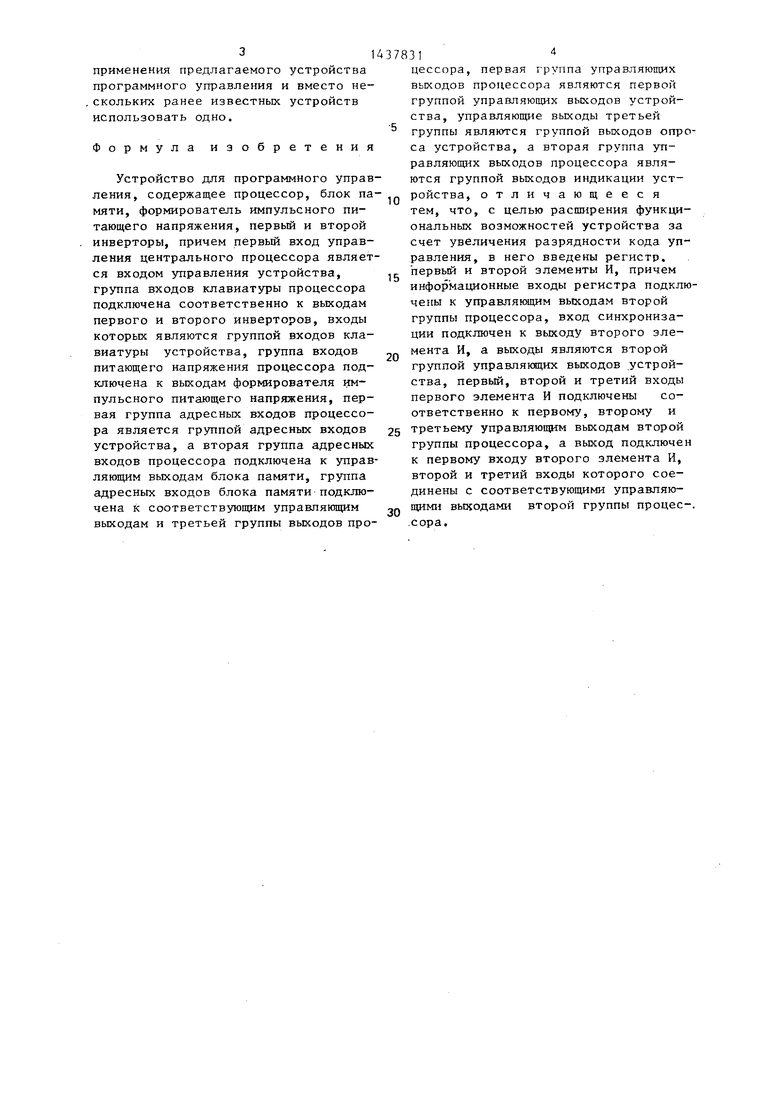

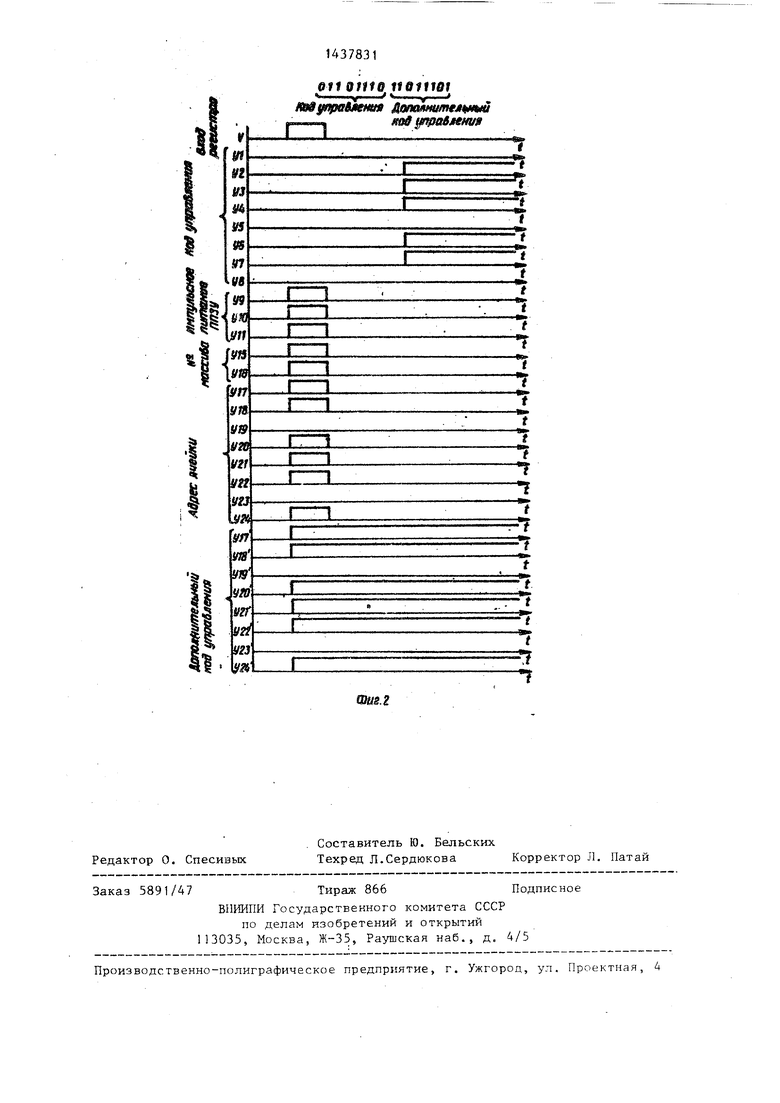

На фиг, 1 показана функциональная схема устройства; на фиг. 2 - временные диаграммы его работы.

Устройство {фиг.1) содержит процессор 1, блок 2 памяти, регистр 3, формирователь 4 импульсного питаю- щего напряжения, первый и второй инверторы группы 5, пс/, вый 6 и второй .7 элементы И, входы 8 10 и выходы 11,12 процессора и выходы 13 регистра На фиг. 1 показаны: группа входов клавиатуры центрального процессора К1 и К2, первая группа адресных входов процессора XI-Х4, вторая группа адресньгх входов процессора Х5-Х12 , первая группа У1-У9, вторая группа У9-У16, третья группа У17-У23 управляющих выходов процессора, группа адресных входов А1-А10 блока памяти, группа входов питающего напряжения процессора Ф1-Ф4.

Устройство работает следующим образом.

Емкость используемого блока памяти - 1024 восьмиразрядных слов, Этот объем памяти можно условно разбить на четыре массива по 256 восьмиразрядных слов в каждомо При такой организации выбор необходимого массива определяется одним из четырех двоичных чисел, составленных из девятого и де сятого разрядов шины адреса. Например первьй массив задается комбинацией из логических нулей на выходах У15 и У16 процессора 1, а четвертый - комбинацией логических единиц на тех же выходах. Выходы процессора 1 У15 и У16 подключаются к двум входам элемента ЗИ 7, к третьему входу подключается выход элемента ЗИ 6. Таким образом, при обращении процессора 1 к четвертому массиву блока 2 памяти на синхровход V регистра 3 подается синхроимпульс и в запоминающий регистр записьшается восьмиразрядное двоичное число, соответствующее номе ру яче;йки четвертого массива, К которому произошло обращение. Двоичное восьмиразрядное число, записанное в регистр 3, устанавливается на его

выходе и представляет собой дополнительный код управления. Таким образом, к программно устанавливаемому двоичному восьмиразрядному коду управления, имеющемуся в модуле контроллера МК-1807, добавляется дополнительный восьмиразрядный программно устанавливаемый двоичный код управления.

Для использования адресных выходов для выдачи дополнительного кода управления необходимо ввести и управляющую программу, там, где это требуется, обращение к 3-му массиву, который соответствует требуемому дополнительному коду управления, В ячейке 3. массива с адресом, равным дополнительному коду управления, должна стоять команда 5,0.

Пример. Пусть необходимо получить полный код управления:

0110111011011101

КУ 66доп КУ 5.5.

При этом первые 8 разрядов будут выдаваться на шину кода управления (КУ), а вторые 8 разрядов - на адресную шину.

Фрагмент программы, позволяющей вьтолнить это, будет имет.., вид: 5.3- 5,5 - команда обращения к подпрограмме в 3 массиве по адресу 5,5.

4.1 - 6.6 - команда выдачи КУ, равного 6.6,

д

5

в 3 массиве в ячейке 5.5 будет команда 5.0.

, Запись 5., 4,, 6. означает в соответствии с требованиями инструкции по программированию ЗУ для БИС К145 ИК 1807, представление в шестнадцатиричной системе числа 13/,,;

,2(,о), 1(о)

Устройство позволяет осуществить реализацию функции управления по по- вьш1енному числу дискретных каналов. По сравнению с прототипом на 11 каналов больше, а в общем случае на п-1 каналов, где п - число разрядов адресной шины процессора. Повышение числа дискретных каналов управления в предлагаемом устройстве дает возможность в программируемых системах управления устранить временное рассогласование между установкой основного кода управления и дополнительного, что необходимо, например, для синхронного управления объектом. Это дает возможность расширения области

применения предлагаемого устройства программного управления и вместо не- скольких ранее известных устройств использовать одно.

Формула изобретения

Устройство для программного управения, содержащее процессор, блок памяти, формирователь импульсного питающего напряжения, первый и второй инверторы, причем первый вход управения центрального процессора является входом управления устройства, группа входов клавиатуры процессора подключена соответственно к выходам первого и второго инверторов, входы которых являются группой входов клавиатуры устройства, группа входов питающего напряжения процессора подключена к выходам формирователя IJM- пульсного питающего напряжения, первая группа адресных входов процессора является группой адресных входов устройства, а вторая группа адресных входов процессора подключена к управяющим выходам блока памяти, группа адресных входов блока памяти подклюена к соответствующим управляющим выходам и третьей группы выходов про0

5

5

0

цессора, первая группа управляющих выходов процессора являются первой группой управляющих вьсходов устройства, управляющие выходы третьей группы являются группой выходов опроса устройства, а вторая группа уп- равляюгцих выходов процессора являются группой выходов индикации устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет увеличения разрядности кода управления, в него введены регистр, первый и второй элементы И, причем информационные входы регистра подключены к управляющим выходам второй группы процессора, вход синхронизации подключен к выходу второго элемента И, а выходы являются второй группой управляющих выходов устройства, первый, второй и третий входы первого элемента И подключены соответственно к первому, второму и третьему управляющим выходам второй группы процессора, а выход подключен к первому входу второго элемента И, второй и третий входы которого соединены с соответствующими управляющими выходами второй группы процес-. .сора.

Oil вП1в 11011161

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| Вычислительное устройство | 1984 |

|

SU1280611A1 |

| Ассоциативное запоминающее устройство | 1987 |

|

SU1501164A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1259262A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Устройство для измерения временных параметров программ | 1982 |

|

SU1136109A1 |

Изобретение относится к области программного управления и может быть использовано для управления технологическим оборудованием. Цель изобретения состоит в расширении функциональных возможностей устройства за счет увеличения разрядности кода управления. Поставленная цель достигается тем, что в известное устройство, содержащее процессор 1 и блок памяти 2, введены регистр 3, первый 6 и второй 7 элементы И. Введение указанных элементов позволило осуществить функции управления по повьппенному числу дискретных каналов, что дает возможность в программируемых системах уп- равления устранить временное paccoi- ласование между установкой основного кода управления и дополнительного. 2 ил. (О

| Модуль контроллера | |||

| Усилитель двойного действия с одновременным усилением высокой и низкой частоты | 1923 |

|

SU1807A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПО Кристалл | |||

| Киев, 1984. | |||

Авторы

Даты

1988-11-15—Публикация

1987-05-06—Подача