U

00

ч

со

Изобретение относится к нычисли- тельной технике и может быть испол.Ь зовано для построения электронных вычислительных машин.

Целью изобретения является шение информационной емкости ки памяти„

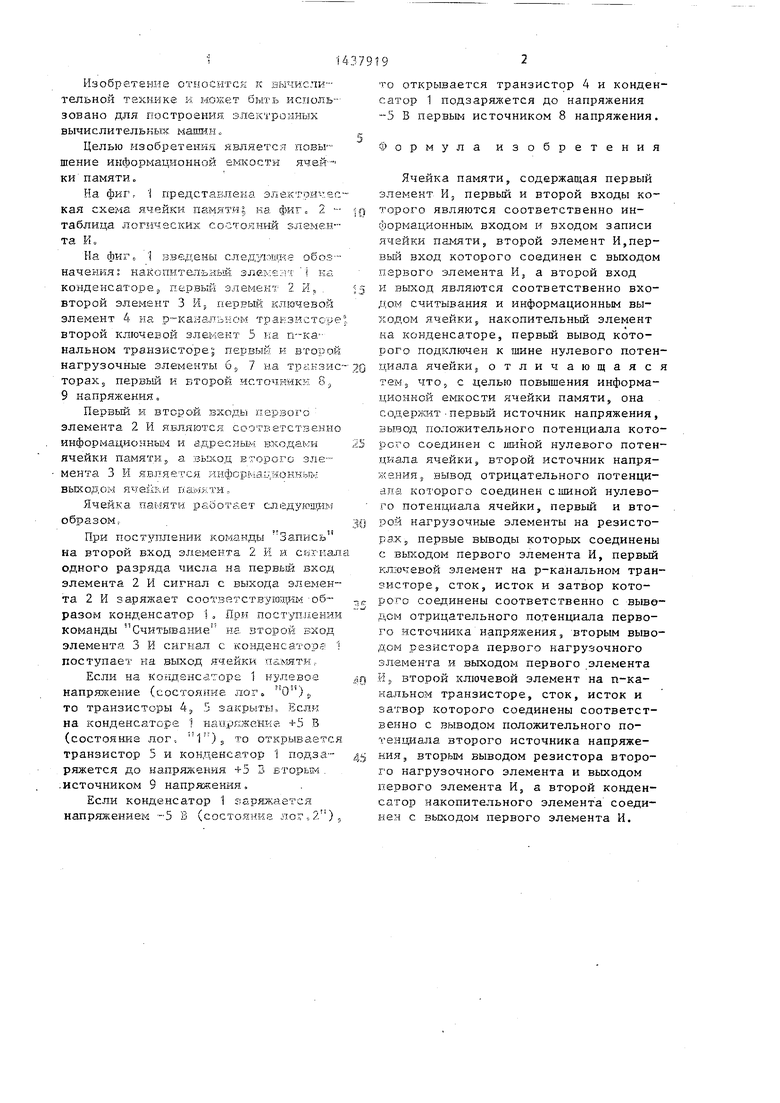

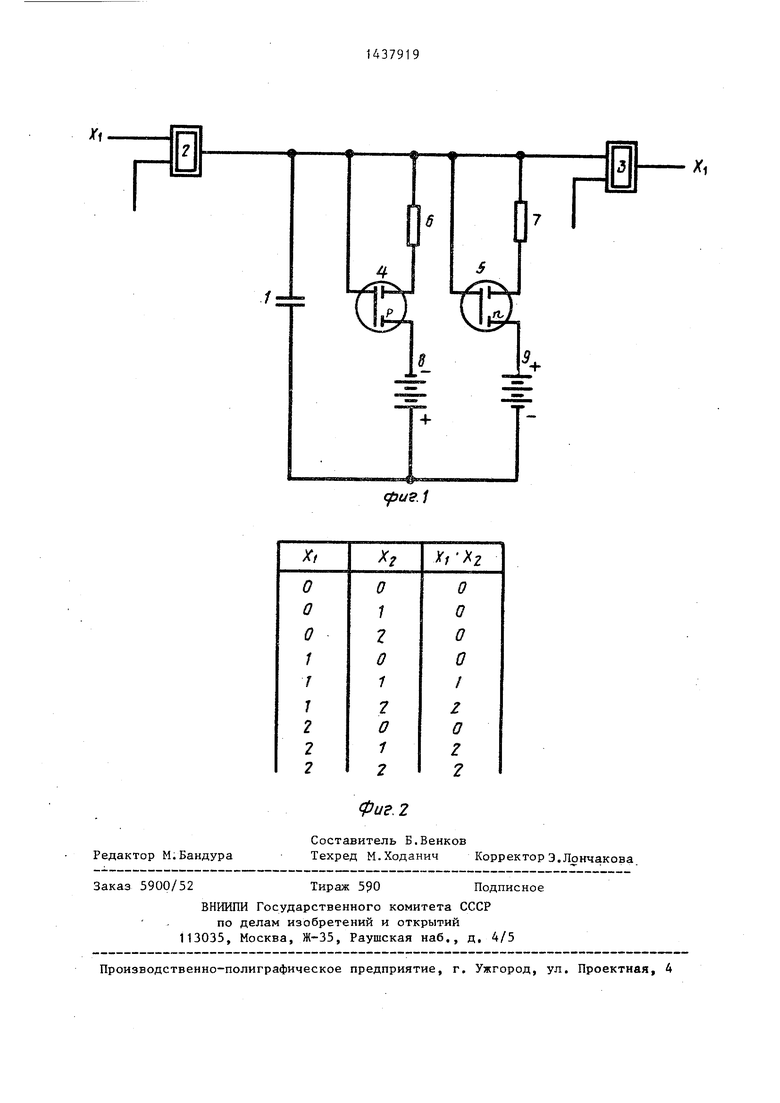

На фиг, 1 представлека электончхее кая схема ячейки памяти I ка фиг. 2 таблица логических состояний элемента И.

На фиг о 1 в:ее;декы след ажа-хе обоз™ начення: накопительный злеке:г Т i ка конденсаторе., первый элемент 2 И, . второй элемент 3 И пернью: ключевой элемент 4 ка р-канальном транзисторе второй ключевой элемент 5 ка гг-ка- нальном транзисторе; первый, и второй нагрузочные элементы 6, 7 на трг1кзис торахэ первьш и второй иг.точ.никк 8j 9 напряжения,

Первый и второй входы первого элемента 2 И являются соответственно информационньм и адресным в: содами ячейки памяти5 а выход второго мента 3 И является информационным выходом .и памяти,

Ячейка памяти работает следуюар1м образом,

При поступлении команды Запись на второй вход элемента 2 И и сигнал одного разряда числа на первый вход элемента 2 И сигнал с выхода элемента 2 И заряжает соответствуюз.тим об- разом конденсатор 1 , При пост ттлении команды Считывание не второй вход элемента 3 И сигнал с конденсатора 1 поступает на выход ячейки палшти,

Если на конденсаторе 1 нулевое напряжение (состояние лог 0.)„ то транзисторы 4, 5 закрыты. Если на конденсаторе 1 нах1ркжение +5 В (состояние лог.. Г )э то открывается транзистор 5 и конденсатор 1 подза- ряжется до напряжения +5 5 вторым . .источником 9 напряжения.

Если конденсатор 1 заряжается напряжением -5 В (состояние лог, 2),

то открывается транзистор 4 и конденсатор 1 подзаряжется до напряжения --5 В первым источником 8 напряжения.

Формула изобретения

Ячейка памяти, содержащая первый элемент И. первый и второй входы которого являются соответственно информационным входом и входом записи ячейки памяти, второй элемент И,первьш вход которого соединен с выходом первого элемента И, а второй вход и выход являются соответственно входом считывания и информационным выходом ячейки 5 накопительньш элемент на конденсаторе, первьш вывод которого подключен к шине нулевого потенциала ячейки; отличающаяс теМэ что, с целью повышения информационной емкости ячейки памяти, она coдepжliт первый источник напряжения, зьшод положительного потенциала которого соединен с шиной нулевого потен циа.ла ячейки, второй источник напряжения вы-вод отрицательного потенци- апа которого соединен с шиной нулевого потенциала ячейки, первый и второй нагрузочные элементы на резисторах 5, первые выводы которых соединены с вьжодом первого элемента И, первый ключевой элемент на р-канальном транзисторе, сток, исток и затвор которого соед.инены соответственно с выводом отрицательного потенциала первого источника напряжения, вторым выводом резистора первого нагрузочного элемента и выходом первого элемента И, второй ключевой элемент на п-ка- на.льном транзисторе, сток, исток и затвор которого соединены соответственно с выводом положительного потенциала второго источника напряжения, вторым выводом резистора второго нагрузочного элемента и выходом первого элемента И, а второй конденсатор накопительного элемента соединен с выходом первого элемента И.

JTf

ua

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Ячейка памяти для регистра сдвига | 1974 |

|

SU1327186A1 |

| Аналоговое запоминающее устройство | 1986 |

|

SU1396159A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

| Электронное устройство | 1987 |

|

SU1427518A2 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU957275A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Ячейка памяти | 1987 |

|

SU1451776A1 |

Изобретение относится к вычислительной технике и можег быть использовано для построения злектроннр-вы- числительных машин. Целью изобретения является повьш1ение информационной плотности ячейки памяти. Поставленная цель достигается тем, что ячейка памяти содержит первый и второй источники напряжения, первый и второй ключевые элементы соответственно на р-канальном и п-канальном транзисторах, первый и второй нагрузочные элементы на резисторах, накопительный элемент на конденсаторе. При состоянии ячейки памяти, равном лог. О, напряжение на конденсаторе равно нулю, при состояниях лог.1 и лог.2 напряжение на конденсаторе равно соответственно +5 В и -5 В. 2 ил. о (Л

Редактор M.Бандура

Составитель Б.Венков

Техред М.Ходанич КорректорЭ.Лончакова

(flUS.I

фиг. 2

| Дроздов Е.А., Комарницкий В.А, Пятибратов А.П | |||

| Электронные вычислительные машины единой системы | |||

| М.: Машиностроение, 1981, с | |||

| ПРИБОР ДЛЯ НЕФТЯНОГО ОТОПЛЕНИЯ ПЕЧЕЙ | 1923 |

|

SU648A1 |

| Соколов Т.Н., Васильев Ф.А | |||

| Ферри- товые логические элементы и узлы информационных систем | |||

| Л.: Лениградская военная инженерная академия им | |||

| Можайского, 1970, с | |||

| Автоматическая акустическая блокировка | 1921 |

|

SU205A1 |

Авторы

Даты

1988-11-15—Публикация

1986-11-25—Подача