ft 2l,.) If Iff t --tfyss

(Л

Ctn-«

00

CO

00

to

Изобретение относится к импульсной технике и предназначено для использования в устройствах обработки число-импульсной информации.

Цель изобретения - повышение точности устройства,

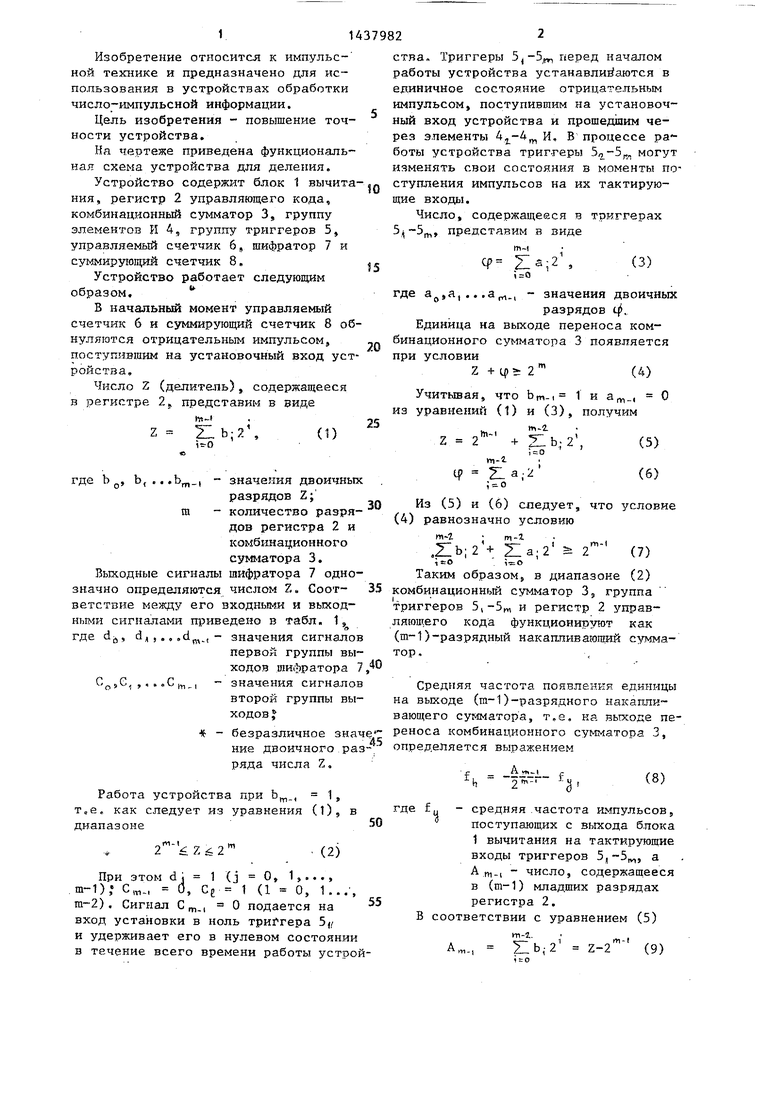

На чертеже приведена функциональная схема устройства для деления.

Устройство содержит блок 1 вычита ния, регистр 2 управляющего кода, комбинационный сумматор 3, группу элементов И А, группу триггеров 5, управляемый счетчик 6,, шифратор 7 и cy itмиpyющий счетчик 8,

Устройство работает следующим образом.

В начальный момент управляемый счетчик б и суммирующий счетчик 8 обнуляются отрицательным импульсом, поступившим на установочный вход устройства.

Число Z (делитель), содержащееся в регистре 2, представим в виде

.

Z Z:b;2

(1)

ш

значения двоичных разрядов Z;

количество разрядов регистра 2 и комбинационного сумматора 3.

сигналы шифратора 7 однозначно определяются числом Z, Соот- 35 комбинационный сумматор 3 группа

-.«

379822

ства« Триггеры , перед началом работы устройства устанавливаются в единичное состояние отрицательньЕм импульсом, поступившим на установочный вход устройства и прошедшим через элементы 4.-4 И, В процессе работы устройства триггеры могут изменять свои состояния в моменты поступления импульсов на их тактирующие входы.

Число, содержащееся в триггерах 5 -5,, представим в виде

тч . Я Za;2 , (3)

15

где а„,а.

.а

rrt-i

- значения двоичны

разрядов qi. Единица на выходе переноса комбинационного сумматора 3 появляется при условии

(4)

О

Z + М)5: 2 Учитывая, что Ь,

и а

из уравнений (1) и (3), получим

5

Z 2

m-2.

0

П1-1

ч Z1 а ; 2 ; о

Из (5) и (6) следует, (4) равнозначно условию m-Z : m-i

(5) (6)

что условие

.Z:b;2 -b а;2 S. 2 (7) 1 :О

Таким образомJ в диапазоне (2)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2013 |

|

RU2517322C1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

Изобретение относится к импульсной технике и предназначено для использования в устройствах обработки число-импульсной информации. Цель изобретения - повьш1ение точности устройства. Устройство для деления содержит блок вычитания 1, регистр 2 управляющего кода, комбинационный сумматор 3, группу элементов И 4, группу триггеров 5, управляемый счетчик 6, шифратор 7 и суммирующий счетчик 8. Р1овым в устройстве является введение комбинационного сумматора, шифратора и управляемого счетчика, что позволило создать более равномерные импульсные потоки во внутренних цепях устройства и привело к значительному повышению точности без сужения диапазона изменения значений делителя, при которых выполняется операция деления, 1 ил., 1 табл.

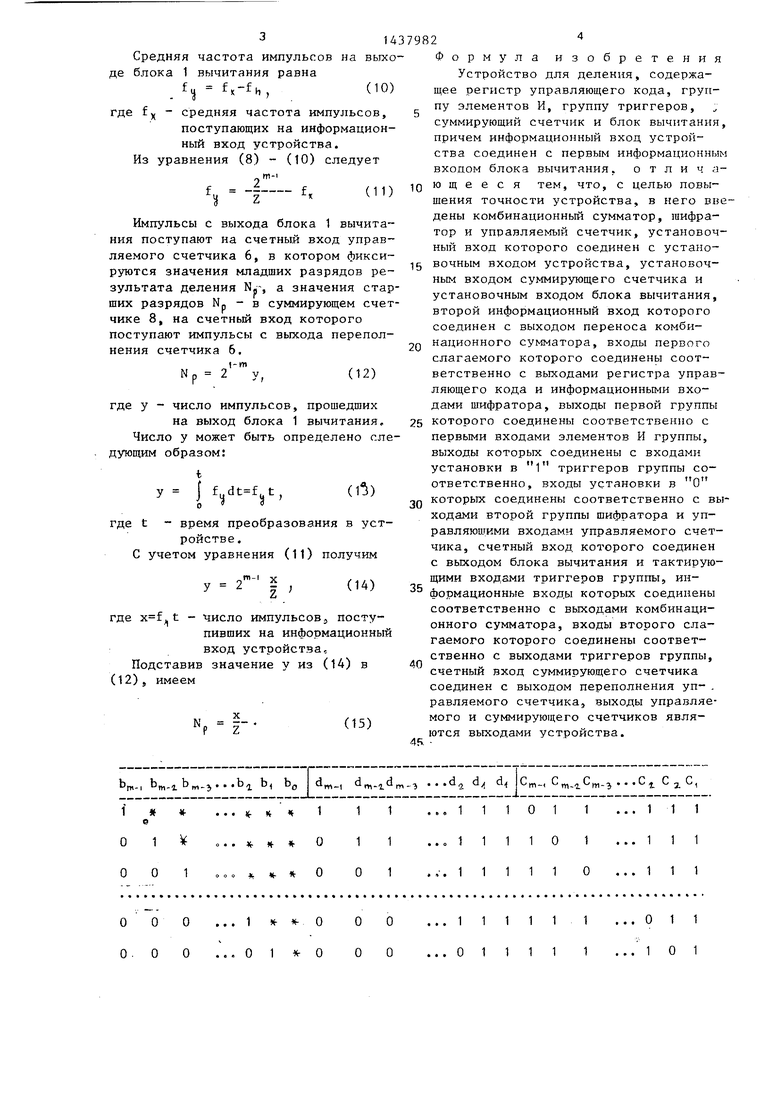

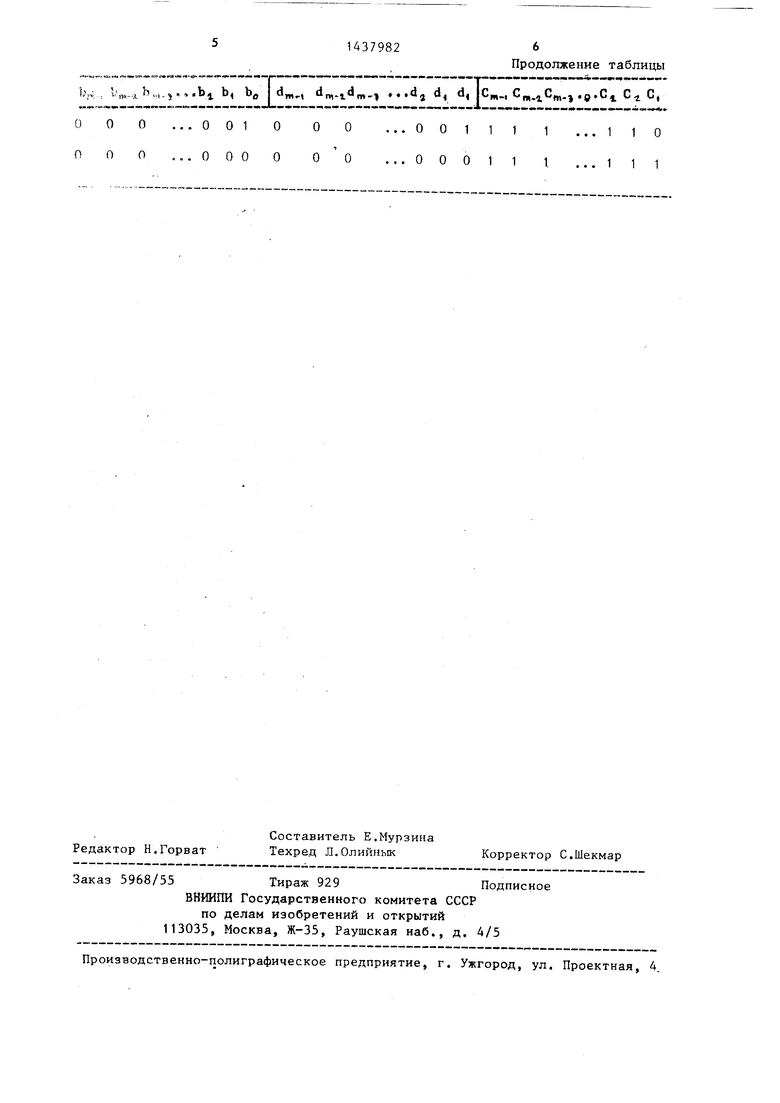

ветствие между его входными и выходными сигналами приведено в табл. 1,

де d, d, ,.,.d,, .G, ,

значения сигналов первой группы выходов шифратора 7 , значения сигналов второй группы выходов J

безразличное значе кие двоичного.раз-, ряда числа Z,

Работа устройства при Ь, т„е, как следует из уравнения диапазоне

2 Z 6 2

m

(2)

При этом di 1 (J О, 1,

при этом U1

т-1), С„., О, т-2). Сигнал С

Сг 1 (1 о, 1....

i., 0 подается на вход установки в ноль триггера 5,/ и удерживает его в нулевом состоянии в течение всего времени работы устройтриггеров 5i-5m и регистр 2 управ- ляюЕтего код а функционируют как (т-1)-разрядный накап-пивающий сумматор.

Средняя частота появленргя единицы на выходе (т-1)-разрядного накапливающего сумматора, т,е, на выходе переноса комбинационного сумматора 3, определяется выражением

f

h

.

п

S

(8)

где f

0

5

средняя .частота импульсов, ° поступающих с выхода блока 1 вычитания на тактирующие входы триггеров 5,5„, а А,П1, - число, содержащееся в (т-1) младших разрядах регистра 2.

В соответствии с уравнением (5) m-l.

lib;2 Z-2

m-t

(9)

3143

Средняя частота импульсов на выходе блока 1 вычитания равна ..-fh,

где fy средняя частота импульсов, поступающих на информационный вход устройства. Из уравнения (8) - (10) следует л. m-i

f..

f.

Импульсы с выхода блока 1 вычитания поступают на счетный вход управляемого счетчика 6, в котором фиксируются значения младших разрядов результата деления N.-, а значения старших разрядов NP - в суммирующем счетчике 8, на счетный вход которого поступают импульсы с выхода переполнения счетчика 6.

1-т у,

(12)

где у - число импульсов, прошедших на выход блока 1 вычитания, Число у может быть определено следующим образом:

I t,

Г 1

(1)

где t - время преобразования в устройстве , С учетом уравнения (11) получим

X

У 2 - ;

(14)

где - число импульсов J поступивших на информационный вход устройства. Подставив значение у из (1А) в

(12), имеем

000 ... О О ...111111 ...011 0.0 О ... О О ...01111 1 ...101

3

7982

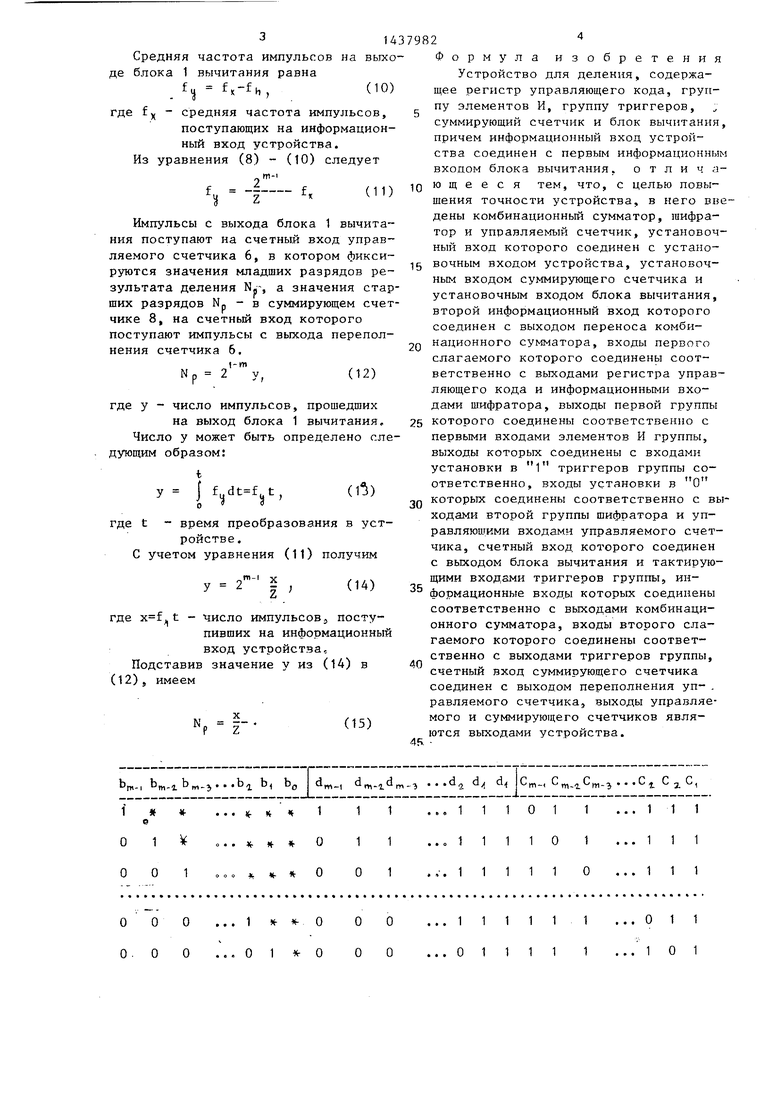

Формула изобретения

Устройство для деления, содержащее регистр управляющего кода, группу элементов И, группу триггеров, суммирующий счетчик и блок вычитания, причем информационный вход устройства соединен с первым информационным входом блока вычитания, о т л и ч ю щ е е с я тем, что, с целью повышения точности устройства, в него введены комбинационный сумматор, шифратор и управляемый счетчик, установочный вход которого соединен с устано15 вочным входом устройства, установочным входом суммирующего счетчика и установочным входом блока вычитания, второй информационный вход которого соединен с выходом переноса комби2Q национного сумматора, входы первого слагаемого которого соединены соответственно с выходами регистра управляющего кода и информационными входами шифратора, выходы первой группы

25 которого соединены соответственно с первыми входами элементов И группы, выходы которых соединены с входами установки в 1 триггеров группы соответственно, входы установки в О

.JQ которьге соединены соответственно с выходами второй группы шифратора и управляющими входами управляемого счетчика, счетный вход, которого соединен с выходом блока вычитания и тактирующими входами триггеров группы, ин- формационные входы которых соединены соответственно с выходами комбинационного сумматора, входы второго слагаемого которого соединены соответственно с выходами триггеров группы, счетный вход суммирующего счетчика соединен с выходом переполнения уп- . равляемого счетчика, выходы управляе1ч, 1„,-лЬ.,,,,.Ьд Ь bo d,, d.d,, ,..d, d, d, C,., C.C., .(.C C G,

„.,.„...-- ---- - - -- ------ - - - - - - - -- - - - - - - -

0 0 0 ...001 0 0 0 ...00111 1 ...110 n 0 0 ...000 0 o o ...00011 1. ...111

| Мельников А,А | |||

| и др | |||

| Обработка частотных и временных импульсных сигналов | |||

| И.: Энергия, 1976, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Авторское сщ детельство СССР № , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-15—Публикация

1987-04-20—Подача