() УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для вычисления тригонометрических функций | 1980 |

|

SU928348A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

1

Изобретение относится к вычислительной технике, а именно к классу арифметических устройств для вычисления трансцендентных функций, и может .быть использовано в цифровых моделирующих, управляющих и вычислительных системах как общего, так и специального применения.

Известны микропроцессорные устройства для вычисления элементарных функций, состоящие из приемных, буферных и выходных регистров, коммутаторов, сдвигателей кодов, сумматоров и др., в которых вычисление каждой функции осуществляется с помощью соответствую-,j щей микропрограммы tl.

Недостатки указанных устройств сложность оборудования и микропрограммного управления, а также невысокое быстродействие.го

Известны цифровые устройства для вычисления ряда элементарных функций, содержащие регистры, блоки сдвига, блоки памяти, сумматоры-вычитатели.

анализаторы сходимости и др., в которых процесс вычисления заключается в выполнении процедур псевдоумножения и псевдоделения с целью реализации алгоритмов Волдера-Меджитта С2}.

Недостатки указанных устройств ограниченные функциональные возможности и невысокое быстродействие, обусловленные наличием деформации вектора.

Известны также цифровые устройства для вычисления элементарных функций, тоже реализующие алгоритмы Волдера-Меджитта и в которых для сни-. жения деформации вектора выбирается формула численного интегрирования высокого порядка З.

Недостатками таких устройств является также недостаточно высокое быстродействие и малая точность.

Наиболее близким к предлагаемому по функциональному назначению, принципу действия и технической сущности является устройство для вычисления

элементарных функций, содержащее три регистра, четыре блока сдвига, блок памяти, семь сумматоров, четыре переключателя, блок управления, счетчик и блок анализа знака. Коррекция деформации вектора в этом устройстве осуществляется путем вычисления на каждом шаге частичных поправок .

Недостатки известного устройства невысокое быстродействие и узость области применения за счет ограниченного диапазона изменения аргумента и невозможности непрерывного генерирования функций с управляемым шагом, которые обусловлены зависимостью коэффициента деформации вектора от набора итераций, в результате чего этот набор задается фиксированным, поэтому вариации его, в зависимости от аргумента или режима функционирования , недопустимы.

Цель изобретения - повышение быстродействия устройства и расширение области его применения за счет увеличения диапазона изменения аргумента и возможности непрерывного генерирования функций с управляемым шагом.

Поставленная цель достигается тем что в устройство, содержащее первый, второй и третий регистры, два блока сдвига, счетчик, блок памяти, блок управления и сумматоры, в котором выкоды первого и второго регистров соечинены с первыми информационными входами первого и второго сумматоров соответственно, выходы первого и второго регистров соединены с информационными входами соответствующих блоков сдвига, выходы которых соединены с вторыми информационными входами второго и первого сумматоров соответственно, выходы третьего, четвертого и пятого сумматоров соединены с первыми информационными входами третьего, первого и второго регистров соответственно, вторые информационные входы которых соединены с входной информационной шиной устройства, запускающий вход и ответный выход устройства соединены соответственно с первым входом и первым выходом блока управления, второй выход которого соединен с управляющими входами приема информации первого, второго и третьего регистров, тактирующие входы первого и второго регистров и первый тактирующий вход третьего регистра соединены с третьим выходом блока управления, четвертый выход которого

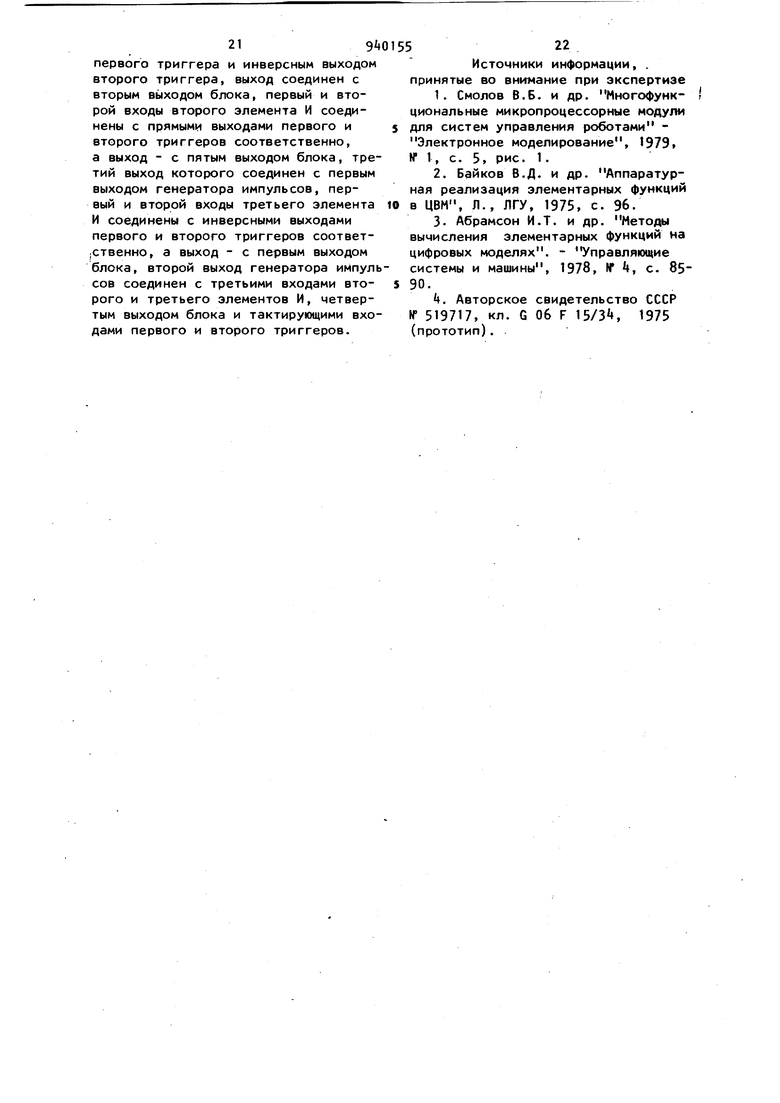

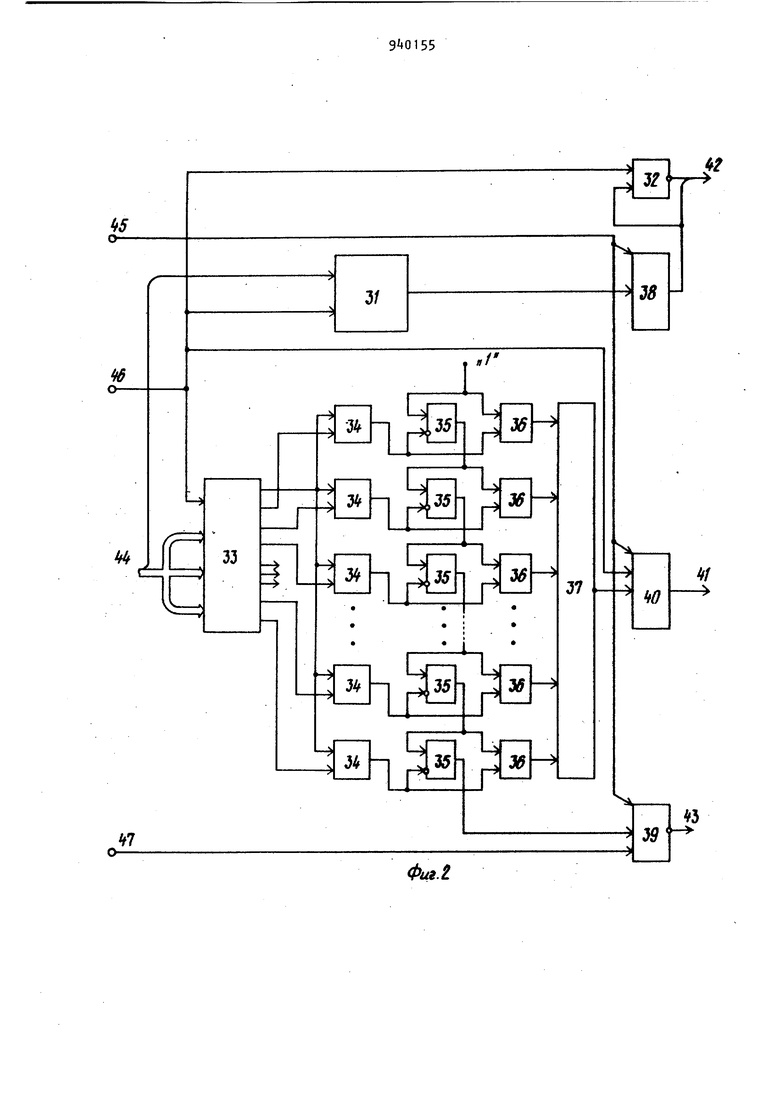

соединен со счетным входом счетчика, выход которого соединен с вторым входом блока управления, первый и второй информационные входы третьего сумматора соединены с выходом третьего регистра и первым выходом блока памяти соответственно, адресная шина устройства соединена с адресными входами блоков сдвига и памяти, знаковая шина устройства соединена с управляющими входами первого, второго, третьего, четвертого и пятого сумматоров, дополнительно введены четвертый и пятый регистры и блок анализа состояния, содержащий регистр кода операций, дешифратор и блок нормализации числа, первый и второй входы которого соединены соответственно с информационным и управляющим входами блока анализа состояния, адресный, знаковый, управляющий и блокирующий выходы которого соединены с первым, вторым и третьим выходами блока нормализации числа и выходом дешифратора соответственно, вход дешифратора соединен с третьим входом блока нормализации числа и выходом регистра кода операций, вход которого соединен с входом кода операции блока анализа состояния, вход обнуления которого соединен с четвертым входом б/юка нормализации числа, причем управляющие входы приема информации четвертого и пятого регистров и счетчика соединены, с пятым выходом блока управления третий Вход которого соединен с управляющим выходом блока анализа состояния, адресный и знаковый выходы которого соединены с адресной шиной и знаковой шиной устройства соответственно, входная управляющая шина и запускающий вход устройства соединены соответственно с входом кода операции и входом обнуления блока анализа состояния, блокирующий выход которого соединен с блокирующим входом блока памяти, второй выход которого соединен с установочным входом счетчика, выход которого соединен с управляющим входом блока анализа состояния информационный вход которого соединен с выходами третьего, четвертого и пятого сумматоров, выходы первого и второго сумматоров соединены с информационными входами четвертого и пятого регистров соответственно, выходы которых соединены с первыми информационными входами четвертого и пятого сумматоров соответственно. 5 вторые информационные входы которых соединены с выходами второго и первого блоков сдвига соответственно, пятый выход блока управления соединен с вторым тактирующим входом третьего регистра. В устройстве для вычисления элементарных функций блок нормализации числа содержит одноразрядный блок памяти, элемент РАВНОЗНАЧНОСТЬ, муль типлексор, элементы ИСКЛОЧАЮЩЕЕ ИЛИ, элементы ЗАПРЕТ, элементы И, шифратор, первый и второй триггеры и регистр, выход которого является первым выходом блока, второй выход кото рого соединен с выходами элемента РАВНОЗНАЧНОСТЬ и первого триггера, управляющий вход которого соединен с управляющими входами регистра и второго триггера и с вторым входом блока, первый вход которого соединен с информационными входами мультиплек сора и первой группой адресных входов одноразрядного блока памяти, вто рая группа адресных входов которого соединена с первым входом элемента РАВНОЗНАЧНОСТЬ, первым информационным входом регистра, адресным входом мультиплексора и третьим входом блока, знаковый выход мультиплексора соединен с первыми входами всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вто.рые входы которых соединены с разрядными выходами мультиплексора, выход каждого элемента ИСКЛОЧАЮЩЕЕ ИЛИ соединен с управляющим входом соответствующего элемента ЗАПРЕТ и первым входом соответствующего элемента И, второй вход каждого элемента И соединен с информационным входом соо ветствующего элемента ЗАПРЕТ и выходом предыдущего элемента ЗАПРЕТ, выходы элементов И соединены с входами шифратора, выход которого соединен с вторым информационным входом регистра, выход одноразрядного блока памя ти соединен с информационным входом первого триггера, выход последнего элемента ЗАПРЕТ соединен с информационным входом второго триггера, выход которого является третьим выходом блока, четвертый вход которого соединен с обнуляющим входом второго триггера, выход первого триггера сое динен с вторым входом элемента РАВНОЗНАЧНОСТЬ . В устройстве для вычисления элементарных функций блок управления со держит генератор импульсов, три эле56мента И, два триггера и мультиплексор, причем третий вход блока соединен с входом сброса мультиплексора, первый и второй управляющие входы которого соединены с прямыми выходами первого и второго триггеров соответственно, первый и второй информационные входы мультиплексора соединены с шиной сигнала 1, третий и четвертый информационные входы мультиплексора соединены с вторым входом блока, пятый информационный вход мулЬ типлексора соединен с шиной сигнала Q, шестой информационный вход мультиплексора соединен с первым входом блока, единичным входом первого триггера, нулевым входом второго триггера и входом запуска генератора импульсов, седьмой и восьмой информационные входы мультиплексора соединены с шиной сигнала 1, первый и второй выходы мультиплексора соединены с информационными входами первого и второго триггеров соответственно, входы первого элемента И соединены с прямым выходом первого триггера и инверсным выходом второго триггера, выход соединен с вторым выходом блока, первый и второй входы второго элемента И соединены с прямыми выходами первого и второго триггеров соответственно, а выход - с пятым выходом блока, третий выход которого соединен с первым выходом генератора импульсов, первый и второй входы третьего элемента И соединены с инверсными выходами первого и второго триггеров соответственно, а выход - с первым выходом блока, второй выход геИератора импульсов соединен с третьими входами второго и третьего элементов И, четвертым выходом блока и тактирующими входами первого и второго триггеров. На фиг. 1 представлена блок-схема |устройства; на фиг. 2 - схема блока нормализации числа; на фиг. 3 схема блока управления. Устройство содержит первый 1, второй 2, третий 3t четвертый k и пятый 5 регистры, первый 6 и второй 7 блоки сдвига, блок 8 памяти, первый 9 второй 10, третий 11, четвертый 12 и пятый 13 сумматоры, блок И управления, счетчик 15 и блок 16 анализа состояния, состоящий из регистра 17 кода операций, дешифратора 18 и блока 19 нормализации числа. Первый, второй и третий выходы блока 19 нормализации 7 . числа соединены соответственно с адресным, знаковым и управляющим выхо дами блока 16 анализа состояния, бло кирующий выход которого соединен с в ходом дешифратора 18, вход которого и третий вход блока 19 нормализации числа соединены с выходом регистра 1 кода операций. Вход этого регистра 1 соединен с входом кода операции блока 16 анализа состояния, информацион ный, управляющий входы и вход обнуле ния которого соединены соответственн с первым, вторым и четвертым входами блока 19 нормализации числа. Выходы третьего11, четвертого 12 и пятого 13 сумматоров по шине 20 соединены с информационным входом блока 16 ана лиза состояния, знаковый выход которого по знаковой шине 21 соединен с управляющими входами всех сумматоров 9-13- Адресный выход блока 16 анализа состояния по адресной шине 22 устройства соединен с адресными вход ми блоков 6 и 7 сдвига и блока 8 памяти, первый выход которого соединен с вторым информационным входом треть его сумматора 11. Блокирующий выход блока Тб анализа состояния соединен с блокирующим входом блока 8 памяти, второй выход которого соединен с установочным входом счетчика 15. Третий вход блока I управления соединен с управляющим выходом блока 16 анализа состояния, вход кода операции которого соединен с входной управляющей шиной 23 устройства. Вход обнуления блока 16 анализа состояния соединен с запускающим входом 2 устройства и первым входом блока 1 управления, первый выход которого соединен с ответным выходом 25 устро ства. Второй выход блока 14 управления соединен по шине 26 с управляющими входами занесения информации первого 1, второго 2 и третьего 3 регистров, выходы которых соединены с первыми информационными входами первого 9, второго 10 и третьего. 11 сумматоров соответственно. Выходы первого 9 и второго 10 сумматоров сое динены с информационными входами четвертого 4 и пятого 5 регистров соответственно, выходы которых соединены с первыми информационными входами четвертого 12 и пятого 13 сумматоров соответственно. Выходы третьего 11, четвертого 12 и пятого 13 сумматоров соединены с первыми информационными входами третьего 3, первого 1 и второго 2 регистров соответственно, вторые информационные входы которых соединены с входной информационной шиной 27 устройства. Четвертый выход блока 14 управления соединен со счетным входом счетчика 15 а пятый выход блока 14 управления соединен по шине 28 с вторым тактирующим входом третьего регистра 3 и с управляющими входами приема информации четвертого 4 и пятого 5 регистров и счетчика 15Третий выход блока 14 управления соединен по шине 29 с тактирующими входами первого 1 и второго 2 регистров и с первым тактирующим входом третьего регистра 3. Выход 30 счетчика 15 соединен с управляющим входом блока 16 анализа состояния и вторым входом блока 14 управления. Выходы первого 1 и второго 2 регистров соединены с информационными входами первого 6 и второго 7 блоков сдвига соответственно. Выход первого блока 6 сдвига соединен с вторыми информационными входами второго 10 и пятого 13 сумматоров. Выход второго блока 7 сдвига соединен с вторыми информационными входами первого 9 и четвертого 12 сумматоров. Блок-схема (фиг. 2) одного из возможных вариантов выполнения блока 19 нормализации числа содержит одноразрядный блок 31 памяти, элемент РАВНОЗНАЧНОСТЬ 32, мультиплексор 33, элементы ИСКЛЮЧАЩЕЕ ИЛИ 34, элементы ЗАПРЕТ 35, элементы И Зб, шифратор 37, первый 38 и второй 39 триггеры и регистр 40. Порядковые номера элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 34, элементов ЗАПРЕТ 35 и элементов И Зб приведены в скобках и соответствуют номеру разряда мультиплексора 33, начиная с младшего. Например, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенный к второму младшему разряду мультиплексора 33, имеет номер 34(2), а соединенные с ним элемент ЗАПРЕТ и элемент И 35(2) и 36(2) соответственно. Для п-разрядного мультиплексора элементы старшего разряда имеют номера соответственно 34(), 35(п-1) и Зб.(п-1), так как п-й разряд является знаковым. Выход регистра 40 является первым выходом 41 блока 19 нормализации числа, второй выход 42 которого по шине соединен с выходами элемента РАВНОЗНАЧНОСТЬ 32 и первого триггера 38. Выход второго триггера 39 является третьим выходом 43 блока 19 нормали9зации числа, первый вход k которого соединен с информационными входами мультиплексора 33 и первой группой адресных входов одноразрядного блока 31 памяти. Управляющие входы регистра АО, первого 38 и второго 39 триггера соединены с вторым входом S блока, третий вход 6 которого соединен с второй группой адресных входов одноразрядного блока 31 памяти, с первым входом элемента РАВНОЗНАЧНОСТЬ 32, с первым информационным входом регистра kQ и адресным входом мультиплексора 33. знаковый выход которого соединен с первыми входами всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3(1) 3«(п-1), вторые входы которых соединены с разрядными выходами мультиплексора 33. Выход каждого элемента ИСКШЧАЮЩЕЕ ИЛИ 3f{j), где j меняется от 1 до п-1, соединен с управляющим входом элемента ЗАПРЕТ 35(j) и первым входом элемента И 36(j) данного j-ro разряда. Второй вход каждого элемента И 36(j) соединен с информационным входом элемента ЗАПРЕТ 35(j) данного j-ro разряда и выходом элемента ЗАПРЕТ 35(j+1) предыдущего старшего разряда. Выходы всех элементов И Зб(1)-Зб(п-1) соединены с соответствующими входами шифратора 37 выход которого соединен с вторым информационным входом регистра 0. Выход одноразрядного блока 31 памяти соединен с информационным входом пер вого триггера 38, выход элемента ЗАПРЕТ 35(1) младшего разряда соединен с информационным входом второго триггера 39, обнуляпщий вход которого соединен с четвертым входом 7 блока нормализации Ч1.сла, причем выход первого триггера 38 соединен с вторым входом элемента РАВНОЗНАЧНОСТЬ 32. Блок-схема (фиг. 3) одного из воз можных вариантов выполнения блока Ш управления содержит генератор 8 импульсов, первый Э, второй 50 и третий 51 элементы ;И, первый 52 и второй 53 треггеры, мультиплексор 5 первый 55, второй 56 и третий 57 вхо ды, а также первый 58, второй 59. третий 60. четвертый 61 и пятый б2 выходы. Первый и второй управляющие входы мультиплексора З соединены с прямыми выходами первого 52 и второг 53 триггеров соответственно, информационные входы которых соединены с первым и вторым выходами мультиплекс 510 ра 5 соответственно. Первый вход 55 блока соединен с единичным входом первого триггера 52. нулевым входом второго триггера 53. входом запуска генератора 8 импульсов и с шестым информационным входом мультиплексора 5, первый, второй, седьмой и восьмой информационные входы которого соединены с шиной сигнала 1. Третий и четвертый информационные входы мультиплексора 5 соединены с вторым входом 5.6 блока, а пятый информационный вход мультиплексора 5 соединен с шиной сигнала О. Третий вход 57 блока соединен с входом сбрюса мультиплексора 5. Входы первого элемента И i9 соединены с прямым выходом первого триггера 52 и инверсным выходом второго триггера 53. а выход соединен с вторым выходом 59 блока. Первый и второй входы второго элемента И 50 соединены с прямыми выходами первого 52 и второго 53 триггера соответственно, а выход - с пятым выходом 62 блока, третий выход 60 которого соединен с первым выходом генератора ЦВ импульсов. Первый и второй входы третьего элемента И 51 соединены с инверсными выходами первого 52 и второго 53 триггеров соответственно, а выход - с первым выходом 58 блока. Второй выход генератора импульсов соединен с третьими входами второго 50 и третьего 51 элементов И, четвертым выходом 61 блока и тактирующими входами первого 52 и второго 53 триггеров. Последовательность работы предлагаемого устройства состоит в задании в виде кодов данных по входной информационной шине 27 устройства, кода операций и запускающего сигнала соответственно по входной управляющей шине 23 и запускающему входу 2t устройства и съеме данных в виде кодов с третьего t1. четвертого 12 и пятого 13 сумматоров, или с первого t, второгЬ 2 и третьего 3 регистров после формирования импульсного сигнала по управляющему выходу блока 16 анализа состояния или по ответному выходу 25 устройства. Работа устройства основывается на следующих рекуррентных соотношениях , q.,..y,. . - - r. -(iM) + P. Ti 1 . +a-.-:f -Z 4f1 « Tl ,-41 ,-, :j(. 6..x- -1- J,. i4-f V -v(l) iH i+1 . -:. i j - номер коррекции j 1,2,3. .m, ; C- - константы истинного значения аргумента, 2arctg при , . i | 2Arth 2 - при j - индекс итерации, принимающий целочисленные значения в диапазоне 0 п, где n - разрядность двоичного представлений данных. Реа/мзация соотношений (1)-()эквивалентна соотношениям te:v::,i,i;:K2 c % с погрешностью до ошибок округления при вычислениях с двоичной разрядностью п. А так как реализация соотношений (8) не приводит к появлению деформации вектора решения на /ж}бой итерации с индексом i, то наборы ите раций могут быть произвольными и задаваться как принудительно, например, в виде одной итерации при генерировании функций с шагом С(7), так и автоматически, т.е. когда индексы 1заранее не определены и формируютс в процессе вычислений. Для определения индекса i, а также для определения значения f, , равного -f 1 или -1, и момента окончания итераций в устройстве служит блок 16 анализа состояния. Код операций (КОП поступающий по входной управляющей шине 23, записывается в регистре 17 кода операций. Первый разряд КОП соответствует величине q, равной +1 или -1, и характеризует тип определяющей функции - тригонометрическая или гиперболическая (экспоненциальная). Дешифратор 18 служит для выде ления режима непрерывного генерирова ния функций. КОП поступает также на a 12 третий вход блока 19 нормализации числа, в котором используется для задания адреса в мультиплексоре 33 (фиг. 2), задания части адреса одноразрядного блока 31 памяти, а также для формирования сигналов пс знаковому выходу блока 16 анализа состояния и для формирования старшего разряда адреса блока 8 памяти. КОП, поступая на мультиплексор 33, управляет выбором выходов с любого сумматора - третьего 11, четвертого 12 или пятого 13 - с целью анализа их выходных кодов. КОП, поступая в одноразрядный блок 31 памяти, совместно с знаками операндов, поступающими по первому входу блока 19 нормализации числа, формирует стратегию выбора знака |. для заданной функции, т.е. обеспечивает сходимость процессов вычислений во всех квадрантах пространства допустимой области определения функций. Все соотношения для выбора знаков во всех квадрантах для каждой функции записываются заранее в одноразрядном блоке 31 памяти, представляющем собой модуль постоянного запоминающего устройства. Первый разряд КОП, поступая на первый вход элемента РАВНОЗНАЧНОСТЬ 32, формирует противофазные или синфазные значения сигналов с выходов первого триггера 38 и элемента РАВНОЗНАЧНОСТЬ 32. Поскольку эти выходы используются для управления операциями сложения или вычитания по второму входу сумматоров, то при их синфазном значении возможны вычисления прямых и обратных гиперболических и экспоненциальных функций. Для противофазных значений выходов элемента РАВНОЗНАЧНОСТЬ 32 и первого триггера 38, что обусловливается значением первого разряда КОП, равным О, операции в первом 9 и четвертом 12 сумматорах будут инверсными по отношению к операцияк во втором 10, третьем 11 и пятом 13 сумматорах, так как выход элемента РАВНОЗНАЧНОСТЬ 32 поступает через знаковую шину 21 на управляющие входы сумматора первой перечисленной группы, а выход первого триггера 38 - соответственно второй. Кроме того, первый разряд КОП через регистр 0 поступает на вход старшего адреса блока 8 памяти, в котором записаны константы (7) , определяя тем самым тип константы. На остальные адресные входы блока 8 памяти и блоков 6 и 7 сдвига поступают сигналы с остальных разрядов регистра 40, на которых содержится величина порядка числа, поступающего с мультиплексора 33.

Для формирования порядка код числа с ПРОИЗВОЛЬНЫМ знаком посредством элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 34 преобразуется в код одного знака. После этого с помощью элементов ЗАПРЕТ 35 и элементов И 36 на каждом k-м разряде входа шифратора 37 формируется функция

« „ а П е,

где значение на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 34 k-ro разряда. приведенного на фиг. 2 варианта соединения элементов схемы на входе шифратора 37 возможно появление только одного разрядного сигнала, соответствующего уровню логической 1, который шифратором 37 преобразуется 8 соответствующий данному разряду номер, либо на входе шифратора 37 не образуется ни одной логической 1, когда анализируемое число эквивалентно арифметическому нулю. 8 последнем случае логическая функция

пн

Ра

снимаемая с выхода элемента ЗАПРЕТ младшего разряда 35(0, принимает значение логической 1, что соответствует окончанию вычислительного процесса. Этот сигнал через второй триггер 39 поступает по управляющему выходу блока 16 анализа состояния на третий вход блока 14 управления. Занесение состояний знакового, адресного и управляющего выходов блока 16 анализа состояния осуществляется при поступлении сигнала PQ с выхода счетчика 15, формируемого в момент переполнения этого счетчика при номере коррекции j, равном т-. Величина, равная дополнению т. до М, где М - емкость счетчика 15, записывается а бпок 8 памяти в виде констант и считывается из него в счетчик 15 по сигналу Сз, поступающему с пятого выхода 28 (фиг. 1) блока 14 управления на управляющий вход счетчика 15Импульсы tf, поступающие с четвертого выхода блока 14 управления, по переднему фронту увеличивают состояние счетчика 15 каждый раз на единицу.

Граф работы блока 14 управления содержит вершину начального состояния CQ. , вершину подготовительного этапа С, вершину корректирующего цикла и вершину формирования ответного сигнала CQOПереход из начального состояния CQ возможен на вершину подготовительного этапа Сх) по запускающему

внешнему сигналу Р, поступающему по первому входу блока 14 управления с запускающего входа 24 устройства, а также на вершину формирования ответного сигнала Сд, переход на ко(Торую возможен при поступлении сиг- |нала PJ, формируемого по сигналу (9) с второго триггера 39 блока 19 норма/мзации числа.

С поступлением сигнала Р на первом и втором выходах генератора 48 импульсов блока 14 управления (фиг.З) формирз тся серии импульсов t и соответственно, обусловливая функционирование устройства.

При нахождении блока 14 управления в начальном состоянии С на выходе первого элемента И 49 формируется строб предварительного занесения С, поступающий через второй выход 26

блока 14 управления на управляющие входы приема информации первого 1, второго 2 и третьего 3 регистров, который совместно с серией импульсов tff, поступающей по третьему выходу блока 14 управления, по переднему фронту разрешает запись в эти регист ры исходной информации о данных Z, Zft, Т, поступающих по входной информационной шине 27 устройства.

Переход блока 14 управления из одного состояния в иное осуществляется по переднему (j JOHTy серии импульсов f, поступающей на тактирующие входы первого 52 и второго 53 триггеров. Функция переходов формируется мультиплексором 54, представляющим собой сдвоенный селектор-мультиплексор- четырех входов на один выход. При нахождении блока 14 управления в состоянии подготовительного этапа С на его пятом выходе формируется строб Сэ. передний фронт которого используется для предварительной установки в счетчик 15 кода,находящегося в блоке 8 памяти. Строб С э поступает также на управляющие входы приема информации четвертого 4 и пятого 5 регистров выполненных на одноступенчатых триггерах типа О, разрешая прохождение информации с информа ционных входов этих регистров на их выходы в течение всей длительности этого строба и запоминание установившейся информации в момент заднего фронта Cj. Кроме того, информация с выхода третьего сумматора 11 по заднему фронту Сд записывается в тре тий регистр 3 а по переднему фронту серии ifj, поступающей по выходу 29, информация с четвертого 12 и пятого 13 сумматоров записывается соответственно в первый 1 и второй 2 регист ры (в регистрах 1-3 используются двухступенчатые триггеры). В результате во время подготовительного этапа вычисляются соотношения (1) и (2), причем Х и у- за поминаются в четвертом 4 и пятом 5 регистрах соответственно, а х Д: и - в первом 1 и втором 2 регис рах соответственно. В третьем регист ре 3 оказывается значение d, вычисленное на предварительном этапе. При определенных значениях аргумента во время выполнения подготовительного этапа С может появиться сигнал переполнения Рг счетчика 15, по которому, если отсутствует сигнал PI с управляющего выхода блока 16 анализа состояния, подготовительный этап повторится, но для иного значения итерации i и соответствующей ей величины шага, а также . Если сигнал Prj со счетчика 15 отсутствует, а также отсутствует сигнал Pj,, то блок 4 управления переходит в состояние корректирующего цикла . Это состояние отличается от предыдущего только отсутствием строба С, благодаря чему в регистрах информация не изменяется, а в счетчике 15 не происходит параллельное занесение информации из блока 8 памяти, а идет лишь подсчет количества циклов j для данной итерации i. В этом случае реализуются соотношения (З), а в конце итерации, при j m.,, также и соотношение (k}, Кроме того, при формировании сигнала Рл с выхода счетчика 15 в блоке 19 нормализации числа запоминается значение f и величина i, равная величине модуля порядка анализируемого числа. В случае отсутствия сигнала Р осуществляется переход на подготовительный этап С., в противном случае блок И управления переходит в состояние формирования ответного S 16 сигнала С В этом случае третьим элементом И 51 формируется сигнал S, который по ответному выходу 25 устройства выдается задатчику (внешнему устройству, процессору, не изображенному на фиг. 1). Принимая этот сигнал, задатчик считывает информацию с регистров или сумматоров, а также снимает запускающий сигнал P-t, который устанавливает генератор k8 импульсов и второй триггер 39 блока 19 нормализации числа в исходное нулевое состояние, и по заднему фронту последнего импульса i блок k управления переходит в исходное начальное состояние С,.. 01 Для непрерывного генерирования функций дешифратор 18, анализируя КОП на регистре 17 кода операций, выдает сигнал, блокирующий первый выход блока 8 памяти, благодаря чему на втором информационном входе третьего сумматора 11 оказывается всегда С О, поэтому код в третьем регистре 3 не меняется и будут выполняться вычисления с постоянным шагом итераций, соответствующим константе С . Устройство в зависимости от кода операций позволяет одновременно форировать следующие основные наборы функций: операции сложения-вычитания X Z t S i дпТ - Z у 2, sign - Z, операцию сдвига X Z, у sign Z - , i{T) L - , операции нормализации числа i I- ; X у Z функциональное преобразование 0)Xs2-OOST; ., 5)x z-ctiT-, .stiT, 6) xsl -CosT-Z,-sinT:} a Z -3fnT Z -co3T -, t) XsZ.jCflT+Z -SllT-, J Z SbT+Z -c T, dlx... e) Xrl.Yci-()Os(Tt| ;:izlZ1f Sfn(Tt|, } (), (), j)(f.arctsEZ /z ; Vl 4z, И) 7 -circt г,1г -, X rVzJtZ, k) l/r-/ rtti2 /Z -, , A)V -ArthZ,/z,-, XrVl -zJ, идр.; функциональное генерирование ct) .COSCj.K., -JsZ-sincT-R-, «) X 2-cticLK; : 2-5ЪсТ-й 1ft) X c.K-Z,.9in cTiC; cTl 42 -COSCj -| ; i)x 2 -cbcy-k+z,.sbcy-ic-, : SI, cj- fc 4 c-h cT. |(; e)., (e .k), / tcT.fc т -1(9 cirCT.t и др. где 2, 2,2, Т - исходные данные, вво димые в начальном состоянии в первый 1, второй 2 и третий 3 регистры соот ветственно. Предлагаемое устройство, предназначенное для ускоренного вычисления указанных наборов функций, является многофункциональным, реализующим мак рокоманды языка высокого уровня, име ет широкую область применения в качестве как центральных, так и функци нальных процессоров для различных Э общего и специального применения, в том числе для решения задач спектраль ного анализа сигналов с помощью БПФ для преобразования прямоугольных коо динат в сферические и наоборот, для вращения координат и векторов, для синтеза криволинейных поверхностей в станках с программным управлением и т.п. Формула изобретения 1. Устройство для вычисления эле ментарных функций, содержащее первый второй и третий регистры, два блока сдвига, счетчик, блок памяти, блок управления и сумматоры, причем выходы первого и второго регистров соеди нены с первыми информационными входа 518 ми первого и второго сумматоров соответственно, выходы первого и второго регистров соединены с информационными входами соответствующих блоков сдвига, выходы которых соединены с вторыми информационными входами второго и первого сумматоров соответственно, выходы третьего, четвертого и пятого сумматоров соединены с первыми информационными входами третьего, первого и второго регистров соответственно, вторые информационные входы которых соединены с входной информационной шиной устройства, запускающий вход и ответный выход устройства соединены соответственно с первым входом и первым выходом блока управления, второй выход которого соединен с управляющими входами приема информации первого, второго и третьего регистров, тактирующие входы первого и второго регистров и первый тактирующий вход третьего регистра соединены с третьим выходом блока управления, четвертый выход которого соединен со счетным входом счетчика, выход которого соединен с вторым входом блока управления, первый и второй информационные входы третьего сумматора соединены с выходом третьего регистра и первым выходом блока памяти соответственно, адресная шина устройства соединена с адресными входами блоков сдвига и памяти, знаковая шина устройства соединена с управляющими входами первого, второго, . третьего, четвертого и пятого сумматоров, отличающееся тем, что, с целью повышения быстродействия устройства и расширения области его применения за счет увеличения диапазона изменения аргумента и возможности непрерывного генерирования функций с управляемым шагом, устройство дополнительно содержит четвер-г тый и пятый регистры и блок анализа состояния, содержащий регистр кода операций, дешифратор и блок нормализации числа, первый и второй входы которого соединены соответственно с Информационным и управляющим входами блока анализа состояния, адресный, знаковый, управляющий и блокирующий выходы которого соединены с первым, вторым и третьим выходами блока нормализации числа и выходом дешифратора соответственно, вход дешифратора соединен с третьим входом блока нормализации, числа и выходом .регистра 19 кода операций, вход которого соединен с входом кода операции блока ана лиза состояния, вход обнуления которого -соединен с четвертым входом бло ка нормализации числа, причем управляюцие входы приема информации четвертого и пятого регистров и счетчика соединены с пятым выходом блока управления, третий вход которого соединен с управляющим выходом блока анализа состояния, адресный и знаковый выходы которого соединены с адресной шиной и знаковой шиной устрой ства соответственно, входная управляющая шина и запускающий вход устрайства соединены соответственно с входом кода операции и входом обнуле ния блока анализа состояния, блокирующий выход которого соединен с бло кирующим входом блока памяти, второй выход которого соединен с установочным входом счетчика, выход которого соединен с управляющим входом блока анализа состояния, информационный вход которого соединен с выходами третьего, четвертого и пятого сумматоров, выходы первого и второго сумматоров соединены с информационными входами четвертого и пятого регистров соответственно, выходы которых соединены с первыми информационными входами четвертого и пятого сумматоров соответственно, вторые информационные входы которых соединены с вы ходами второго и первого блоков сдви га соответственно, пятый выход блока управления соединен с вторым тактирующим входом третьего регистра. 2. Устройство по п. 1, о т л и чающееся тем, что блок норма лизации числа содержит одноразрядный блок памяти, элемент РАВНОЗНАЧНОСТЬ, мультиплексор, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы ЗАПРЕТ, элементы И шифратор, первый и второй триггеры и регистр, выход которого является первым выходом блока, второй выход которого соединен с выходами элемента РАВНОЗНАЧНОСТЬ и первого триггера управляющий вход которого соединен с управляющими входами регистра и второго триггера и с вторым входом блока, первый вход которого соединен с .информационными входами мультиплексора и первой группой адресных входов одноразрядного блока памяти, вторая группа адресных входов которого соединена с первым входом элемента РАВНОЗНАЧНОСТЬ, первым информационным входом регистра, адресным входом мультиплексора и третьим входом блока, знаковый выход мультиплексора соединен с первыми входами всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с разрядными выходами мультиплексора, выход каждого элемента ИСКШЗЧАЮЩЕЕ ИЛИ соединен с управляющим входом соответствующего элемента ЗАПРЕТ и первым входом соответствующего элемента И, второй вход каждого элемента И соединен с информационным входом соответствующего элемента ЗАПРЕТ и выходом предыдущего элемента ЗАПРЕТ, выходы элементов И соединены с входами шифратора, выход которого соединен с вторым информационным входом регистра, выход одноразрядного блока памяти соединен с информационным входом первого триггера, выход последнего элемента ЗАПРЕТ соединен с информа- ционным входом второго триггера, выход которого является третьим выходом блока, четвертый вход которого соединен с обнуляющим входом второго триггера, выход первого триггера соединен с вторым входом элемента РАВНОЗНАЧНОСТЬ. 3. Устройство по п. 1, о т л и чающееся тем, что блок управления содержит генератор импульсов, три элемента И, два триггера и мультиплексор, причем третий вход блока соединен с входом сброса мультиплексора, первый и второй управляющие входы которого соединены с прямыми выходами первого и второго три(- геров соответственно, первый и второй информационные входы мультиплексора соединены с шиной сигнала 1, третий и четвертый информационные входы мультиплексора соединены с вторым входом блока, пятый информационный вход мультиплексора соединен с шиной сигнала О, шеСтой информационный вход мультиплексора соединен с первым входом блока, единичны входом первого триггера, нулевым входом второго триггера и входом запуска генератора импульсов, седьмой и восьмой ийформационны.е входы мультиплексора соединены с шиной сигнала 1, первый и второй выходы мультиплексора соединены с информационными входами первого и второго триггеров соответственно, входы первого элемента И соединены с прямым выходом

первого триггера и инверсным выходом второго триггера, выход соединен с вторым выходом блока, первый и второй входы второго элемента И соединены с прямыми выходами первого и второго триггеров соответственно, а выход - с пятым выходом блока, третий выход которого соединен с первым выходом генератора импульсов, первый и второй входы третьего элемента И соединены с инверсными выходами первого и второго триггеров соответ;Ственно, а выход - с первым выходом блока, второй выход генератора импульсов соединен с третьими входами второго и третьего элементов И, четвертым выходом блока и тактирующими входами первого и второго триггеров.

Источники информации, . принятые во внимание при экспертизе

Ц. Авторское свидетельство СССР If 519717, кл. G Об F 15/3, 1975 (прототип).

Фиг.1

Авторы

Даты

1982-06-30—Публикация

1980-06-06—Подача