(Л CL

00

ел

Од

кия, задатчик 4 блок 5 прнрап;ения, :тер в1 |й блок 6 сложе 1ия, первый блок 7 Nfac;mTa6HpoBaFiHB, первый регистр 8, 1терв.1й блок 9 выделения знака и мас- ттабирования, квадратор 10, первый блок 11 умножения, второй блок 12 сложения, первьш блок 13 выделения знака, блок 14 управления, элемент 15 задержки, второй блок 16 масштабирования, третий блок 17 сложения, второй регистр 18, второй блок 19

вычитания, четвертый блок 20 сложения, третий блок 21 вычитания, блок 22 сложения, второй блок 23 вьщеления знака, второй блок 24 умножения, шестой .блок 25 сложения, четвертый блок 26 вычитания, седьмой блок 27 сложения, второй блок 28 выделенных знака и масштабирования. Цель изобретения достигается за счет введения элемента 15, регистра 18 и блоков 15-17, 19-28. 12 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный спектрокоррелометр | 1979 |

|

SU942033A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Устройство для контроля параметров | 1986 |

|

SU1401483A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Аналого-цифровой квадратор | 1983 |

|

SU1120374A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

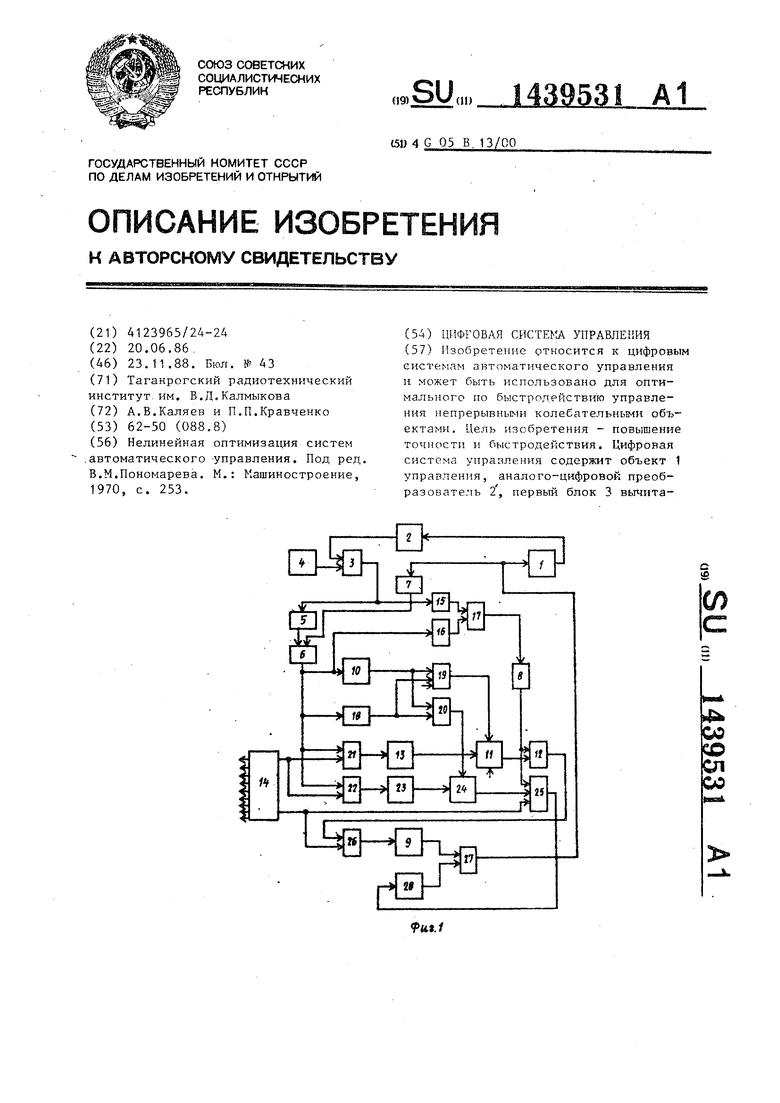

Изобретение относится к цифровым системам автоматического управления и может быть использовано для оптимального по быстродействиго управления непрерывными колебательными объектами. Цель изобретения - повышение точности и быстродействия. Цифровая система управления содержит объект 1 управления, аналого-цифровой преобразователь 2, первый блок 3 вычита

Изобретение относится к цифровым системам автоматического управления и может, быть использовано для оптимального по быстродействию управления непрерывными колебательными объектами типа двух интегрируюа1их звеньев (например, колесными само- ходньп 1И машинами, электроприводами, технологическими процессами) .

Цель изобретения - повьшюние точности и быстродействия.

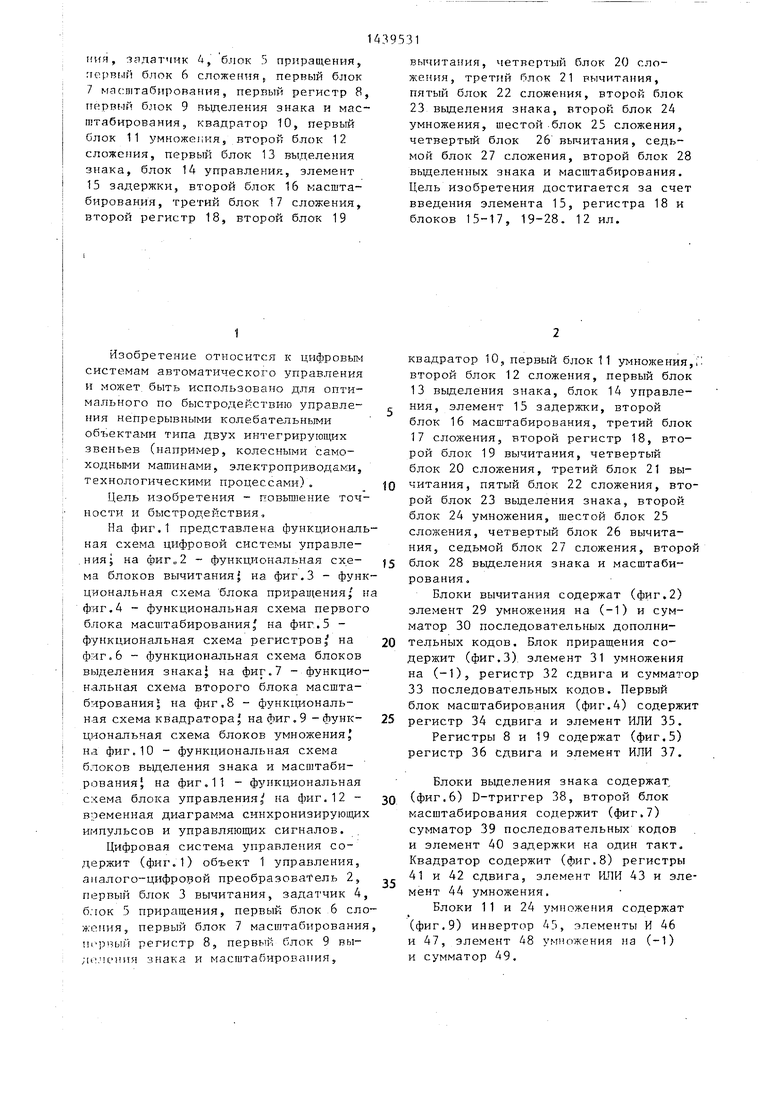

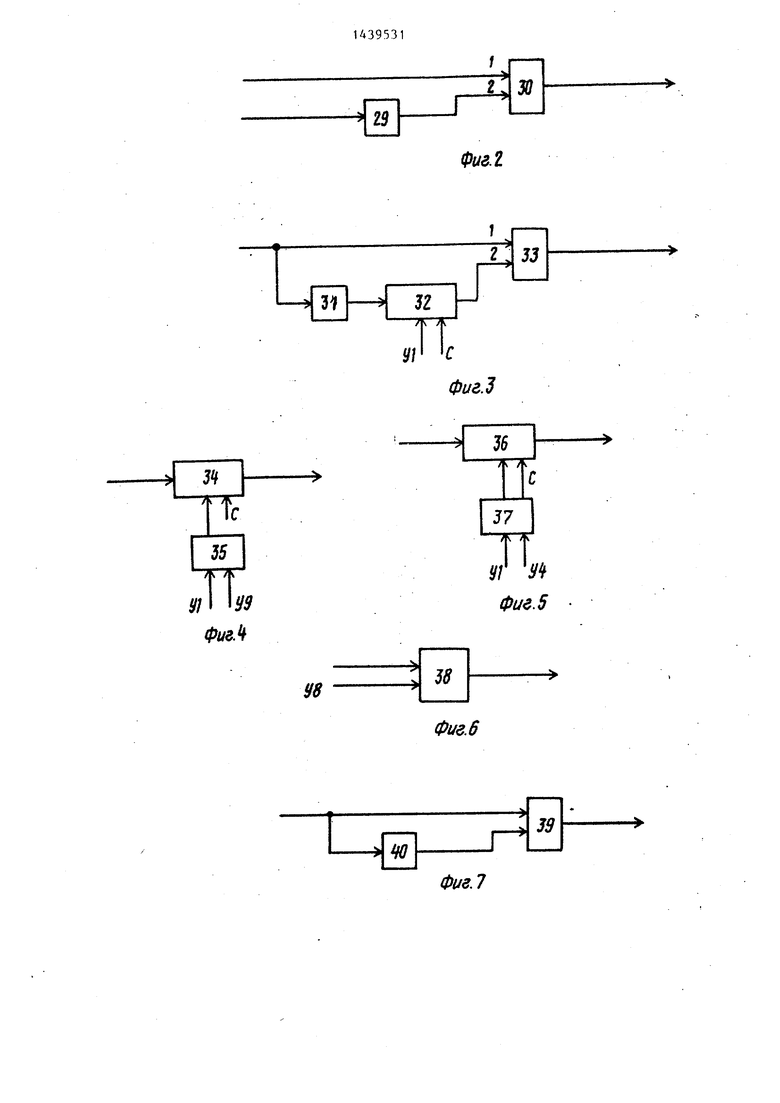

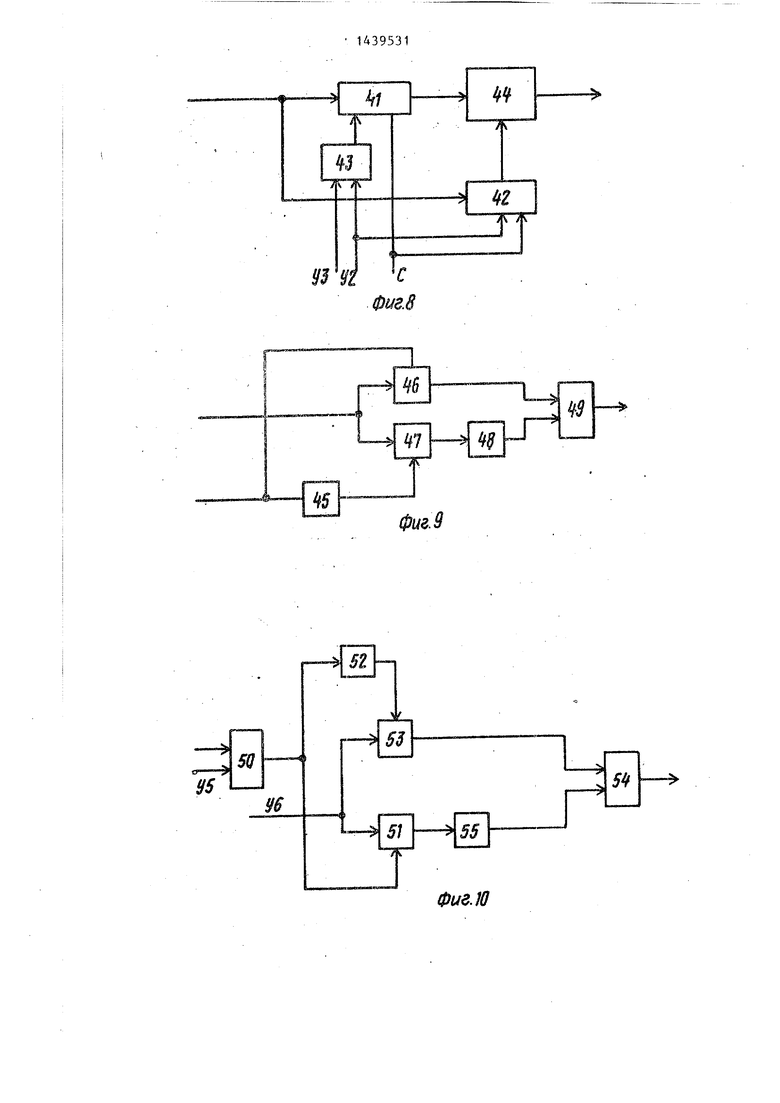

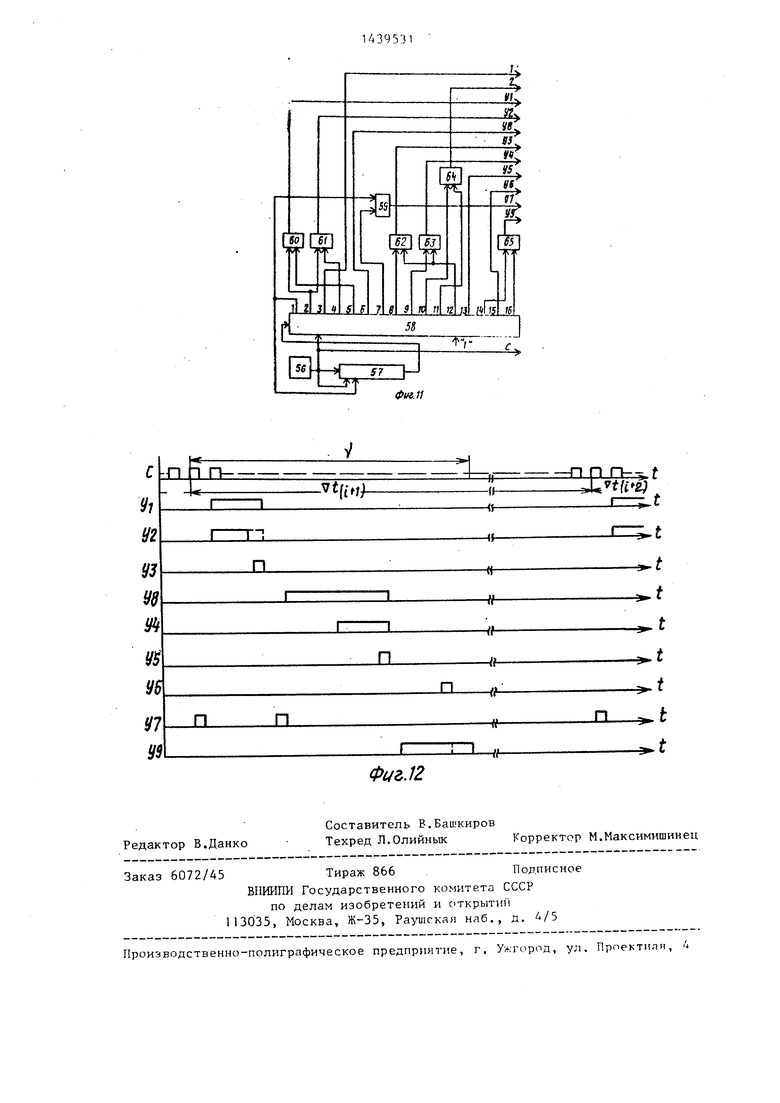

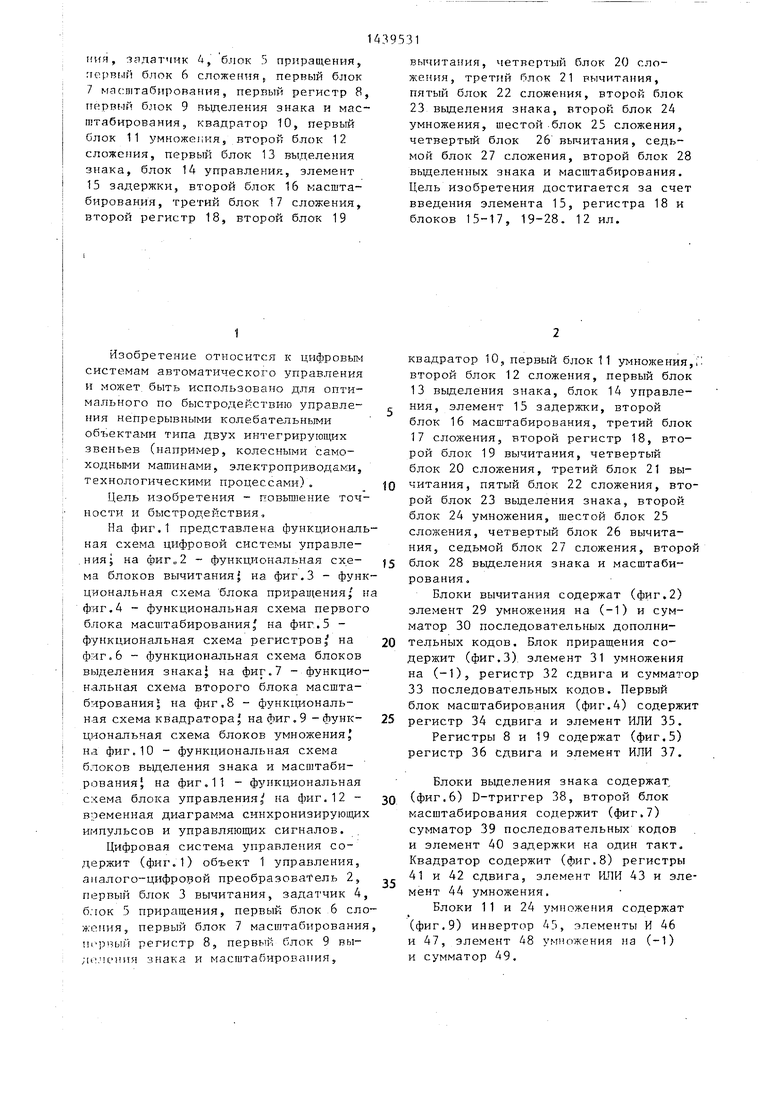

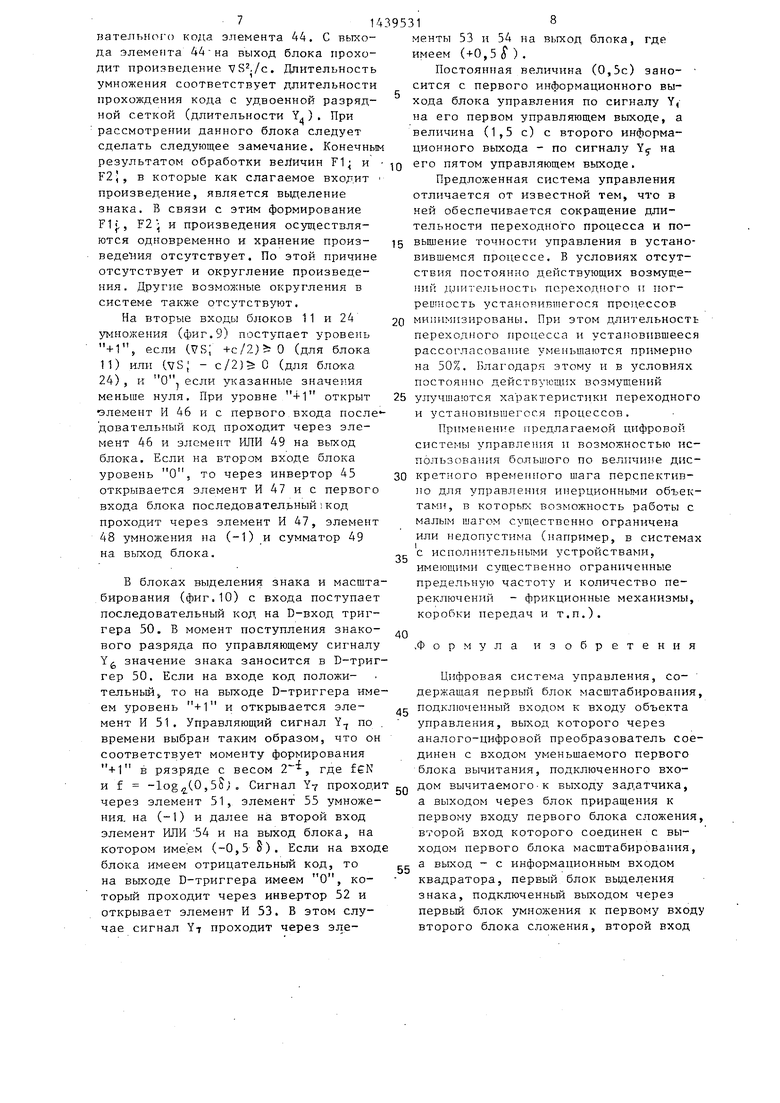

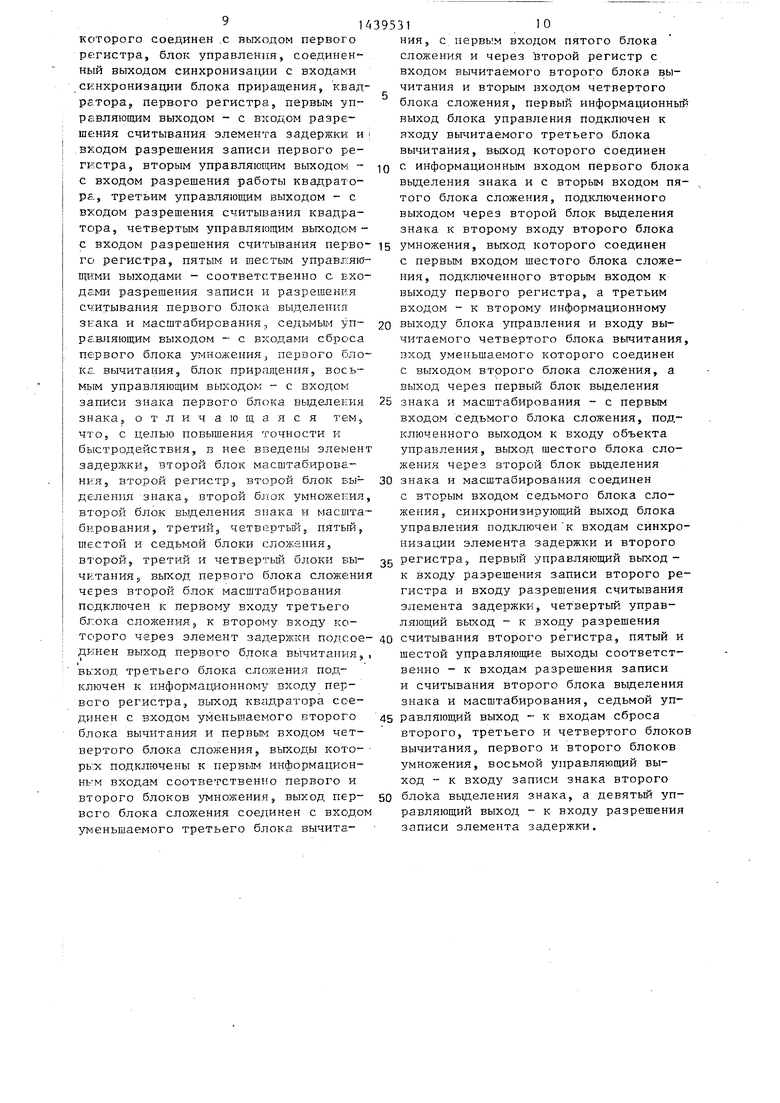

На фиг.1 представлена функциональная схема цифровой системы управле- .ния; на фиг„2 - функциональная схе- ма блоков вычитанияJ на фиг.З - функциональная схема блока приращения, н фиг.4 - функциональная схема первого блока масштабирования на фиг.5 - функциональная схема регистров на фиг,6 - функциональная схема блоков выделения знака на фиг.7 - функциональная схема второго блока масшта- будрования на фиг.8 - функ1щональ- ная схема квадратора J на фиг.9 - функ- циональная схема блоков умноженияJ на фиг.10 - функциональная схема блоков выделения знака и масштаби- рования на фиг,11 - функциональная схема блока управления, на фиг.12 - временная диаграмма синхронизирующих импульсов и управляющих сигналов. ,

Цифровая система управления содержит (фиг.1) объект 1 управления, аналого-цифровой преобразователь 2, первый блок 3 вычитания, задатчик 4, блок 5 приращения, первый блок 6 сложения, первый блок 7 масштабирования пг рвый регистр 8, первый блок 9 вы- ло. и-ния знака и масштабирования.

квадратор 10, первый блок 11 умножения, второй блок 12 сложения, первый блок 13 вьщеления знака, блок 14 управления, элемент 15 задержки, второй блок 16 масштабирования, третий блок 17 сложергия, второй регистр 18, второй блок 19 вычитания, четвертый блок 20 сложения, третий блок 21 вычитания, пятый блок 22 сложения, второй блок 23 выделения знака, второй блок 24 умножения, шестой блок 25 сложения, четвертый блок 26 вычитания, седьмой блок 27 сложения, второ блок 28 вьщеления знака и масштабирования.

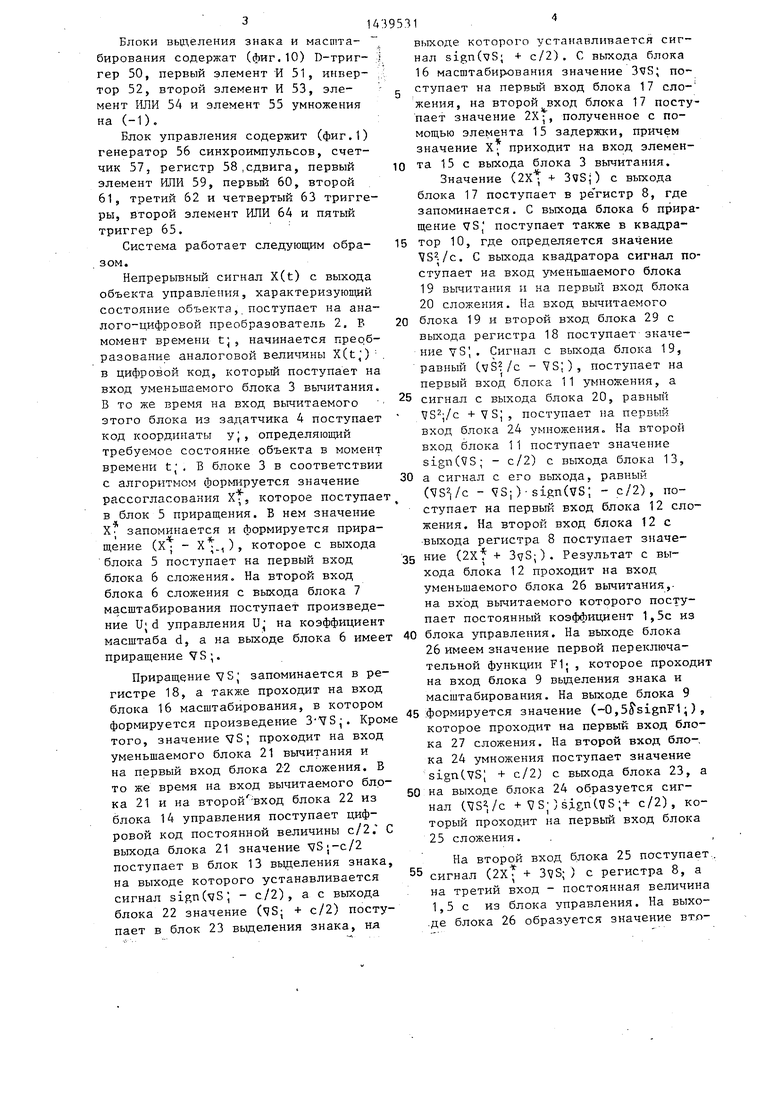

Блоки вычитания содержат (фиг.2) элемент 29 умножения на (-1) и сумматор 30 последовательных дополнительных кодов. Блок приращения содержит (фиг.З). элемент 31 умножения на (-1), регистр 32 сдвига и суммато 33 последовательных кодов. Первый блок масштабирования (фиг.4) содержи регистр 34 сдвига и элемент ИЛИ 35.

Регистры 8 и 19 содержат (фиг.5) регистр 36 сдвига и элемент ИЛИ 37.

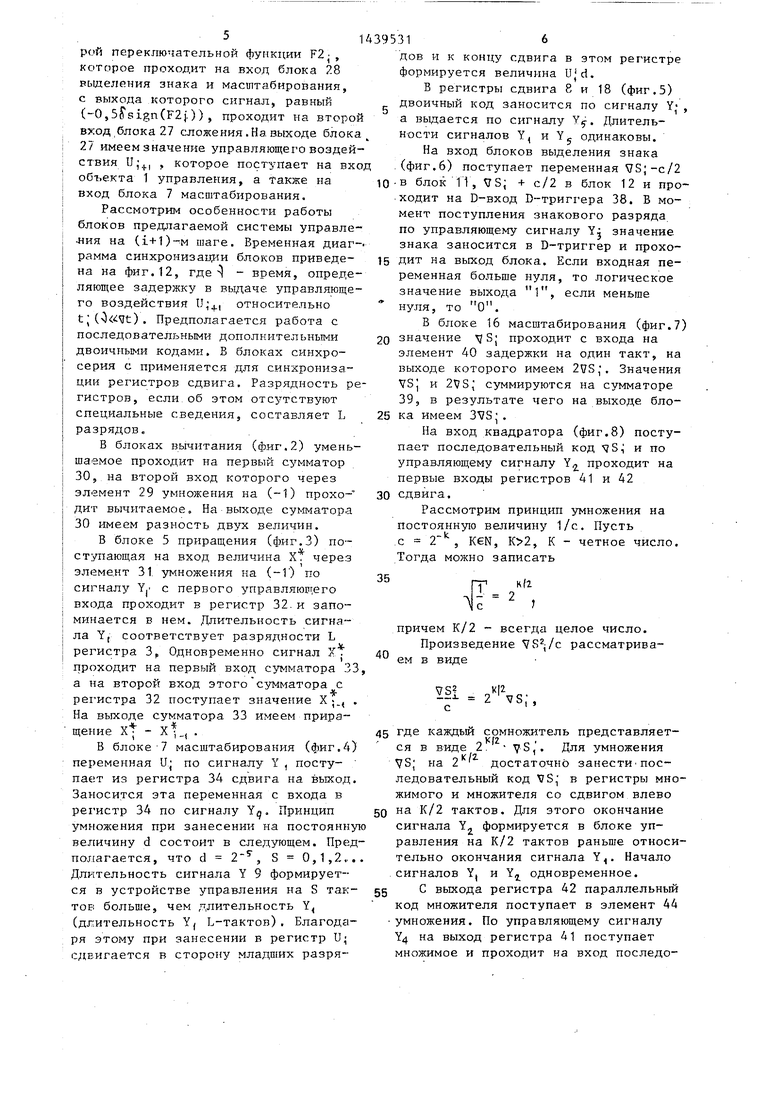

Блоки вьщеления знака содержат, (фиг.6) D-триггер 38, второй блок масштабирования содержит (фиг.7) сумматор 39 последовательных кодов и элемент 40 задержки на один такт. Квадратор содержит (фиг.8) регистры 41 и 42 сдвига, элемент Ш1И 43 и элемент 44 умножения.

Блоки 11 и 24 умножения содержат (фиг.9) инвертор 45, элементы И 46 и 47, элемент 48 умножения на (-1) и сумматор 49.

Блоки выделения знака и мастта- бирования содержат (фиг.10) D-триг- i гер 50, первый элемент И 51, инвертор 52, второй элемент И 53, элемент ИЛИ 5А и элемент 55 умножения на (-1).

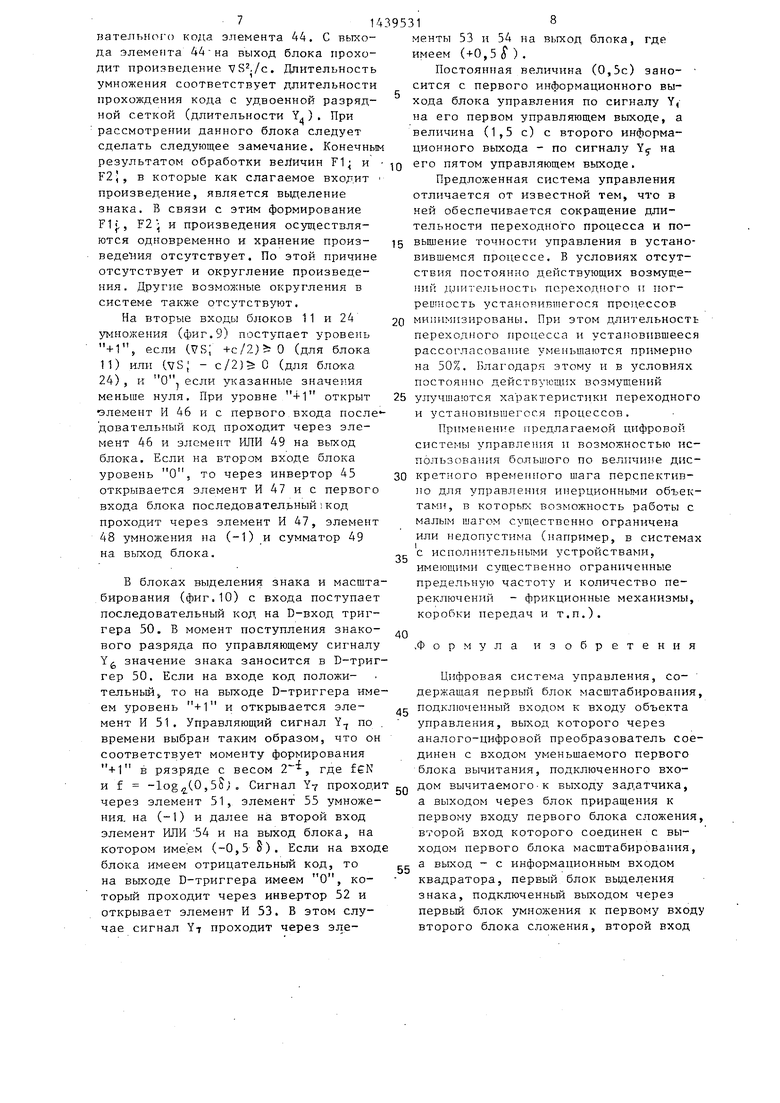

Блок управления содержит (фиг.1) генератор 56 синхроимпульсов, счетчик 57, регистр 58 ,сдвига, первый элемент ИЛИ 59, первьй 60, второй 61, третий 62 и четвертый 63 триггеры, второй элемент ИЛИ 64 и пятый триггер 65.

Система работает следующим образом.

Непрерывный сигнал X(t) с выхода объекта управления, характеризуюЕщй состояние объекта,. поступает на аналого-цифровой преобразователь 2. В момент времени tj, начинается преобразование аналоговой величины X(t,) в цифровой код, который поступает на вход уменьшаемого блока 3 вычитания. В то же время на вход вычитаемого этого блока из задатчика 4 поступает код координаты у;, определяющий требуемое состояние объекта в момент времени t;. В блоке 3 в соответствии с алгоритмом фopмIipyeтcя значение рассогласования X, которое поступает в блок 5 приращения. В нем значение X. запоминается и формируется приращение (X; - Х., ), которое с выхода блока 5 поступает на первый вход блока 6 сложения. На второй вход блока 6 сложения с выхода блока 7 масштабирования поступает произведение Uj d управления U на коэффициент

выходе которого устанавливается сигнал sign(vS; + с/2) . С выхода блока 16 масштабирювания значение 3VS; поg ступает на первый вход блока 17 ело- жения, на второй вход блока 17 поступает значение 2Х;, полученное с помощью элемента 15 задержки, причем значение X; приходит на вход злемен10 та 15 с выхода блока 3 вычитания. Значение (2Х; + 3vS;) с выхода блока 17 поступает в ре гистр 8, где запоминается. С выхода блока 6 приращение 7S, поступает также в квадра15 тор 10, где определяется значение

ЧЗЯ/с. С выхода квадратора сигнал поступает на вход уменьщаемого блока

19вычитания и на первьш вход блока

20сложения. На вход вычитаемого 20 блока 19 и второй вход блока 29 с

выхода регистра 18 поступает значение V S , . Сигнал с выхода блока 1 9, равный ( -VS;), поступает на первый вход блока 11 умножения, а

25 сигнал с выхода блока 20, равный VS2;/c + VSJ , поступает на первы.й вход блока 24 умножения На второй вход блока 11 поступает значение sign(VS; - с/2) с выхода блока 13,

30 а сигнал с его выхода, равный

(VSyc - VS;)-sign(vS; - с/2), поступает на первый вход блока 12 сложения. На второй вход блока 12 с выхода регистра 8 поступает значе 35 ние (2xt + 3vS;). Результат с выхода блока 12 проходит на вход уменьшаемого блока 26 вычитания,, на вход вычитаемого которого постуПриращение VS; запоминается в регистре 18, а также проходит на вход блока 16 масщтабирования, в котором

пает постоянный коэффициент 1,5с из

масштаба d, а на выходе блока 6 имеет 40 блока управления. На выходе блока приращение VS ,26 имеем значение первой переключательной функции Fij , которое проходит на вход блока 9 выделения знака и

масштабирования. На выходе блока 9 олока ID масштаииуоьании, ь AUIUJJUII/ п c ч

о „о тс «а 45 формируется значение (-0,5osignF1;) , формируется произведение 3-VS:, Кроме - t- . ь i

которое проходит на первый вход блока 27 сложения. На второй вход бло-, ка 24 умножения поступает значение sign(VS| + с/2) с выхода блока 23, а 50 на выходе блока 24 образуется сигнал (SVc + VS;)s;Lgn(4S;+ с/2), который проходит на первый вход блока 25 сложения.

На второй вход блока 25 поступает,. 5 сигнал (.2 К + 3VS; ) с регистра 8, а . на третий вход - постоянная величина 1,5 с из блока управления. На выхо- .де блока 26 образуется значение вт.отого, значение VS; проходит на вход уменьшаемого блока 21 вычитания и на первый вход блока 22 сложения. В то же время на вход вычитаемого блока 21 и на второй вход блока 22 из блока 14 управления поступает цифровой код постоянной величины с/2. С выхода блока 21 значение VS;-c/2 поступает в блок 13 выделения знака, на выходе которого устанавливается сигнал sign(vS; - с/2), а с выхода блока 22 значение (S; + с/2) поступает в блок 23 вьщеления знака, нд

выходе которого устанавливается сигнал sign(vS; + с/2) . С выхода блока 16 масштабирювания значение 3VS; поступает на первый вход блока 17 ело- жения, на второй вход блока 17 поступает значение 2Х;, полученное с помощью элемента 15 задержки, причем значение X; приходит на вход злемента 15 с выхода блока 3 вычитания. Значение (2Х; + 3vS;) с выхода блока 17 поступает в ре гистр 8, где запоминается. С выхода блока 6 приращение 7S, поступает также в квадратор 10, где определяется значение

ЧЗЯ/с. С выхода квадратора сигнал поступает на вход уменьщаемого блока

19вычитания и на первьш вход блока

20сложения. На вход вычитаемого блока 19 и второй вход блока 29 с

выхода регистра 18 поступает значение V S , . Сигнал с выхода блока 1 9, равный ( -VS;), поступает на первый вход блока 11 умножения, а

сигнал с выхода блока 20, равный VS2;/c + VSJ , поступает на первы.й вход блока 24 умножения На второй вход блока 11 поступает значение sign(VS; - с/2) с выхода блока 13,

а сигнал с его выхода, равный

(VSyc - VS;)-sign(vS; - с/2), поступает на первый вход блока 12 сложения. На второй вход блока 12 с выхода регистра 8 поступает значение (2xt + 3vS;). Результат с выхода блока 12 проходит на вход уменьшаемого блока 26 вычитания,, на вход вычитаемого которого постурой переключательной функции F2, которое преходит на вход блока 28 рыделрния знака и масштабирования, с выхода которого сигнал, равный (-OjSflsignCFZ).)) , проходит иа второй вход блока 27 сложения.На блока 27 имеем значение управляющего воздействия , которое поступает на вхо объекта 1 управления, а также на вход блока 7 масштабирования.

Рассмотрим особенности работы блоков предлагаемой системы управления на (i+1)--M шаге. Временная диаграмма синхронизации блоков приведена на фиг. 12, где- - время, определяющее задержку в выдаче управляющего воздействия .i относительно t;(). Предполагается работа с последовательными дополнительными двоичными кодами, В блоках синхро- серия с применяется для синхронизации регистро1з сдвига. Разрядность регистров, если,об этом отсутствуют специальные сведения, составляет L разрядов,

В блоках вычитания (фиг.2) уменьшаемое проходит на первый сумматор 30, на второй вход которого через элемент 29 умножения на (-1) прохо- дит вычитаемое. На выходе сумматора 30 имеем разность двух величин.

В блоке 5 приращения (фиг.З) поступающая на вход величина xt через элемент 31. умножения на (-Г) по сигналу Yj- с первого управляюргего входа проходит в регистр 32.и запоминается Е нем. Длительность сигнала Y, соответствует разрядности L регистра 3 Одновременно сигнал Xj проходит на первый вход сумматора 33 а на второй вход этого сумматора с регистра 32 поступает значение Xj., , На выходе сумматора 33 имеем приращение х| - х, .

В блоке 7 масштабирования (фиг,4) переменная U,j по сигналу Y , посту- пает из регистра 34 сдвига на выход. Заносится эта переменная с входа в регистр 34 по сигналу Yg. Принцип умножения при занесении на постоянну величину d состоит в следующем. Предполагается, что d 2 , S 0,1,2,,. Длительность сигнала Y 9 формируется в устройстве управления на S тактов больше, чем длительность Y (длительность Y, L-тактов). Благодаря этому при занесении в регистр 1) сдвигается в сторону младших разряд

14395316

дов и к концу сдвига в этом регистре формируется величина UJd.

В регистры сдвига 8 и 18 (фиг.З) двоичный код заносится по сигналу Y; , а выдается по сигналу . Длительности сигналов Y, и Y одинаковы. На вход блоков выделения знака (фиг.6) поступает переменная 7S;-с/2 в блок 11, VS; + с/2 в блок 12 и про- ходит на D-вход D-триггера 38. В момент поступления знакового разряда по управляющему сигналу Yj значение знака заносится в D-триггер и прохо- дит на выход блока. Если входная переменная больше нуля, то логическое значение выхода 1, если меньше нуля, то О.

В блоке 16 масштабирования (фиг.7) значение проходит с входа на элемент 40 задержки на один такт, на выходе которого имеем 2У8,. Значения VS и 2VS суммируются на сумматоре 39, в результате чего на выходе бло- ка имеем 3VSj.

На вход квадратора (фиг.8) поступает последовательный код vSi и по управляющему сигнгшу Y. проходит на первые входы регистров 41 и 42 сдвига.

Рассмотрим принцип умножения на постоянную величину 1/с. Пусть с 2 , KeN, , К - четное число. Тогда можно записать

35

к (г

40

причем К/2 всегда целое число.

Произведение рассматриваем в виде

if ,

45 где каждьй сомножитель представляется в виде 2. vS, « Для умножения VSj на достаточно занести пос- ледовательный код в регистры множимого и множителя со сдвигом влево

50 на К/2 тактов. Для этого окончание сигнала Y,j формируется в блоке управления на К/2 тактов раньше относительно окончания сигнала Y,. Начало сигналов Y, и Yj одновременное.

55 С выхода регистра 42 параллельный код множителя поступает в элемент 44 умножения. По управляющему сигналу Y4 на выход регистра 41 поступает множимое и проходит на вход последовател,ног() кода элемента 44. С выхода элемента 44 - на выход блока проходит произведение vS./c. Длительность умножения соответствует длительности прохождения кода с удвоенной разрядной сеткой (длительности Y. ). При рассмотрергии данного блока следует сделать следующее замечание. Конечным результатом обработки величин F1 и F2J, в которые как слагаемое входит произведение, является вьщеление знака. В связи с этим формирование Flj:, F2 и произведения осуществляются одновременно и хранение произ- веде ния отсутствует. По этой причине отсутствует и округление произведения. Другие возможные округления в системе также отсутствуют.

На вторые входы блоков 11 и 24 умножения (фиг.9) поступает уровень +1, если (VS; +c/2)5;0 (для блока 11) или (VS| - с/2)5 С (для бло-ка 24), и 0 если указанные значения меньше нуля. При уровне +1 открыт элемент И 46 и с первого входа после - дователы ый код проходит через элемент 46 и элемент ИЛИ 49 на выход блока. Если на втором входе блока уровень О, то через инвертор 45 открывается элемент И 47 и с первого входа блока последовательныйiкод проходит через элемент И 47, элемент 48 умножения на (-1) и сумматор 49 на выход блока.

В блоках выделения знака и масштабирования (фиг.10) с входа поступает последовательный код, на D-вход триггера 50, В момент поступления знакового разряда по управляющему сигналу Y значение знака заносится в D-триг- гер 50. Если на входе код положительный то на выходе D-триггера имеем уровень +1 и открывается элемент И 51 . Управляющий сигнал У по . времени выбран таким образом, что он соответствует моменту формирования +1 в рязряде с весом 2, где

менты 53 и 54 на выход блока, где имеем (+0,5 ).

Постоянная величина (0,5с) заносится с первого информационного выхода блока управления по сигналу на его первом управляющем выходе, а величина (1,5 с) с второго информационного выхода - по сигналу У5- на

10

15

20

его пятом управляющем выходе.

Предложенная система управления отличается от известной тем, что в ней обеспечивается сокращение длительности переходного процесса и повышение точности управления в устано вившемся процессе. В условиях отсутствия постоянно действующих возмущений длительность псреход ого i: пог- реипшсть установившегося процессов минимизированы. При этом длительност переходного процесса и установившеес рассогласование уменьшаются примерно на 50%. Благодаря этому и в условиях постоянно действующих возмущений

25 улучшаются характеристики переходног и установившегося процессов.

Применение предлагаемой цифровой системы управления и возможностью ис п6льзован я большого по вел11чи е дис

30 кретного вреиегигого шага перспективно для управления инерционными объек тами, в которых возможность работы с малым шагом суп(ественно ограничена или недопустима (например, в система с исполнительными устройствами, имеющими существенно ограниченные предельную частоту и количество переключений - фрикционные механизмы коробки передач и т.п.),

40

.Формула изобретени

Цифровая система управления, содержащая первый блок масштабировани л(- подклюг1енный входом к входу объекта управления, выход которого через аналого-цифровой преобразователь со динен с входом уменьшаемого первого блока вычитания, подключенного вхо35

в рязряде с весом

и f -log(0, Сигнал У проходит с„ дом вычитаемого-к выходу задатчика, через элемент 51, элемент 55 умноже- а выходом через блок приращения к ния. на (-1) и далее на второй вход элемент ИЛИ 54 и на выход блока, на котором имеем (-0,5 S), Если на входе блока имеем отрицательный код, то

55

первому входу первого блока сложени второй вход которого соединен с выходом первого блока масштабирования а вькод - с информационным входом квадратора, первый блок выделения знака, подключенный выходом через первый блок умножения к первому вхо второго блока сложения, второй вход

на выходе D-триггера имеем О, который проходит через инвертор 52 и открывает элемент И 53. В этом случае сигнал УТ проходит через элементы 53 и 54 на выход блока, где имеем (+0,5 ).

Постоянная величина (0,5с) заносится с первого информационного выхода блока управления по сигналу на его первом управляющем выходе, а величина (1,5 с) с второго информационного выхода - по сигналу У5- на

его пятом управляющем выходе.

Предложенная система управления отличается от известной тем, что в ней обеспечивается сокращение длительности переходного процесса и повышение точности управления в установившемся процессе. В условиях отсутствия постоянно действующих возмущений длительность псреход ого i: пог- реипшсть установившегося процессов минимизированы. При этом длительность переходного процесса и установившееся рассогласование уменьшаются примерно на 50%. Благодаря этому и в условиях постоянно действующих возмущений

улучшаются характеристики переходного и установившегося процессов.

Применение предлагаемой цифровой системы управления и возможностью ис- п6льзован я большого по вел11чи е дискретного вреиегигого шага перспективно для управления инерционными объектами, в которых возможность работы с малым шагом суп(ественно ограничена или недопустима (например, в системах с исполнительными устройствами, имеющими существенно ограниченные предельную частоту и количество переключений - фрикционные механизмы, коробки передач и т.п.),

.Формула изобретения

Цифровая система управления, содержащая первый блок масштабирования, подклюг1енный входом к входу объекта управления, выход которого через аналого-цифровой преобразователь соединен с входом уменьшаемого первого блока вычитания, подключенного вхо

дом вычитаемого-к выходу задатчика, а выходом через блок приращения к

дом вычитаемого-к выходу задатчика, а выходом через блок приращения к

первому входу первого блока сложения, второй вход которого соединен с выходом первого блока масштабирования, а вькод - с информационным входом квадратора, первый блок выделения знака, подключенный выходом через первый блок умножения к первому входу второго блока сложения, второй вход

которого соединен .с выходом первого ре Гистра, блок управления, соединенный выходом синхронизации с входаки синхронизации блока приращения, квад- рЗ-Тора, первого регистра, первым управляющим выходом с входом разрешения считывания элемента задержки и .входом разрешения записи первого регистра, вторым управляющим выходом - с входом разрешения работы квадратора, третьим управляющим выходом - с входом разрешения считывания квадратора, четвертым управляющим выходом- с входом разрешения считывания перво- го регистра, пятым и шестым управляющими выходами - соответственно с входами разрешения записи и разрешения считывания первого блока выделения: знака и масштабирования,, седьмыдм управляющим выходом - с входами сброса пе-.рвого блока умнолсения, первого блока вычитания, блок приращения, восьмым управляющим выходом - с входом записи знака первого блока выделения знака, отличающаяся тем, что, с целью повышения точности и быстродействия, в нее введены элемент задержки, второй блок масштабирования, второй регистр, второй блок выделения знака, второй блок умножения второй блок вьщеления знака и масштабирования, третий, четвертьм, пятый, шестой и седьмой блоки сложения, второй, третий и четвертьй блоки вычитания, выход первого блока сложения через второй блок масштабирования подключен к первому входу третьего

блока сложения, к второму входу которого через элемент задержки подсое- 40 считывания второго регистра, пятый и

динен выход первого блока вычитания, , выход третьего блока сложения подключен к информац1 гонному входу первого регистра, выход квадратора соединен с входом уменьшаемого второго блока вычитания и первым входом четвертого блока сложения, выходы кото- рь:х подключены к первьм информацион- входам соответственно первого и второго блоков умножения, выход первого блока слойсения соединен с входом уменьшаемого третьего блока вычита5

0

ния, с первым входом пятого блока сложения и через второй регистр с входом вычитаемого второго блока вычитания и вторым входом четвертого блока сложения, первый информационный выход блока управления подключен к входу вычитаемого третьего блока вычитания, выход которого соединен

с информационным входом первого блока выделения знака и с вторым входом пятого блока сложения, подключенного выходом через второй блок вьщеления знака к второму входу второго блока умножения, выход которого соединен с первым входом шестого блока сложения, подключенного вторым входом к первого регистра, а третьим входом - к второму информационному выходу блока управления и входу вычитаемого четвертого блока вычитания, вход уменьшаемого которого соединен с выходом второго блока сложения, а выход через первый блок выделения знака и масштабирования - с первьм входом седьмого блока сложения, подключенного выходом к входу объекта управления, выход шестого блока сложения через второй блок выделения знака и масштабирования соединен с вторым входом седьмого блока сложения, синхронизирующий выход блока управления подключен к входам синхронизации элемента задержки и второго

5 регистра, первый управляющий выход - к входу разрешения записи второго регистра и входу разрешения считывания элемента задержки, четвертый управляющий выход - к входу разрешения

0

шестой управляющие выходы соответст- - к входам разрешения записи и считывания второго блока выделения знака и масштабирования, седьмой уп45 равляюш1ий выход - к входам сброса

второго, третьего и четвертого блоко вычитания, первого и второго блоков умножения, восьмой управляющий выход - к входу записи знака второго

50 блока вьщеления знака, а девятый управляющий выход - к входу разрешения записи элемента задержки.

34

Тс

П

yj У9 ФигЛ

У8

Фиг. 2

У1

и if

Фиг.д

7 k

37

II

ИГ я

фие.5

38

Фиг.6

39

Фиг Л

45

5Q

US

Ив

0us.8

-Ы

I

фие.9

Фие.Ю

| Нелинейная оптимизация систем .автоматического -управления | |||

| Под ред | |||

| В.М.Пономарева | |||

| М.: Машиностроение, 1970, с | |||

| Прибор для измерения угла наклона | 1921 |

|

SU253A1 |

Авторы

Даты

1988-11-23—Публикация

1986-06-20—Подача