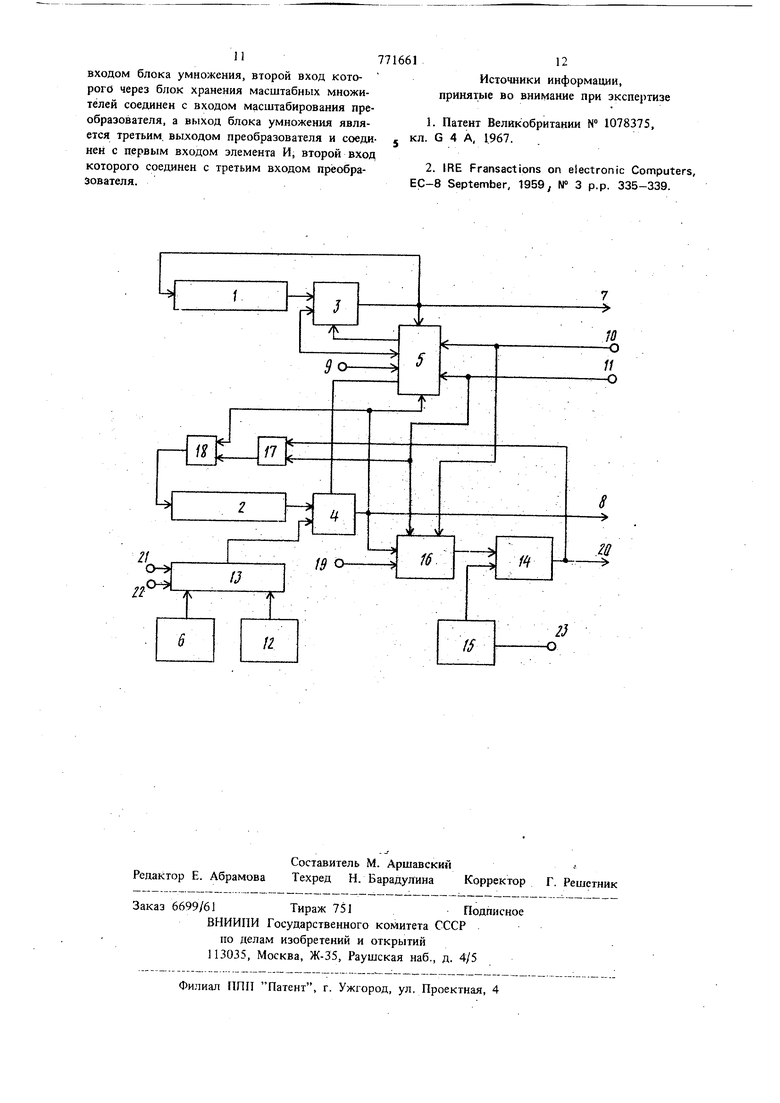

3 чинами часто имеют место случаи, когда цена младшего р;|:;ряда исходного десятичного числа вводимого на преобразование, не совпадает с ценой младшего разряда двоичного кода, -используемого в вычислениях. Точно так имеют место CJтyчaи, когда двоичное число, вводимое на преобразование в десятичное число, имеет цену разряда, неудобную для преобразования и вывода на индикацию. В первом случае требуется выполнять умножение двоичного кода, полученного nocjie преобразования из двоичнодесятичных тетрад на масштабный множитель. Во втором случае на масштабный множитель требуется умножать двоичное число, поступающее на преобразованные в двоично-десятичные тетрады. Целью изобретения является расширение функциональных возможностей преобразователя заключающееся в обеспечении возможности мас штабирования и в преобразовании кодов с про извольным разбиением на группы десятичных разрядов. Цель достигается тем, что реверсивный преобразователь двоичного кода в двоично-десятич ный код, содержащий первый и второй сдви1;овые регистры, блок хранения констант перевода угловых величин, первый и второй сумма торы-вычитатели, первые входы которых соединены с выходами соответствующих сдвиговых регистров, блок управления, первый и второй выходы которого соответственно соединены с управляющими входами сумматоров-вычитателей выходы которых являются первым и вторым выходами преобразователя и соединены соответ ственно с первым и вторым входами блока. управления, третий выход которого соединен со вторым входом первого сумматора-вычитателя, вход первого сдвигового регистра соединен с первым входом блока управления, третий четвертый и пятый входы которого являются соответственно первым информационным, первым и вторым входами переключения режимов работы преобразователя, дополнительно содержит блок хранения констант перевода метричес ких величин, коммутатор констант, блок умножения, блок хранения масштабных множителей коммутатор переключения режимов, элемент И элемент ИЛИ, первый вход которого соединен с выходами элемента И, второй вход соединен с выходом второго сумматора-вычитателя и с первым входом коммутатора переключения режимов, а выход элемента ИЛИ соединен со вхо дом второго сдвигового регистра, выходы блоков хранения констант перевода угловых величин и констант перевода метрических величин соединены соответственно с первым и вторым входами коммутатора констант, третий и четвертый входы которого являются первым и вторым входами (ра констант преобразова I4 теля, а зыxoд коммутатора констант соединен со вторым входом второго сумматора-ьычигателя, первый, второй входы переключения режимов работы и второй информационный вход преобразователя соединены соответственно со вторым, третьим и четвертым входами коммутатора перек;гючения режимов, выход которого соединен с первым входом блока умножения, второй вход которого через блок хранения масщтабных множителей, соединен с входом масштабирования преобразователя, а выход блока умножения является третьим вы)(одом преобразователя и соединен с первым входом элемента И, второй вход которого соединен с третьим входом преобразователя. Структурная схема предлагаемого преобразователя приведена на чертеже. Предлагаемый преобразователь содержит первый и второй сдвиговые регистры 1 и 2, первый и второй сумматоры-вь1читатели 3 и 4, блок управления 5 и блок хранения 6 констант перевода угловых величин. Выходы младших разрядов сдвиговых регистров 1 и 2 подключены к первым входам соответствующих сумматоров-вьшитателей 3 и 4, которых подключены к первому и второму входам блока управления 5. Выход сумматора-вычитателя 3 подключен к. входу старшего разряда регистра 1. Выходы первого и второго сумматороввычитателей 3, 4 являются первым и вторым выходами 7, 8 преобразователя. Третий, четвертый и пятый входы блока управления 5 соеда иены с первым информационным входом преобразователя 9; первым 10 и вторым 11 входами переключения режимов работы преобразователя. Предлагаемый преобразователь включает в свой состав блок хранения 12 констант перевода метрических величин, к;оммутатор 13 констант, блок умножения 14, блок хранения 15 масштабных множителей, коммутатор 16 переключения режимов, элемент И 17 и элемент ИЛИ 18. Входной двоичный код поступает через второй информационный вход 19 преобразователя и проходит на его третий выход 20. При переводе физических величин, заданных в метрической системе мер с десятичными подразделениями между разрядами, в двоичную систему переводимое десятичное число записывается в сдвиговый регистр 1 в виде тетрад, представленных в плюс-минус коде. Для п разрядного десятичного числа имеем: х(п) ( + 2Ь -t- 1Ь + 0,5|i 4,5) МО + (. + 2Ь + 1Ь + 0,5 + н- 4,5). + ( + 2Ь + + + 0,5|i -ь 4,5)- 10 + ( + 2Ь + + 1Ь + 0,5, + 4,5). 10°, где + 1, -1

или

x(n) ( + 2Ь + 1Ь + 0, ) 10 +

И--)

+ ( + 2Ь + 1Ь 0,)- 10

+ ( + 2Ь + 1Ь -I- 0,5)- 10 +

+ ( + 2Ь + 1Ь- + 0,5,)10° +С гдеС 4,510 4,5- 10 + ... + 4,5.10 + + 4,5-10°.

ЛУЧ

t , как следует из первой формулы, определяется числом тетрад,

Число тетрад и соответственно длина сдвиговых регистров выбирается заранее, исходя из требуемого числа десятичных разрядов преобразуемой величины.

Для выполнения преобразования следует имет двоичные коды коэффициентов при переменных ii +1,.-1 и двоичный код постоянной С которые содержатся в блоке хранения 12 констант перевода метрических величин. Подключение блока хранения констант перевода угловых величин или блока хранения констант перевода метрических величин к второму входу сумматора-вычитателя 4 осуществляет коммутатор 13 констант при подаче на его первый и второй входы 21, 22 выбора констант соответствующих сигналов на переключение.

Кроме того, необходимо иметь двоичные коды масштабных множителей, которые записаны в блоке хранения 15 масштабных множителей, Число масштабных множителей определяется числом преобразуемых величин. Выбор масштабного множителя из блока 15 и выдача его на второй вход блока умножения 14 осушествляется сигналом, подаваемым на вход 23 масштабирования преобразователя.

Для преобразования угловых величин блок хранения 6 констант перевода подключен через коммутатор констант 13 к второму входу сум.матора-вычитателя 4. При выполнении преобразрвания десятичного кода угловых величин в двоичный код исходная величина угла, выраженная в диадах, триадах, тетрадах, содержитс/i в сдвиговом регистре 1. Результат преобразования накапливается в двоичном коде в сдвигоBOM регистре 2 и поступает на выход 8 преобразователя. Этот вид преобразования угловой величины происходит следующим образом.

При выполнении преобразования двоично-десятичного кода угла, выраженного диадой сотен градусов, тетрадой десятков градусов и т.д. в двоичный код, выраженный в долях оборота на вход 10 преобразователя поступает сигнал, разрешаюший выполнение данного вида преобразования. По этому сигналу вход 9 преобразователя соединяется со вторым входом сумматора-вычитателя 3, а управляющие входы сумматоров-вычитателей 3 и 4 подсоединяются к выходу сумматора-вь читателя 3..

Все пресхтразовакие выполняется ja ,п 1 шаг, где п -- число двоичных разрьяов в сдвиговых регистрах I и 2.

На каждом шаге преобразования происходи г проверка значения разрядов двоично-десятичного кода угла, содержащегося в сдвиговом регистре 1,и формирование управляющего оператор Pj 0,1 в зависимости от результата этой проверки. Этот оператор пост т1ает на входы управления сумматоров-вычлтателей 3 и 4 и выполняет их. установку на сложение-или вычитание, причем сумматоры-вычитатели устанавливаются на противоположные действия. В сдвиговом регистре 2 происходит накопление констант, содержащихся в блоке хранения 6 констант перевода углов. В нем содержатся поправочный угол Ci-. вытекающий из исполь зования при преобразовании плюс-минус кода, и константы, являюшиеся эквивалентными весовых значений разрядов в диадах, триадах, тетрадах и т.д. сдвигового регистра 1. Все константы представлены двоичным кодом долей оборота.

В конце преобразования в сдвиговом регистре 2 накапливается двоичный код преобразуемого угла в долях оборота.

W

М, .

где (

- константы i-ro щага;

-1 - знак константы i-ro шага, определяемый управляюшим оператором Pj 0,1.

На первом шаге на вход 9 преобразователя подается число 2 , которое через блок управления поступает на второй вход сумматора-вычитателя 3. На первьЕЙ вход сумматора-вычитателя 3 поступает содержимое сдвигового регистра 1. В блоке управления 5 вырабатывается управляющий оператор pi О, который устанавливает сумматор-вычитатель 4 на сложение. Результат вычитания с выхода сумматора-вычитателя 3 вновь записывается в сдвиговый регистр 1. Знак разности, полученный на выходе сумматора-вычитателя 3, поступает в блок управления 5, где по его значению формируется управляющий оператор q 0,1, вьпюлняющий установку сумматоров-вычитателей 3 и 4 на следующем шаге. Одновременно с этим на второй вход сумматора-вычитателя 4 с выхода блока хранения 6 поступает код поправочного угла, который, пройдя через сумматор-вычитатель 4, записывается в сдвиговый регистр 2.

На втором шаге в зависимости от значения 42 0,1 сумматоры-вычитатели устанавливаются на вьшолнение следующего лепствия: 7 (0, сумматор 3 на -, сумматор 4 наЧ ( 1, сумматор 3 на +, сумматор 4 на -. Иа вход 9 преобразователя подается число 2 , которое через блок управления 5 поступает на второй вход сумматора-вычитателя 3 и складывается (вычитается) с содержимым . сдвигового регистра 1, полученным после выполнения первого шага. Знак результата на выходе сумматора-вычитателя 3 определяет оператор Яз для следующего шага. Одновременно на второй вход сумматоравычитателя 4 поступает с выхода блока хранения 6 двоичный код угла 100 Ij и складывается (вычитается) с содержимым сдвигового регистра 2. После выполнения второго шага в сдвиговом регистре 2 содержится двонч1й ш код угла . . litC. +Ь 100,, где 12 - На (п+1)-ом шаге в результате суммирова, НИН (вычитания) двоичных ксшстант, содержащихся в блоке хранения 6, в сдвиговом регист ре 2 будет получен двоичный код преобразуемого угла в долях оборота al2 + При выполнении преобразования двоичных кодов угловых величин в десятичный код исходная величина угла записывается в сдвиговом регистре 2. Результат преобразования в ви де диод, триод и тетрад накапливается в сдвиговом регистре 1. Для выполнения преобразования двоичного кода угла, выраженного в долях оборота, в двоично-десятичный код, выраженный диодой сотен градусов, тетрадой десятков градусов и т.д., на вход 11 блока управления 5 поступает сигнал, разрешающий -выполнение этого преобразования. В результате этого на все время преобразования сумматор-вычитатель 3 устанавливается на сложение, а сумматор-вычи: татель 4 управляется оператором, формируемым в блоке управления 5 на каждом шаге в зависимости от знака числа на выходе сумматоравычитателя 4. Кроме того, этот управляющий оператор управляет поступлением чисел со входа 9 преобразователя на второй вход сумматор вычитателя 3. В сдвиговом регистре 2 в исход Ном состоянии записан двоичный код преобразуемого угла а 2, а сдвиговый регистр 1 очищен. На первом шаге в блоке управления 5 выра .батывается управляющий оператор qj О, который устанавливает сумматор-вычитатель 4 на вычитание. Из блока хранения 6 констант перевода углов на второй вход сумматора-вычитателя 4 поступает двоичный код поправочного угла , который вычитается из содержимого СДВИ1-ОВОГО регистра 2, в результате чего 18 на выходе сумматора-вычитателя 4 и соответственно в сдвиговом регистре 2 получается число XJ tola + li , где f, -1. В блоке управления анализируется знак этого числа и формируется управляющий оператор для второго шага qj 0,1. На втором шаге на вход 9 преобразователя поступает число 2 , которое в зависимости от значения управляющего оператора Яз 0,1 проходит или не проходит на второй вход сумматора-вычитателя 3. Ш - число проходит. U - число не проходит. Число 2 , пройдя через сумматор-вь1читатель 3, записывается в старшем разряде сдвигового регистра 1 в виде старшего разряда диады. Одновременно с этим на второй вход сумматора-вычитателя 4 из блока хранения 6 коистант перевода углов поступает двоичный код угла , а на первый вход его из сдвигового регистра 2 поступает результат первого шага Xi 2. Сумматор-вычитатель 4 в зависимости от управляющего воздействия q2 устанавливается на сложение иди вычитание. iO - на вычитание, 1 - на сложение. На выходе сумматора-вычитателя 4 и в сдвиговом регистре 2 в результате выполнения второго шага формируется число Л212 а 2 + stcWlj + al100° 2, где(-1, если qa О (+1, если qa 1., Аналогичным образом на следующих шагах определяются и записываются в сдвиговом регистре 1 значения двоично-десятичного кода угла. В конце преобразования на (п + 1)-ом шаге в сдвиговом регистре 1 содержится значение разрядов двоично-десятичного кода в виде диады, триад и тетрад, которые соответствующим образом расшифровываются для индикации. Работа устройства при выполнении преобразования десятичных кодов физических величин, заданных в метрической системе мер с десятичными подразделениями между разрядами, в двоичный код происходит следующим образом. На вход 10 преобразователя„поступает сигнал, включающий этот режим работы, как и при преобразовании утповых величин. Кроме того этот сигнал в коммутаторе 16 переключения режимов подключает выход сумматора-вычитателя 4 к первому входу блока умножения 14. Л на вход 22 преобразователя поступает сигнал, выполняющий подключение блока 12 хранения констант перевода метрических величин

через коммутатор констант 13 к второму входу сумматора-вычитателя 4.

Исходное десятичное число в виде двоичнодесятичных тетрад с избытком 3 записыв.ается в сдвиговый регистр 1. Преобразование выполняется аналогично описанному выше, но с использованием констант, содержащихся в блоке констант перевода метрических величин 12.

После выполнения преобразования двоичный код числа с выхода сумматора-вычитателя 4 через коммутатор 16 поступает на первый вход блока умножения 14. Hai второй вход блока умножения 14 поступает ;:-оичный код масштабного множителя. После двоичного кода числа на масштабный множитель двоичный 15 код числа с требуемой для дальнейшего использования ценой младшего разряда поступает на выход 20 .преобразователя. Работа устройства при преобразовании двоичного кода вдесятичный происходит следующим 20 образом. Блок 12 хранения констант по-прежнему подключен через, коммутатор констант 13 ,к второму входу сумматора-вычитателя 4. На вход 11 преобразователя поступает сигнал, включающий блок управления на выполнение этого вида преобразования. Кроме того, этот сигнал через коммутатор 16 переключения режимов подключает вход 19 преобразователя к первому входу блока умножения 14, а также подключает выход блока умножения 14 через элемент И 17 и элемент ИЛИ 18 к входу сдвигового регистра 2. Двоичный код преобразуемого числа поступает через коммутатор переключения режимов 16 на первый вход блока умножения 14. На второй вход блока умножения с выхода блока хранения 15 масштабных множителей поступает соответствующий масштабный множитель. После вьшолнения умножения на выходе блока умножения 14 имеет место двоичный код числа с ценой младшего разряда, удобной для пре образования, который поступает через элемент И 17 и элемент ИЛИ 19 на вход сдвигового регистра 2 для преобразования двоичного кода в двоично-десятичный. Преобразование двоичного кода в десятичный выполняется аналогично описанному выше, но с использованием констант, содержащихся в блоке хранения констант перевода метрических величин. Результат преобразования в виде тетрад с избытком 3 накапливается в сдвиговом регистре 1 и поступает на выход 7 преобразователя. Технико-экономический эффект от использования предлагаемого преобразователя заключается в расширении его функшюнальных возмож ностей. Предлагаемое техническое решение в отличие от известных позволяет выпотшять преобразование, десятичного кода в двоичный и обратно

как для угловых величин, выраженных в градусах, минутах и секундах, так и для других физических величин, выраженных в метрической системе мер с десятичными подразделениями между разрядами с изменением масштаба (цены разрядов) двоичных кодов.

Формула изобретения

Реверсивный преобразователь двои1ного кода в двоично-десятичный код, содержащий первый и второй сдвиговые регистры, блок хранения констант перевода угловых величин, пер25вый и второй сумматоры-вычитатели, первые входы которых соединены с выходами cooTBCifствующих сдвиговых регистров, блок управления, первый и второй выходы которого соответственно соединены с управляющими входами сумматоров-вычитател Й, выходы которых являются первым и вторым выходами преобразователя и соединены соответственно с первым и вторым входами блока управлеш1я, третий выход которого соединен со вторым входом первого сумматора-вычитателя, вход первого сдвигового регистра соединен с первым входом блока управления, третий, четвертый и пятьп1 входы которого являются соответственно первым информационным, первым и вторым skoдами переключения режимов работы преобразователя, отличающийся .тем, что, с целью расширения функциональных возможностей, заключающегося в обеспечении возможности масштабирования и в преобразовании кодов с произвольным разбиением на группы десятичных разрядов, в него введен блок хранения констант перевода метрических величин, комм т:атор констант, блок умножения, блок хранения масштабных множителей, коммутатор переключения режимов, элемент И, элемент ИЛИ, первый вход которого соединен с выходом элемента И, второй вход соединен с выходом второго сумматора-вь читателя и с первым входом коммутатора переключения режимов, а выход элемента ИЛИ соединен со входом второго сдвигового регистра, выходы блоков хранения констант перевода зтловых величин и констант перевода метрических величин соединены соответственно с первым и вторым входами коммутатора констант, третий и четвертый входы которого являются первым и вторым входами выбора констант преобразователя, а выход коммутатора констант соед11нен со вторым входом второго сумматора-вычитателя, первый, второй входы переключения режимов работы и второй информашюнный вход преобразователя соединены соответственно со вторым, третьим и четвертым входами коммутатора переключения режимов, которого сое;1и.чсн с первым входом блока умножения, второй вход которого через блок хранения масштабных множителей соединен с входом масштабирования преобразователя, а выход блока умножения является третьим, выходом преобразователя и соединен с первым входом элемента И, второй вход которого соединен с третьим входом преобразователя. 112 Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № 1078375, кл. G 4 А, 1967. 2.IRE Fransactions on electronic Computers, EC-8 September, 1959 tf 3 p.p. 335-339.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1979 |

|

SU877521A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода в двоично-десятичный с масштабированием | 1978 |

|

SU771662A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

Авторы

Даты

1980-10-15—Публикация

1978-10-20—Подача