ВС 10

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Цифровой линейный интерполятор с оценочной функцией | 1981 |

|

SU991375A1 |

| Цифровой линейный интерполятор | 1990 |

|

SU1805449A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для формирования векторов на газоразрядной индикаторной панели | 1988 |

|

SU1642509A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Линейный интерполятор | 1985 |

|

SU1282084A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

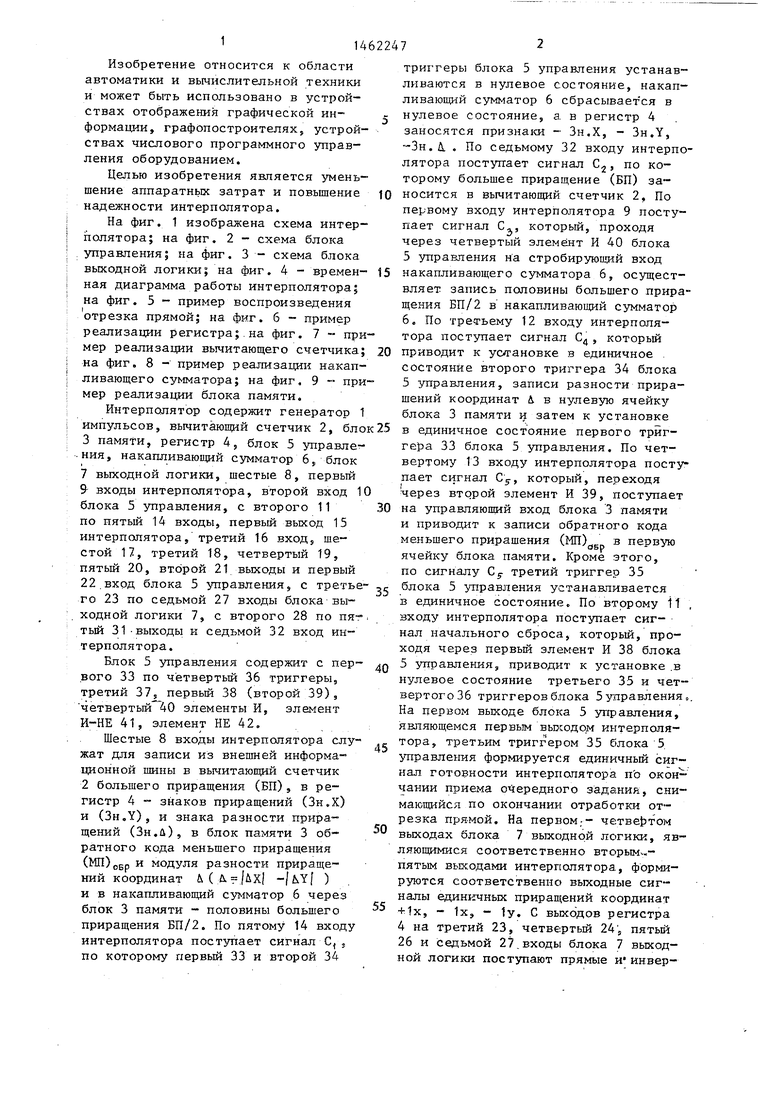

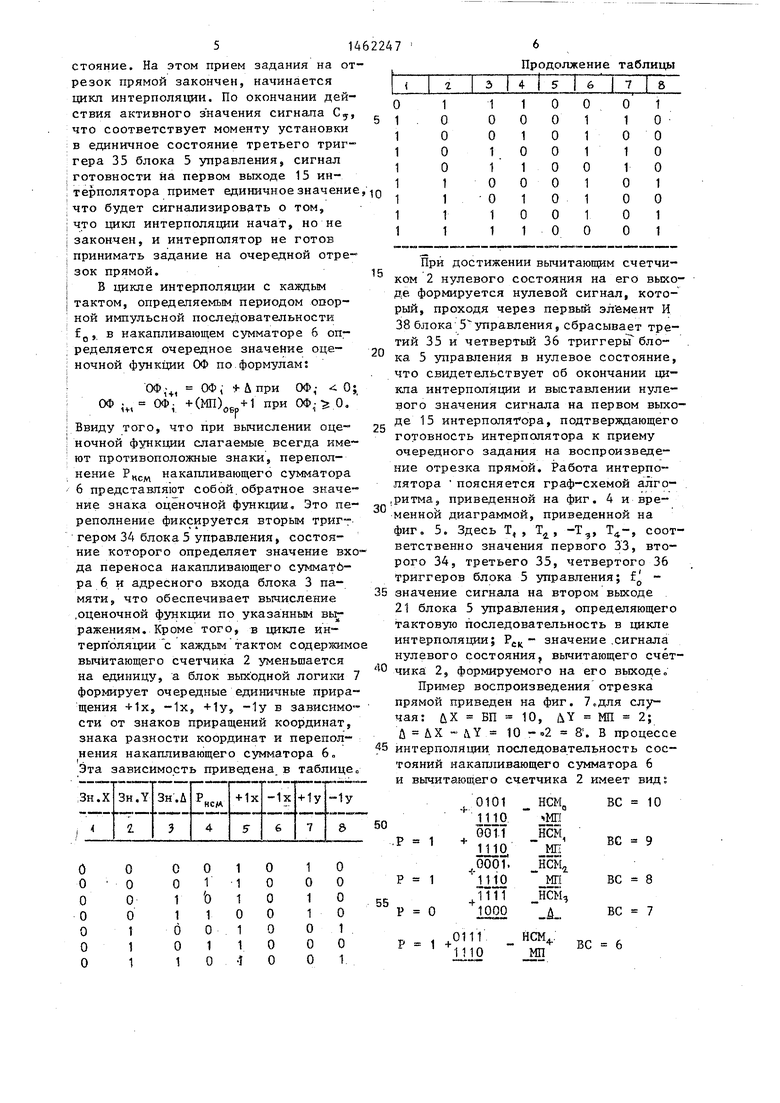

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройст-. вах отображения графической информации, графопостроителях, устройствах числового программного управления оборудованием. Целью изобретения является уменьшение аппаратурных затрат и повышение надежности интерполятора. Интерполятор содержит ратор импульсов 1, вычитающий счетчик 2, блок памяти 3; регистр 4, блок управления 5, накапливающий сумматор 6, блок выходной логики.7. Введение в интерполятор блока памяти позволило исключить такие аппара- турно-емкие блоки как два полноразрядных регистра, два полноразрядных коммутатора, полноразрядные блоки вентилей и инверторов, а также повысить надежность интерполятора за счет уменьшения количества связей между его элементами и блоками. 1 з.п. ф-лы, 9 ил., 1 табл. s w JiA

.Р

ЕС

Р

ВС 8

55

ВС 7

0101

р

HCMg мп

HCMj

Jffl

нсм ш

HCMg

u

нем, мп

НСМ,о

вс

вс

вс

вс

вс

вс о

10

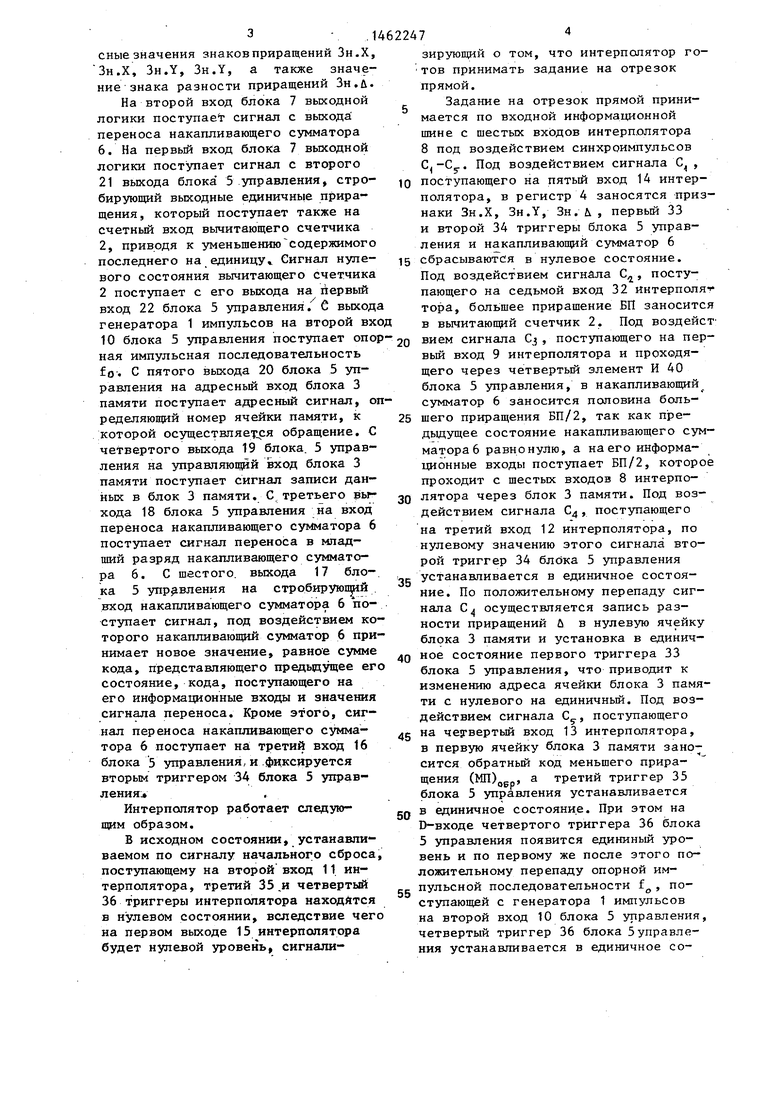

Здесь НСМ; - состояние накапливающего сумматора 6 в i-м тактеi ВС - состоя-ние вычитающего счегчийа 2.

Блок 7 выходной логики, реализующий систему функций, заданную указанной таблицей истинности, в одном из примеров может быть реализован, как показано на фиг. 3. В этом случае он содержит элементы НЕ 43 и 50, элементы И-НЕ 44-49.

Регистр 4 (фиг. 6) .вьшолнен на основе .регистра с прямыми и инверсными входами 51.

Пример реализаций вычитающего. счетчика 2 приведен на фиг. 7. Он содержит элемент И 52 и реверсивные счетчики 53.

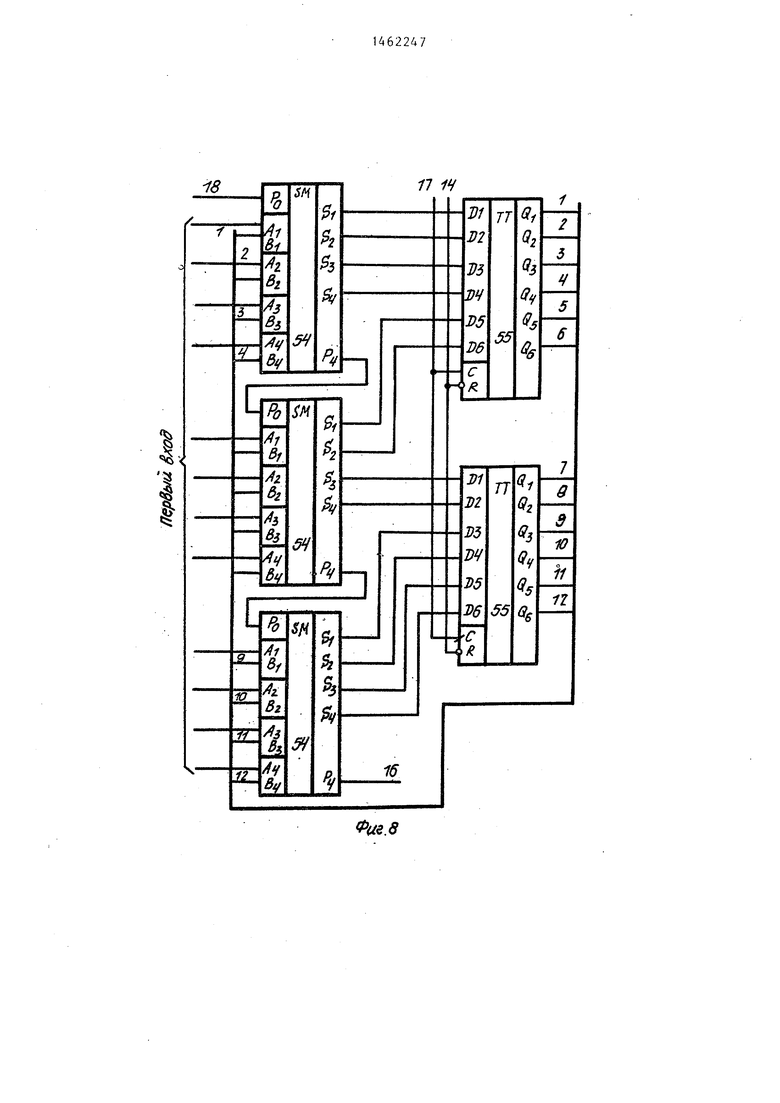

Пример реализации накапливающего сумматора 6 приведен на фиг. 8. Он содержит сумматоры 54 и регистр 55.

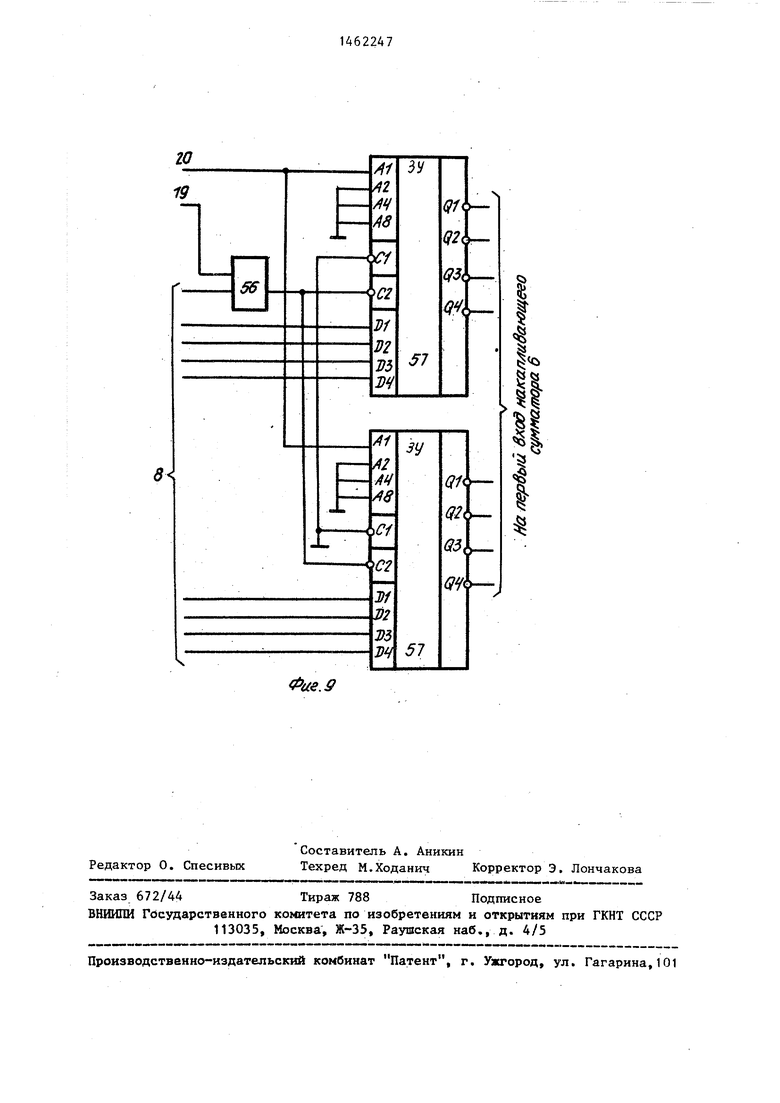

Пример реализации блока памяти 3 приведен на фиг. 9. Он содержит элемент И 56 и элементы 57 памяти. На один из входов элемента И 56 с одного из шестых входов 8 иатерполято- ра одновременно со значением БП/2 поступает сигнал записи его в блок 3 памяти. Блок памяти при наличии сиг- - нала записи на входах С 2 элементов памяти пропускает информацию с

большего приращения, меньшего приращения и разности приращений нат, что позволило исключить такие с аппаратно-емкие блока, как два полно- разрядных регистра, два псшноразряд- ных коммутатора, полноразрядные блок вентилей и инверторов.

Значительное упрощение интерпо- . лятора позволяет существенно улучшить такие технико-экономические характеристики, как габаритные размеры, потребляемая мощность, трудоемкость в изготовлении, стоимость, вес, не снижая быстродействия и точности, упростить стыковку интерполятора с другими устройствами средств отображения и регистрации графической информации.

Повышение надежности интерполятора обеспечивается за счет уменьшения количества связей между его элементами и блоками,

15

20

25

Формула изобретения

35 выход блока управления является первым -выходом интерполятора, второй выход блока управления соединен со счетным входом вычитающего счетчика и первым входом блока выходной логи40 ки, третий, выход блока управления соединен с входом переноса накапливающего сумматора, выход которого подключен к третьему входу блока управления, отличающийся

тов памяти пропускает информе1цин, с- уменьшения аппаратшестых входов 8 интерполятора на свои fb повышения надежности

50

ных затрат и повышения надежности интерполятора, в него введен блок памяти, управляющий и адресньй входы которого подключены соответс твенно к четвертому и пятому выходам блока

управления, а выходы - к информавыходы, а в отсутствие сигнала записи (режим чтения) информация на выходах блока 3 памяти определяется значением сигнала на его адресном входе и содержимым нулевой или первой ячейки памяти. - ционным входам накапливающего сумматора, выход которого подключен к второму входу выходного блока логики,

п o:lящiи к определению оценочной, функ- 55 а стробирующий вход соединен с шестым Накапливающем сумматоре на ос- вьпсодом блока управления, у которого нове определенных вне интерполятора и предварительно размещенных в накапливающем сумматоре и блоке памяти .

Введение в интерполятор блока памяти позволило свести процесс интервходы с четвертого по седьмой являются соответственно с первого по четвертый входами интерполятора, при

10

большего приращения, меньшего приращения и разности приращений нат, что позволило исключить такие с аппаратно-емкие блока, как два полно- разрядных регистра, два псшноразряд- ных коммутатора, полноразрядные блок вентилей и инверторов.

Значительное упрощение интерпо- . лятора позволяет существенно улучшить такие технико-экономические характеристики, как габаритные размеры, потребляемая мощность, трудоемкость в изготовлении, стоимость, вес, не снижая быстродействия и точности, упростить стыковку интерполятора с другими устройствами средств отображения и регистрации графической информации.

Повышение надежности интерполятора обеспечивается за счет уменьшения количества связей между его элементами и блоками,

15

20

25

Формула изобретения

35 выход блока управления является первым -выходом интерполятора, второй выход блока управления соединен со счетным входом вычитающего счетчика и первым входом блока выходной логи40 ки, третий, выход блока управления соединен с входом переноса накапливающего сумматора, выход которого подключен к третьему входу блока управления, отличающийся

- уменьшения аппарат повышения надежности

ных затрат и повышения надежности интерполятора, в него введен блок памяти, управляющий и адресньй входы которого подключены соответс твенно к четвертому и пятому выходам блока

управления, а выходы - к информационным входам накапливающего сумматора, выход которого подключен к второму входу выходного блока логики,

а стробирующий вход соединен с шестым вьпсодом блока управления, у которого

входы с четвертого по седьмой являются соответственно с первого по четвертый входами интерполятора, при

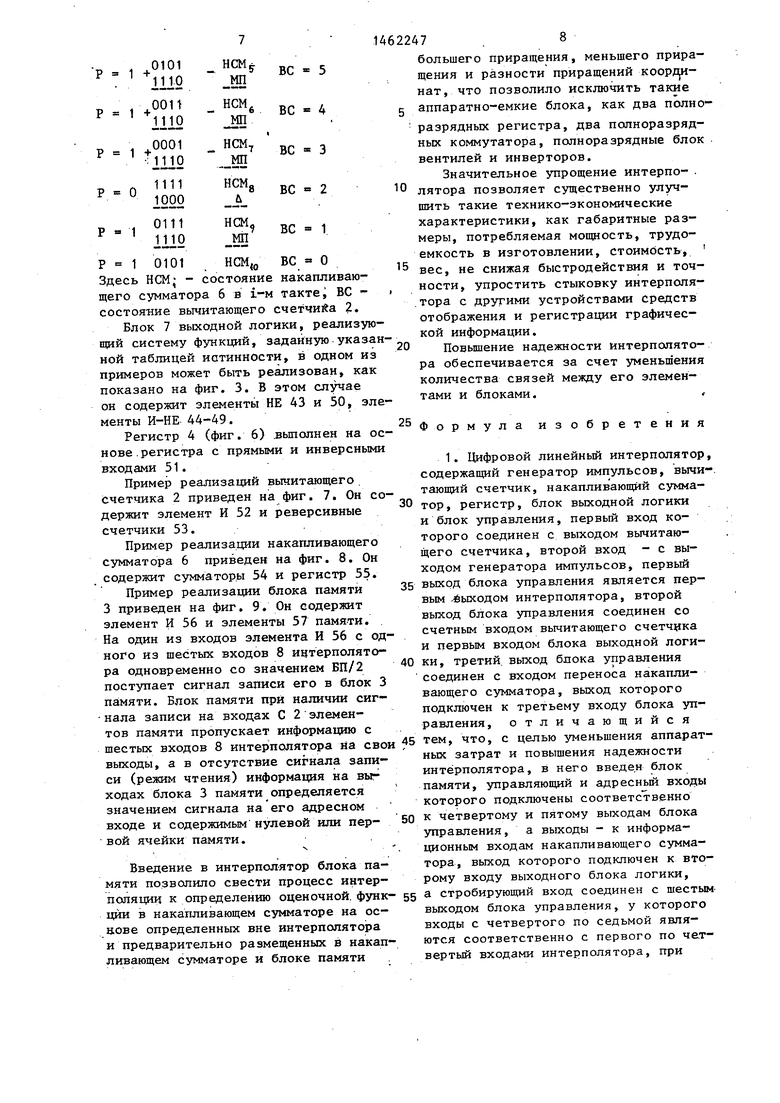

этом восьмой вход блока управления соединен со сбросовым входом накапливающего сумматора и управляющим входом регистра и является пятым входом интерполятора с первого по пятый выходы регистра соединены со- ;ответственно с третьего по седьмой v входами блока выходной логики, у которого выходы с первого по четвертый являются с второго по пятый выходами интерполятора, информационные входы вычитающего счетчика, блока памяти и регистра подключены к шестым входам интерполятора, а управляющий вход вычитающего счетчика является седьмым входом интерполятора.

ка управления, выход первого триггера подключен к первому входу третьего элемента И, второй вход которого соединен с выходом второго триггера и является третьим выходом блока управления, второй вход второго элемента И соединен с С-входом третьего триггера и является седьмым входом

блока управления, выход третьего триггера подключен к D-входу четвертого триггера и является первым выходом блока управления, выход элемента И-НЕ соединен с С-входом второго

триггера, первым входом четвертого элемента И и является вторым выходом блока управления, первый вход элемента И-НЕ подключен к выходу четвертого триггера, а второй вход к выходу элемента НЕ, вход которого соединен с С-входом четвертого триггера и я-вляется вторым входом блока управления, D-входы второго и третьего триггеров соединены с источ-

НИКОМ сигнала логической единицы, при этом D-вход второго триггера является третьим, а второй вход четвертого элемента И- четвертым входами блока управления, а выходы второго, третьего и четвертого элементов И .являются соответственно четвертым, пятым и шестым выходами бло-: ка управления..

., /7

.2

Фие. J

Фие.5

Фие.б

3

Фи.д

Фие.9

J

II

sl

i |

| Цифровой линейный интерполятор с оценочной функцией | 1981 |

|

SU991375A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровой линейный интерполятор | 1981 |

|

SU957171A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-02-28—Публикация

1987-03-10—Подача