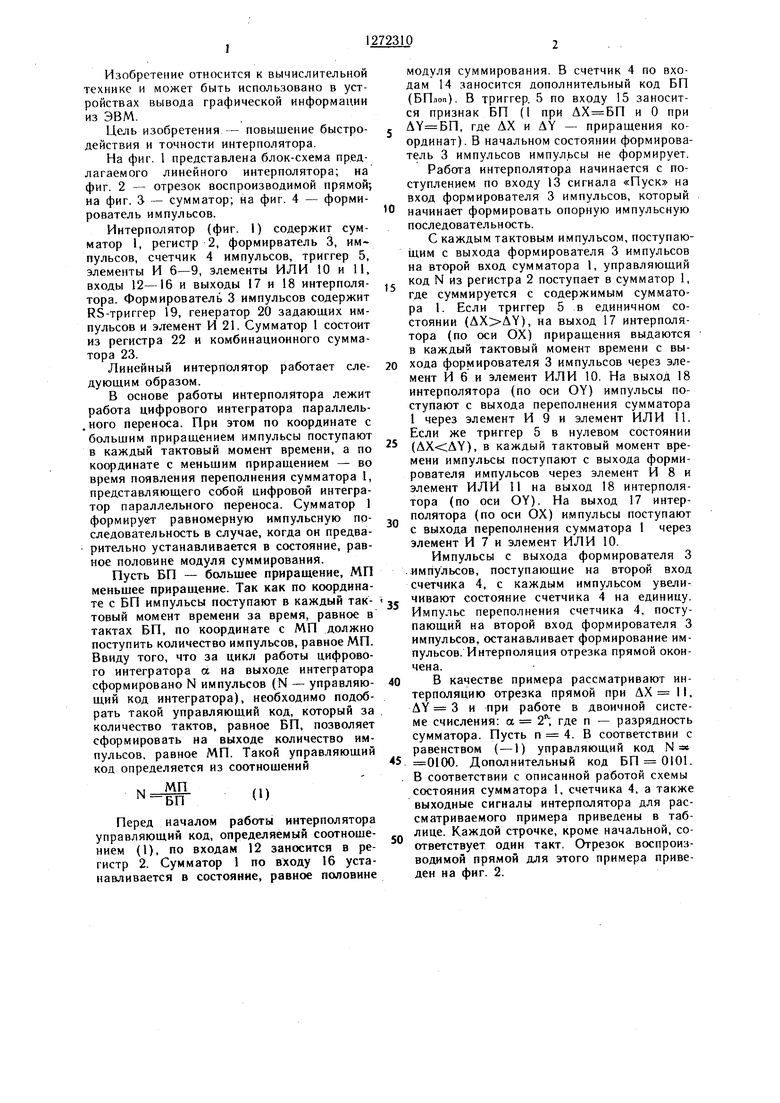

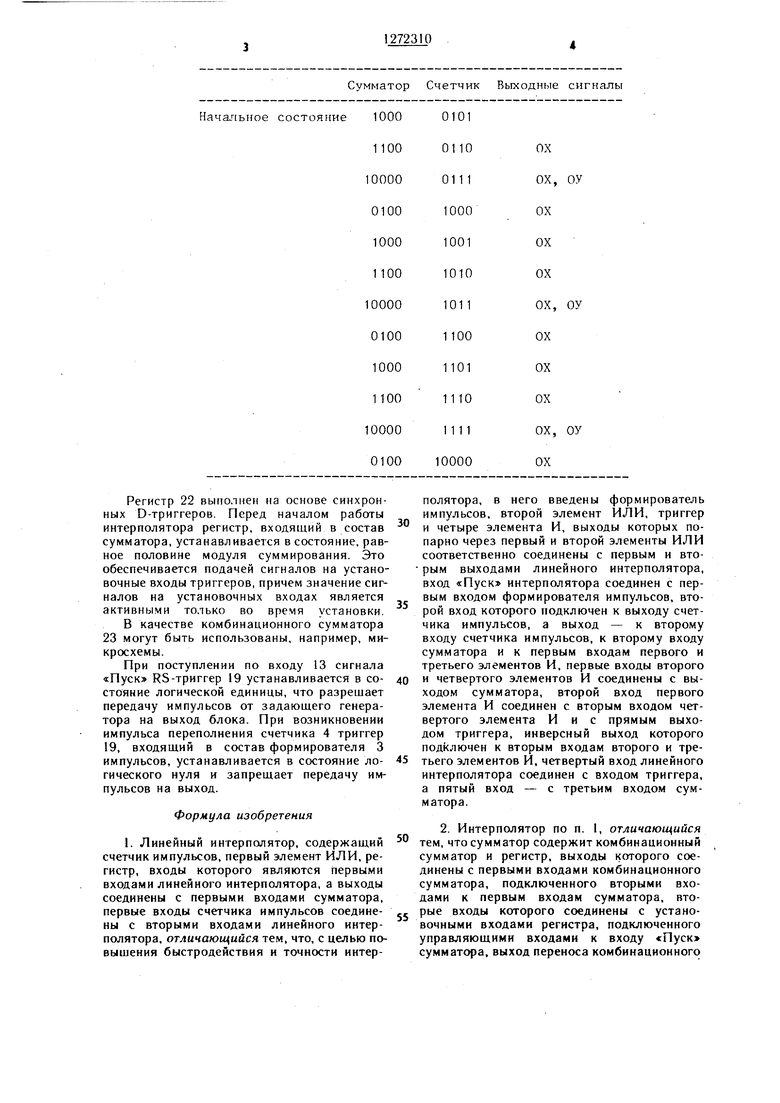

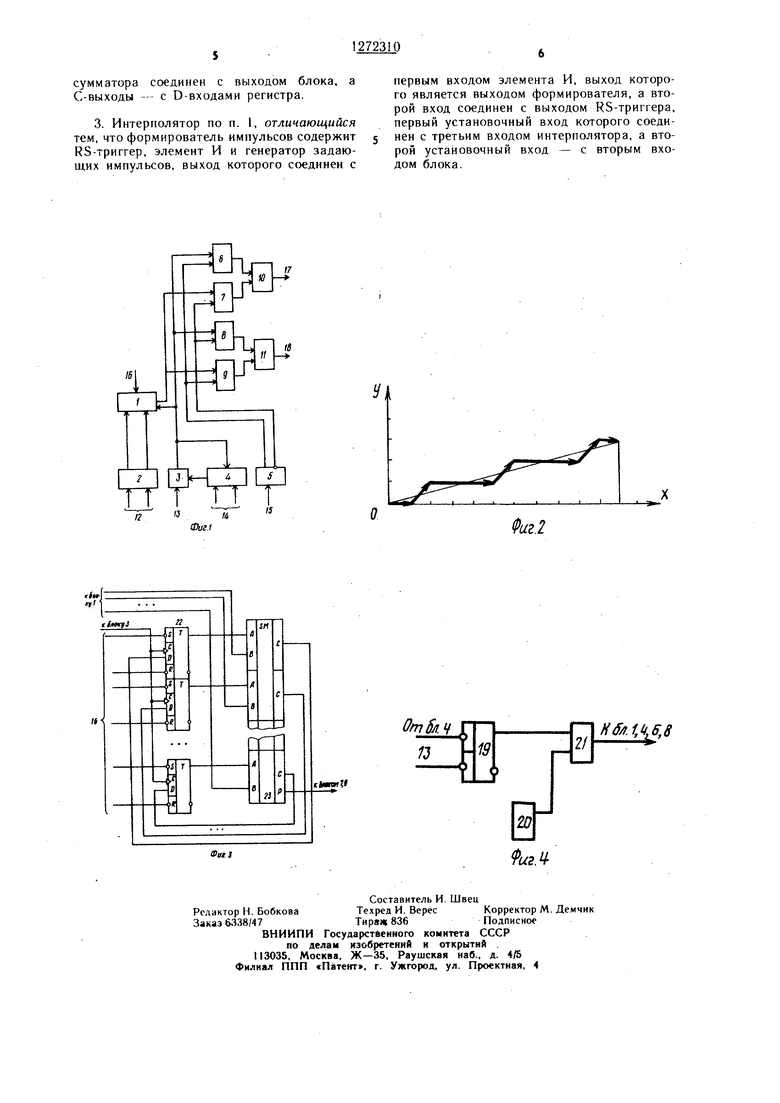

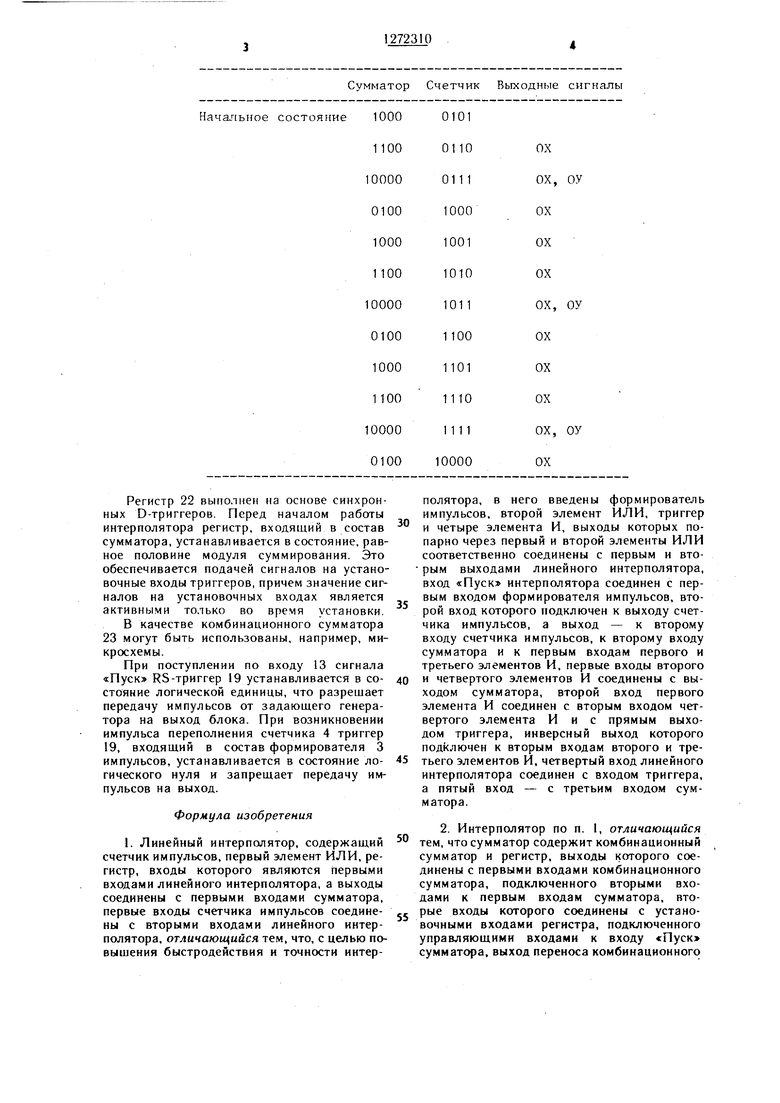

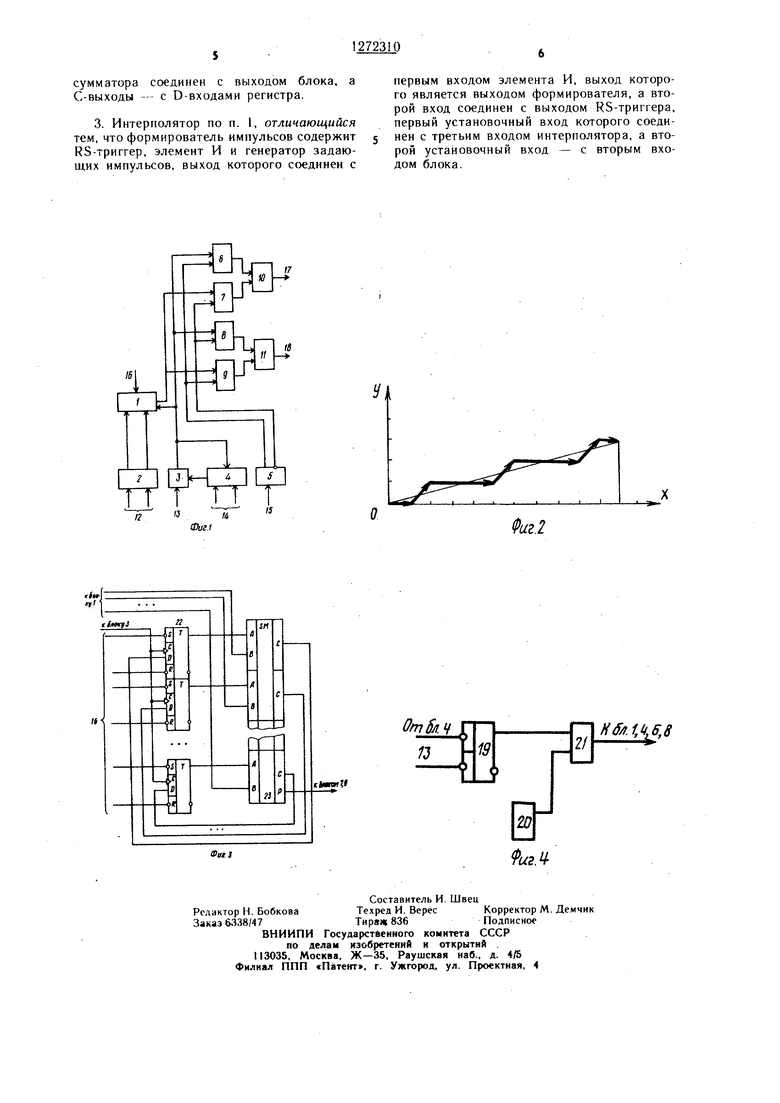

Изобретение относится к вычислительной технике и может быть использовано в устройствах вывода графической информации из ЭВМ. Цель изобретения - повышение быстродействия и точности интерполятора. На фиг. 1 представлена блок-схема предлагаемого линейного интерполятора; на фиг. 2 - отрезок воспроизводимой прямой; на фиг. J - сумматор; на фиг. 4 - формирователь импульсов. Интерполятор (фиг. I) содержит сумматор 1, регистр 2, формирватель 3, импульсов, счетчик 4 импульсов, триггер 5, элементы И 6-9, элементы ИЛИ 10 и II, входы 12-16 и выходы 17 и 18 интерполятора. Формирователь 3 импульсов содержит RS-триггер 19, генератор 20 задающих импульсов и элемент И 21. Сумматор 1 состоит из регистра 22 и комбинационного сумматора 23. Линейный интерполятор работает еледующим образом. В основе работы интерполятора лежит работа цифрового интегратора параллель. ного переноса. При этом по координате с больщим приращением импульсы поступают в каждый тактовый момент времени, а по координате с меньшим приращением - во время появления переполнения сумматора 1, представляющего собой цифровой интегратор параллельного переноса. Сумматор 1 формирует равномерную импульсную последовательность в случае, когда он предварительно устанавливается в состояние, равное половине модуля суммирования. Пусть БП - большее приращение, МП меньщее приращение. Так как по координате с БП импульсы поступают в каждый тактовый момент времени за время, равное в тактах БП, по координате с МП должно поступить количество импульсов, равное МП. Ввиду того, что за цикл работы цифрового интегратора а на выходе интегратора сформировано N импульсов (N - управляющий код интегратора), необходимо подобрать такой управляющий код, который за количество тактов, равное БП, позволяет сформировать на выходе количество импульсов, равное МП. Такой управляющий код определяется из соотнощений Перед началом работы интерполятора управляющий код, определяемый соотнощением (1), по входам 12 заносится в регистр 2. Сумматор 1 по входу 16 устанавливается в состояние, равное половине модуля суммирования. В счетчик 4 по входам 14 заносится дополнительный код БП (БПлоп). В триггер. 5 по входу 15 заносится признак БП (I при и О при , где ДХ и ДУ - приращения координат). В начальном состоянии формирователь 3 импульсов импульсы не формирует. Работа интерполятора начинается с поступлением по входу 13 сигнала «Пуск на вход формирователя 3 импульсов, который начинает формировать опорную импульсную последовательность. С каждым тактовым импульсом, поступаю1цим с выхода формирователя 3 импульсов на второй вход сумматора 1, управляющий код N из регистра 2 поступает в сумматор 1, где суммируется с содержимым сумматора 1. Если триггер 5 в единичном состоянии (), на выход 17 интерполятора (по оси ОХ) приращения выдаются в каждый тактовый момент времени с выхода формирователя 3 импульсов через элемент И 6 и элемент ИЛИ 10. На выход 18 интерполятора (по оси OY) импульсы поступают с выхода переполнения сумматора 1 через элемент И 9 и элемент ИЛИ 11. Если же триггер 5 в нулевом состоянии (), в каждый тактовый момент времени импульсы поступают с выхода формирователя импульсов через элемент И 8 и элемент ИЛИ 11 на выход 18 интерполятора (по оси OY). На выход 17 интерполятора (по оси ОХ) импульсы поступают с выхода переполнения сумматора 1 через элемент И 7 и элемент ИЛИ 10. Импульсы с выхода формирователя 3 импульсов, поступающие на второй вход счетчика 4, с каждым импульсом увеличивают состояние счетчика 4 на единицу. Импульс переполнения счетчика 4, поступающий на второй вход формирователя 3 импульсов, останавливает формирование импульсов. Интерполяция отрезка прямой окончена. В качестве примера рассматривают интерполяцию отрезка прямой при ДХ И, ДУ 3 и при работе в двоичной системе счисления: а 2 где п - разрядность сумматора. Пусть п 4. В соответствии с равенством (-1) управляющий код N 0100. Дополнительный код БП 0101. В соответствии с описанной работой схемы состояния сумматора 1, счетчика 4, а также выходные сигналы интерполятора для рассматриваемого примера приведены в таблице. Каждой строчке, кроме начальной, соответствует один такт. Отрезок воспроизводимой прямой для этого примера приведен на фиг. 2.

Сумматор Счетчик Выходные сигналы

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1989 |

|

SU1659986A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Цифровой линейный интерполятор | 1990 |

|

SU1805449A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Круговой интерполятор | 1985 |

|

SU1359772A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для коррекции положения резца на станке с программным управлением | 1981 |

|

SU983651A1 |

| Линейно-круговой интерполятор | 1985 |

|

SU1259218A1 |

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

Изобретение относится к области вы числительной техники и может быть исполь.зовано в устройствах вывода гра4)ической информации из ЭВМ. Целью изобретения является повышение быстродйствия и точное ти интерполятора. Интерполятор содержит .сумматор, регистр, формирователь импульсов, счетчик импульсов, триггер, элементы И и ИЛИ. При этом формирователь импульсов содержит RS-триггер, элемент И и задающий генератор. При этом сумматор выполнен как регистр и комбинационный сумматор. Начальная установка сумматора в состояние, равное половине модуля суммирования, позволяет повысить точность интерполяции в два раза, т.к. при выполнении раздельных шагов максимальная погрешность шага приближается к шагу дискретизации, а в данном случае - к половине шага. Замена двух раздельных шагов одним совмещенным приводит к повышению быстродействия интерполятора. Т.к. количество совмещенных шагов равно малому приращению (МП), то уменьшение времени интерполяции составляет величину МП - At. Применение такого интерполятора наряду с простотой реализации позволяет повысить быстро о действие устройств вывода графической информации из ЭВМ, повысить качество вос(Л производимых отрезков или сократить разрядность устройств обработки графической информации с сохранением той же точности. 2 з.п. ф-лы, 4 ил. 1 табл. ьо 1C 00

Регистр 22 выполнен на основе синхронных D-триггеров. Перед началом работы интерполятора регистр, входящий в состав сумматора, устанавливается в состояние, равное половине модуля суммирования. Это обеспечивается подачей сигналов на установочные входы триггеров, причем значение сигналов на установочных входах является активными только во время установки. В качестве комбинационного сумматора 23 могут быть использованы, например, микросхемы. При поступлении по входу 13 сигнала «Пуск RS-триггер 19 устанавливается в состояние логической единицы, что разрешает передачу импульсов от задающего генератора на выход блока. При возникновении импульса переполнения счетчика 4 триггер 19, входящий в состав формирователя 3 импульсов, устанавливается в состояние логического нуля и запрещает передачу импульсов на выход. Формула изобретения . Линейный интерполятор, содержащий счетчик импульсов, первый элемент ИЛИ, регистр, входы которого являются первыми входами линейного интерполятора, а выходы соединены с первыми входами сумматора, первые входы счетчика импульсов соединены с вторыми входами линейного интерполятора, отличающийся тем, что, с целью повышения быстродействия и точности интерполятора, в него введены формирователь импульсов, второй элемент ИЛИ, триггер и четыре элемента И, выходы которых попарно через первый и второй элементы ИЛИ соответственно соединены с первым и вторым выходами линейного интерполятора, вход «Пуск интерполятора соединен с первым входом формирователя импульсов, второй вход которого подключен к выходу счетчика импульсов, а выход - к второму входу счетчика импульсов, к второму входу сумматора и к первым входам первого и третьего элементов И, первые входы второго и четвертого элементов И соединены с выходом сумматора, второй вход первого элемента И соединен с вторым входом четвертого элемента И и с прямым выходом триггера, инверсный выход которого подключен к вторым входам второго и третьего элементов И, четвертый вход линейного интерполятора соединен с входом триггера, а пятый вход - с третьим входом сумматора. 2. Интерполятор по п. 1, отличающийся тем, что сумматор содержит комбинационный сумматор и регистр, выходы которого соединены с первыми входами комбинационного сумматора, подключенного вторыми входами к первым входам сумматора, вторые входы которого соединены с установочными входами регистра, подключенного управляющими входами к входу «Пуск сумматора, выход переноса комбинационного

сумматора соединен с выходом блока, а С-выходы - с D-входами регистра.

первым входом элемента И, выход которого является выходом формирователя, а второй вход соединен с выходом RS-триггера, первый установочный вход которого соединен с третьим входом интерполятора, а второй установочный вход - с вторым входом блока.

| Линейный интерполятор | 1980 |

|

SU920636A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| 0 |

|

SU377822A1 | |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-23—Публикация

1985-04-29—Подача