. „.-.,™. .«. .,

ШГ

||Щ«

z

Фь

СлЭ О5

00

1чЭ

TZGn:

Изобретение относится к вычисли- , ельной технике и может быть использовано в устройствах диагностироваия и статистической обработки ин- с ормации.

Цель изобретения - повышение быстродействия регистра сдвига.

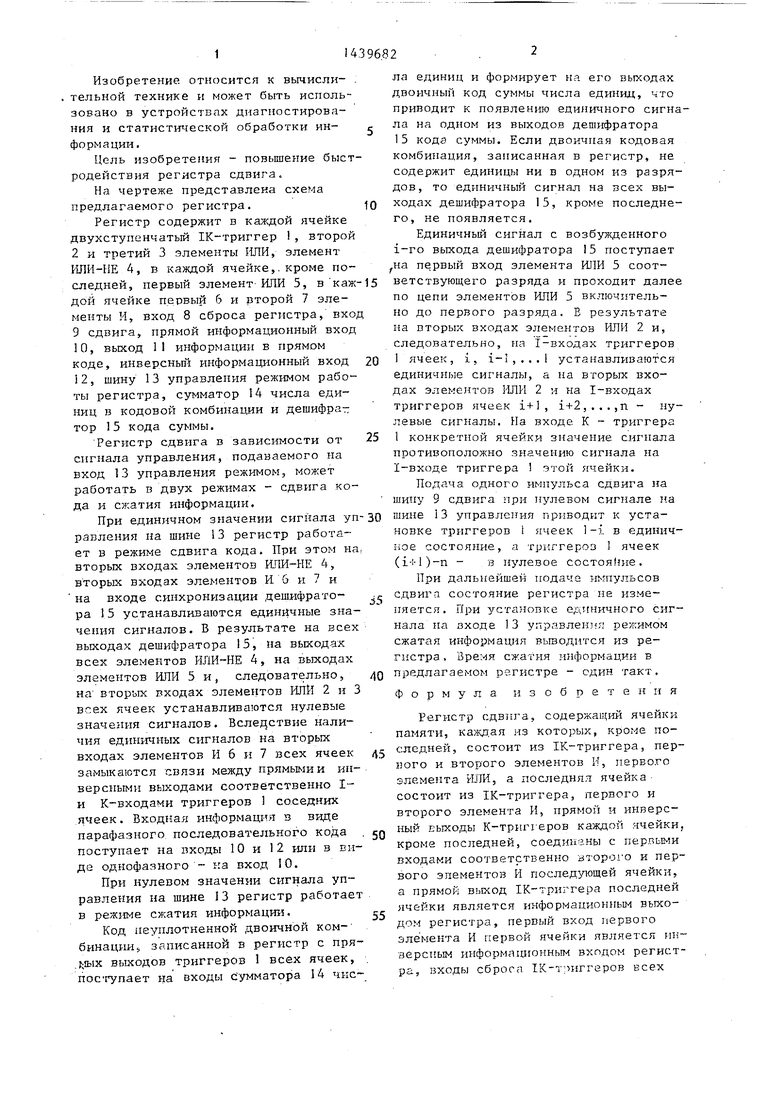

На чертеже представлена схема предлагаемого регистра,tO

Регистр содержит в каждой ячейке вухступенчатьм 1К-триггер 1, второй 2 и третий 3 элементы ИЛИ, элемент ПИ-ЫЕ 4, в каждой ячейке,, кроме последней, первый элемент-ИЛИ 5, в каж-15 ои ячейке первый 6 и второй 7 элеенты И, вход 8 сброса регистра, вход 9 сдвига, прямой информационный вход 10, выход 11 информации в прямом оде, инверсньш информационный вход 20 12, шину 13 управления режимом работы регистра, сумматор 14 числа единиц в кодовой комбинации и дешифратор 15 кода суммы.

Регистр сдвига в зависимости от 25 сигнала управления, подаваемого на вход 13 управления режимом, может работать в двух режимах - сдвига коа и сжатия информации.

При единичном значении сигнала уп- 30 равления на шине 3 регистр работает в режиме сдвига кода. При этом на; вторых входах элементов ИЛИ-НЕ 4, вторых входах элементов И 6 и 7 и на входе синхронизации дешифрато- ( ра 15 устанавливаются единичные значения сигналов. В результате на всех выходах дешифратора 15, на вькодах всех элементов ИЛИ-НЕ 4, на выходах элементов ИЛИ 5 и, следовательно, 40 на вторых входах элементов ИЛИ 2 и 3 всех ячеек устанавливаются нулевые значения сигналов. Вследствие наличия единргчных сигналов на вторых входах элементов И 6 и 7 всех ячеек 45 замыкаются связи между прямыми и инверсными выходами соответственно I- и К-входами триггеров 1 соседних ячеек. Входная информация в виде парафазного, последовательного кода . gQ поступает на входы 10 и 12 или з виде однофазного - на вход 10.

При нулевом значении сигнала управления на шине 13 регистр работает в режиме сжатия информации. 55

Код пеуплотненной двоичной ком- бинации., записанной в регистр с пря- выходов триггеров 1 всех ячеек, . поступает на входы С умматора 14 числа единиц и формирует на его выходах двоичный код суммы числа единид, что приводит к появлению единичного сигнла на одном из выходов дешифратора 15 кода суммы. Если двоичная кодовая комбинация, занисанная в регистр, не содержит единицы ни в одном из разрядов, то единичный сигнал на зсех выходах дешифратора 15, кроме последнего, не появляется.

Единичный сигнал с возбужденного i-ro выхода дешифратора 15 поступает на первый вход элемента ИЛИ 5 соответствующего разряда и проходит дале по цепи элементов ИЛИ 5 включительно до первого разряда. В результате на вторых входах элементов ИЛИ 2 и, следовательно, на 1-входах триггеров 1 ячеек, i, i-l,..,I устанавливаются единичные сигналы, а на вторых входах элементов ИЛИ 2 и на 1-входах триггеров ячеек i+1, i+2,..,,n - нулевые сигналы. На входе К - триггера 1 конкретной ячейки значение сигнала противоположно значению сигнала на 1-входе триггера 1 этой ячейки.

Лодача одного импульса сдвига на шипу 9 сдвига при нулевом сигнале на шине 13 управления ГФНБОДИТ к установке триггеров 1 ячеек 1-i в единич- 1юе состояние, а тркггероа 1 ячеек ()-n - В нулевое состояние.

При дальнейшей подаче г1 ;пульсов сдвига состояние регистра не изменяется. При установке ед лничного сигнала на входе 13 управления регкимом сжатая информация вьтодится из регистра , Bpe:-iH сжатия информации в предлагаемом регистре - един такт.

Формула изобретения

Регистр сдв ига, содержащий ячейки памяти, кажд.ая из которых, кроме последней, состоит из 1К-триггера, первого и второго элементов И, первого элемента ИЛИ, а последняя ячейка состоит из 1К-триггера, первого и второго элемента И, прямой и инверсный выходы К-триггеров каждой ячейки кроме последней, соедиианы с первыми входами соответственно второго и первого элементов И последующей ячейки, а прямой выход 1К-триггера последней ячейки является информационным выходом регистра, первый вход первого элемента И первой ячейки является nii верспым информационным входом регистра, входы сброса 1К-т: иггеров всех

ячеек соединены и являются входом сброса регистра, тактовые входы IK- триггеров всех ячеек соединены и являются входом сдвига регистра, первый вход первого элемента ИГГИ каждой ячейки, кроме предпоследней, соединен с выходом первого элемента ИЛИ последующей ячейки, отличаюийся тем, что, с целью повыше- ю НИН быстродействия регистра, он соержит сумматор, дешифратор, а в

каждой ячейке,кроме последней,второй и третий элементы 11Ш и элемент ИЛИ-КЕ, а последняя ячейка содержит первый 45 и второй элемент ИЛИ и элемент ИЛИ-НЕ,

причем выходы первого и второго элементов ИЛИ последней ячейки и выходы второго и третьего элементов 11ЛИ остальных ячеек соединены соответст- 20 веннос I- и К-входами 1К-триггеров, первые входы - соответственно с выходами второго и первого элементов И, а вторые входы - соответственно с первым входом и выходом элемента 25

ИЛИ-НЕ, первый вход которого в каждой ячейке, кроме последней, соединен с выходом первого элемента ЦЛИ, а второй вход соединен с вторыми входами первого и второго элементов И, первый вход второго элемента И первой ячейки является прямым информационным входом регистра, вторые входы элементов ИЛИ-НЕ всех ячеек объединены и являются входом управления режимом работы регистра, прямые выходы IK-триггеров всех ячеек соединены с соответствующими входами слагаемых сумматора, выходы которых соединены с соответствующими информационными входами дешифратора,вход стробирования которого соединен с вторыми входами элементов 1ШИ-НБ всех ячеек, а выходы дешифратора - соответственно с вторыми входами первых элементов ИЛИ всех ячеек, первым входом элемента последней ячейки и первым входом элемента ИЛИ предпоследней ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| Адаптивный коммутатор телеизмерительной системы | 1990 |

|

SU1785020A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для сортировки чисел | 1984 |

|

SU1223221A1 |

| Устройство для программного управления захватом автооператора | 1982 |

|

SU1233103A1 |

| Устройство для отображения информации | 1987 |

|

SU1437909A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для сжатия и накопления графической информации | 1983 |

|

SU1164763A2 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

Изобретение относится к вычислительной технике и моясет Сыть испол;....- зовано в устройствах ггиагног.тировання и статист.1ческо11 обработки информации. Цель из 1боет ения - повышение быстродействия регистра. Поставленная цель достигается тем, что регистр содержит вторые 2 и третьи 3 элементы ИЛИ, элет.енты 1-ШИ-НЕ 4, сум- матер 14 и дешифратор 15 с соответ- ствллащими связями. В режиме сжатия информаци.я поступает с выходов триггеров 1 iid сумхгтор 14, который суммирует число единиц в регистре. Вычисленное количество.единиц вновь записывается в регистр ири поступлении тактового сигнала, 3 резу.пьтате сжатие информации производится за один такт. 1 ил.ю

| УСТРОЙСТВО ОРГАНОВ СТАБИЛИЗАЦИИ И УПРАВЛЕНИЯ В АЭРОПЛАНАХ, СНАБЖЕННЫХ НЕСКОЛЬКИМИ РЯДОМ УСТАНОВЛЕННЫМИ МОТОРАМИ | 1924 |

|

SU1049A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Регистр сдвига | 1984 |

|

SU1179435A2 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1988-11-23—Публикация

1987-04-07—Подача