Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении вычислительных систем на основе общей магистрали при необходимости организации надежной работы синхронизации нескольких одновременно работающих модулей.

. Целью изобретения является повышение помехоустойчивости устройства при одновременной работе нескольких модулей вычислительной системы.

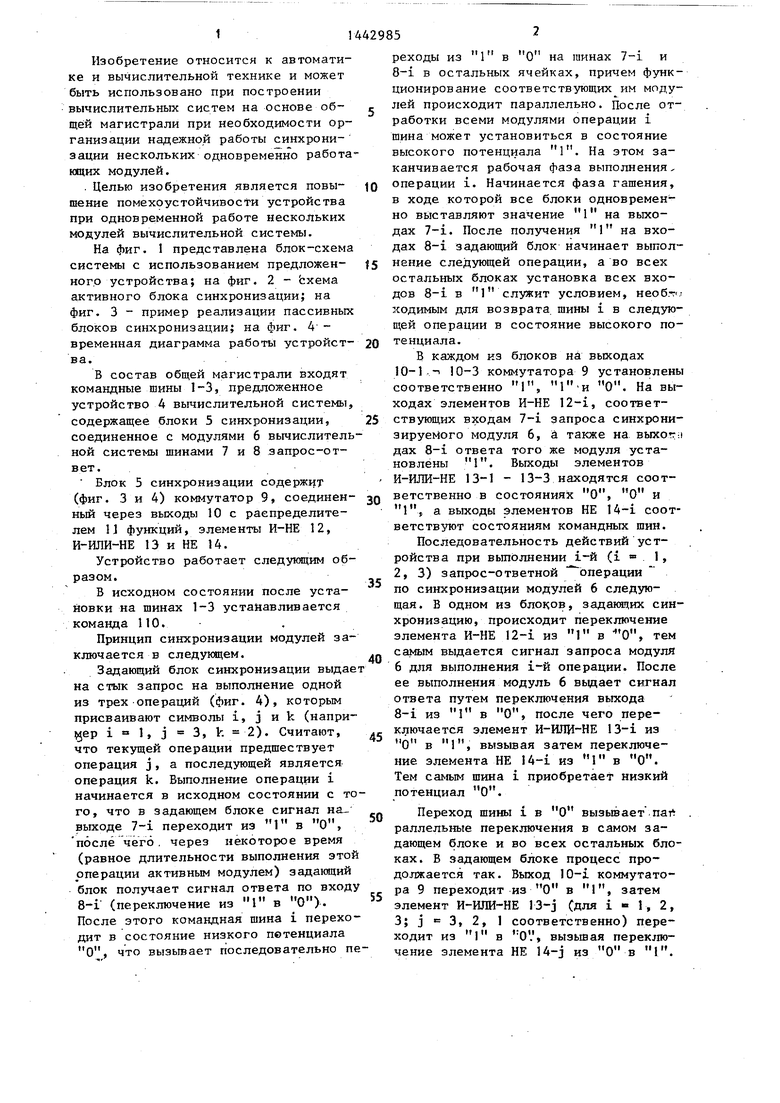

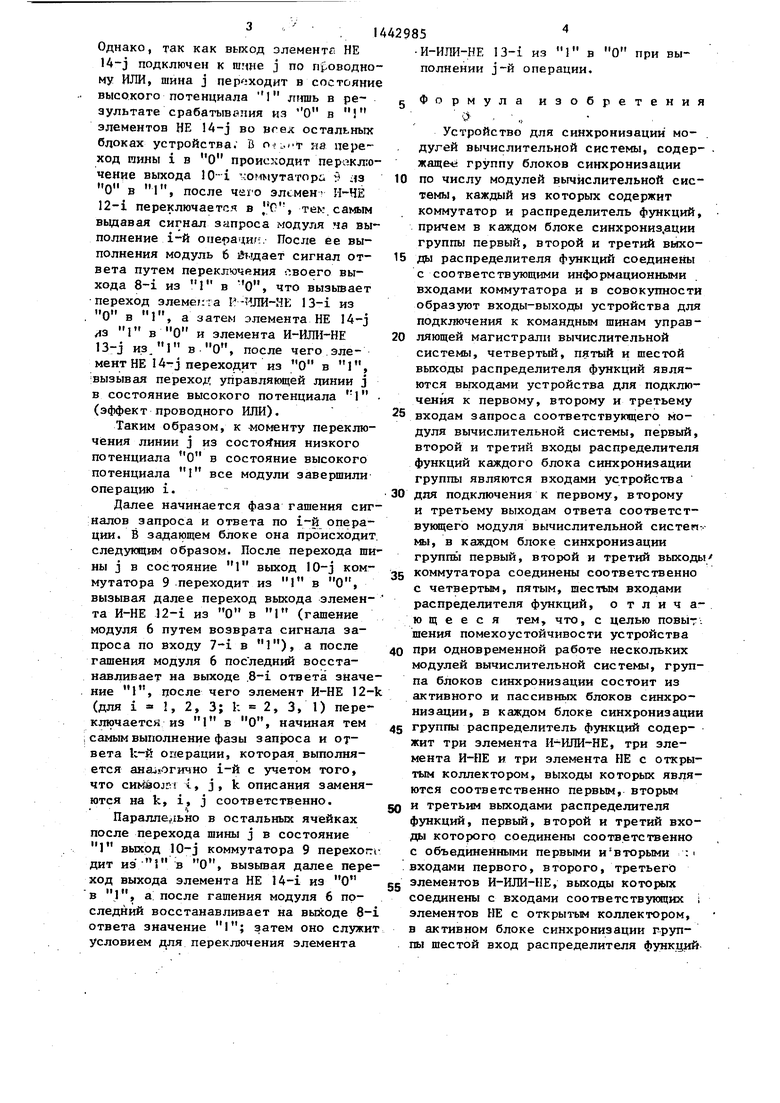

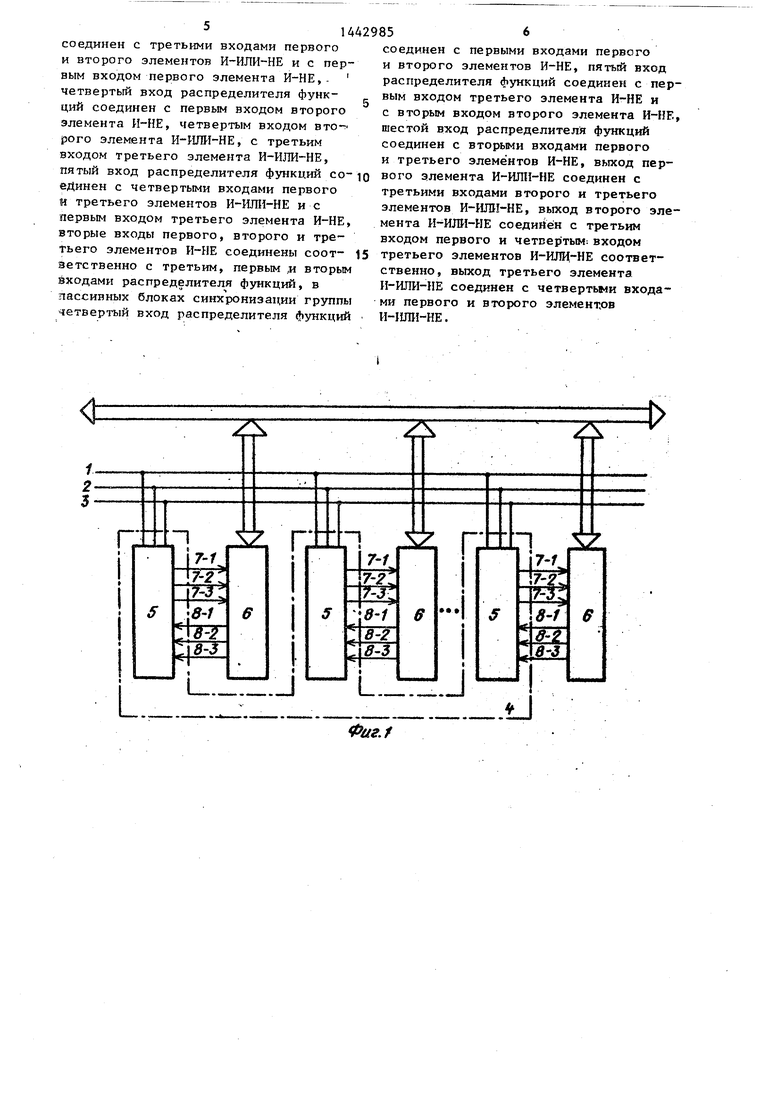

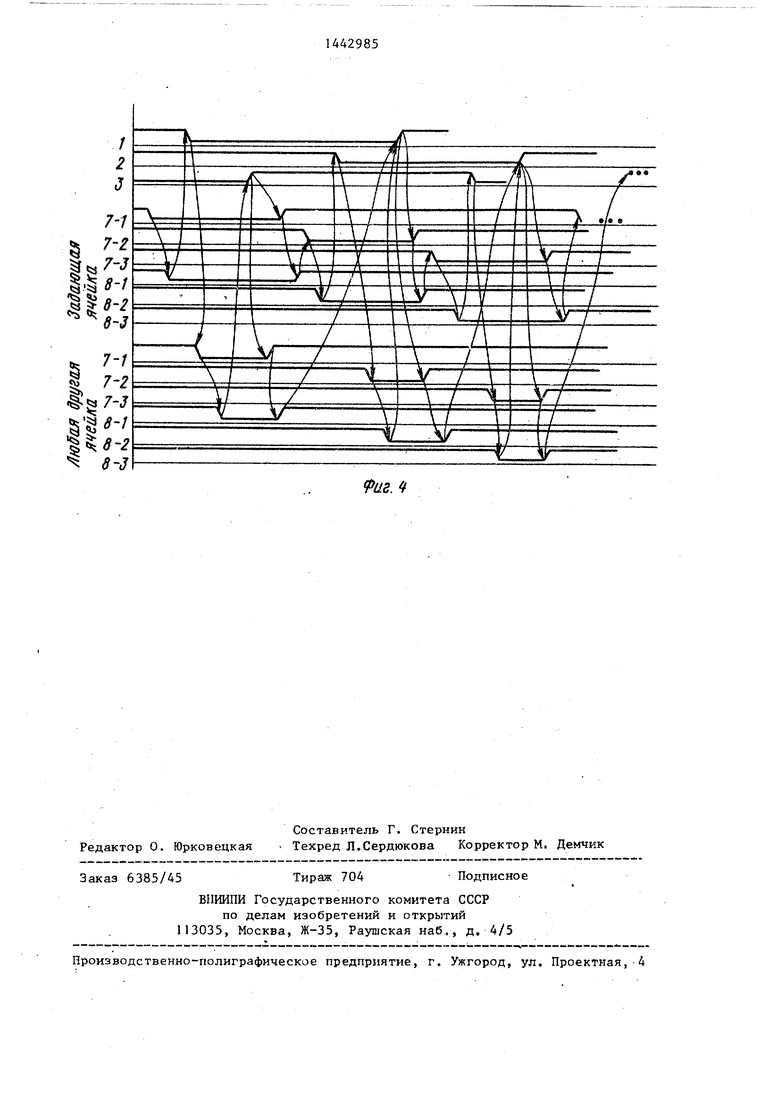

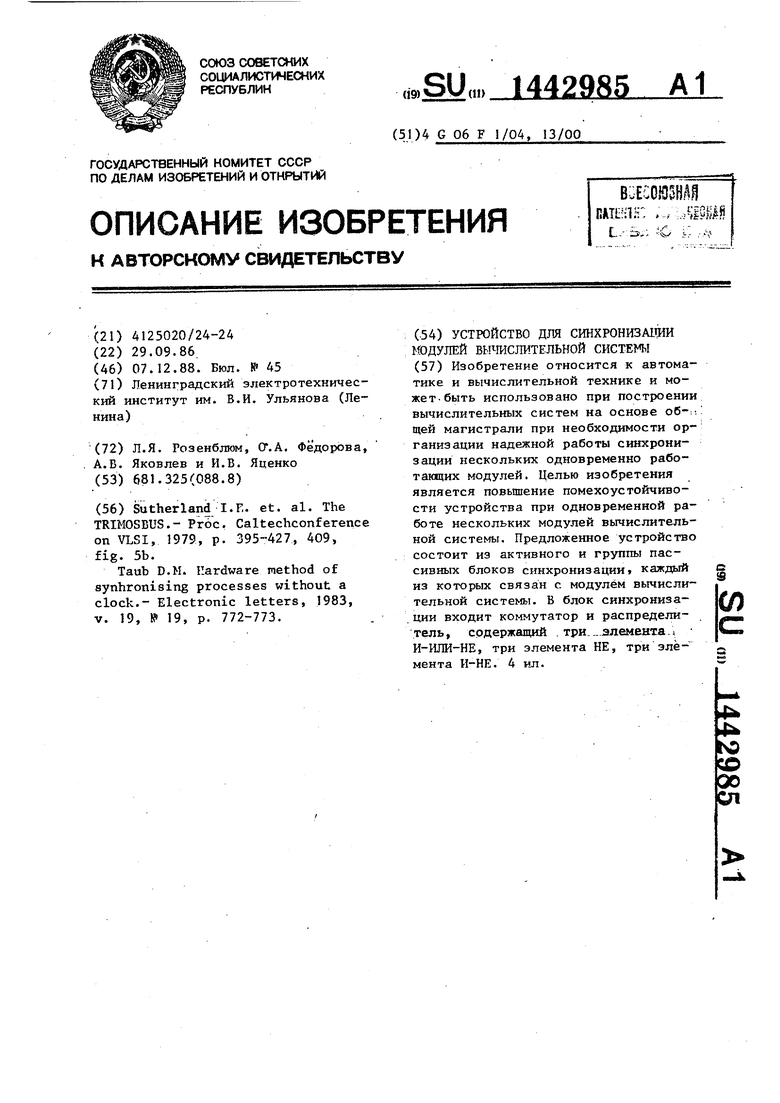

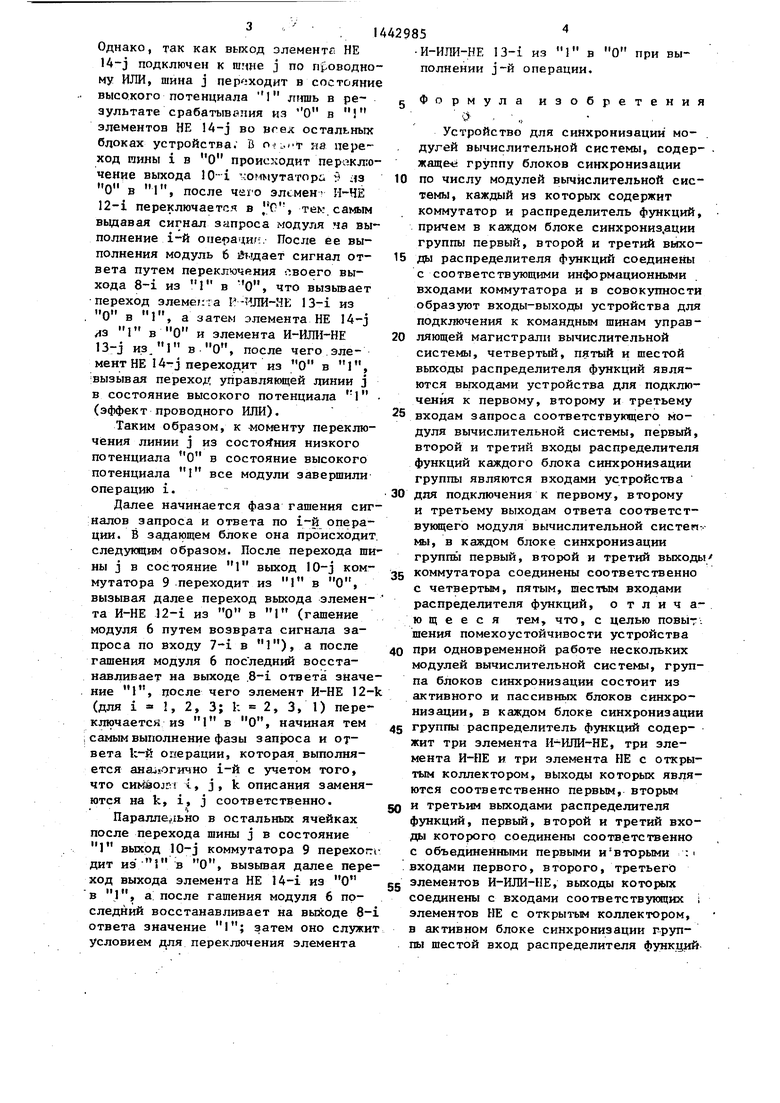

На фиг. 1 представлена блок-схема системы с использованием предложенного устройства; на фиг. 2 - Ьхема активного блока синхронизации; на фиг. 3 - пример реализации пассивных блоков синхронизации; на фиг. 4- временная диаграмма работы устройства.

В состав общей магистрали входят командные шины 1-3, предложенное устройство А вычислительной системы, содержащее блоки 5 синхронизации, соединенное с модулями 6 вычислительной системы шинами 7 и 8 запрос-ответ.

Блок 5 синхронизации содержит (фиг. 3 и 4) коммутатор 9, соединен- ньй через выходы 10 с распределителем П функций, элементы И-НЕ 12, И-ИЛИ-НЕ 13 и НЕ 14.

Устройство работает следующим образом.

В исходном состоянии после установки на шинах 1-3 устанавливается команда 110.

Принцип синхронизации модулей заключается в следукщем.

Задающий блок синхронизации выдае на стык запрос на выполнение одной из трех операций (фиг. 4), которым присваивают символы i, j и k (напри- ер i 1, j 3, k 2). Считают, что текущей операции предшествует операция j, а последующей является- операция k. Выполнение операции i начинается в исходном состоянии с того, что в задающем блоке сигнал выходе 7-i переходит из 1 в О, после чего , через некоторое время (равное длительности выполнения этой операции активным модулем) задающий блок получает сигнал ответа по входу 8-1 (переключение из 1 в О). После этого командная шина i переходит в состояние низкого потенциала О, что вызьшает последовательно пе

реходы из 1 в О на гаинах 7-i и 8-1 в остальных ячейках, причем функционирование соответствующих им модулей происходит параллельно. После отработки всеми модулями операции i шина может установиться в состояние высокого потенциала 1. На этом заканчивается рабочая фаза выполнения, операции i. Начинается фаза гашения, в ходе которой все блоки одновременно выставляют значение 1 на выходах 7-i. После получения 1 на входах 8-i задающий блок начинает выполнение следующей операции, а во всех остальных блоках установка всех входов 8-i- в 1 служит условием, необ.г-; ходимым для возврата шины i в следующей операции в состояние высокого потенциала.

В каждом из блоков на выходах 10-1-1 10-3 коммутатора 9 установлены

соответственно 1

Г И О. На вы5

0

5

0

5

0

5

ходах элементов И-НЕ 12-i, соответствующих входам 7-i запроса синхронизируемого модуля 6, а также на вьпсогг: дах 8-1 ответа того же модуля установлены 1. Выходы элементов И-ИЛИ-НЕ 13-1 - 13-3 находятся соответственно в состояниях о, о и 1, а выходы элементов НЕ 14-i соответствуют состояниям командных шин. Последовательность действий устройства при вьшолнении i-й (1 I , 2, 3) запрос-ответной операции по синхронизации модулей 6 следующая. В одном из блоков, задаклдих синхронизацию, происходит переключение элемента И-НЕ 12-i из 1 в О, тем самым выдается сигнал запроса модуля 6 для выполнения i-й операции. После ее выполнения модуль 6 вьдает сигнал ответа путем переключения выхода 8-i из 1 в О, после чего переключается элемент И-ИЩ-НЕ 13-i из О в 1, вызывая затем переключение элемента НЕ 14-i из I в О. Тем самым Ш1ша i приобретает низкий потенциал О.

Переход шины i в О вызывает пат раллельные переключения в самом задающем блоке и во всех остальных блоках. В задающем блоке процесс продолжается так. Выход 10-i коммутатора 9 переходит из О в 1, затем элемент И-ИЛИ-НЕ 13-j (Для i 1, 2, 3j j 3, 2, 1 соответственно) переходит из 1 в О ., вызьшая переключение элемента НЕ 14-j из О в 1.

. 1442985

Однако, так как выход элементг. НЕ-И-ИЛИ-НЕ 13-1 из 1 в О при вы14-J подключен к шине j по проводно-полнении j-й операции,

му ИЛИ, шина j пер ходит в состояние высокого потенциала 1

лишь в результате срабатывания из О в элементов НЕ 14-j во вгех остальных блоках устройства. В на переход ИННЫ i в О проискодит переключение выхода ::оммутатор. 9 лз О а 1, после чего элсмен Н-ЧЕ 12-i переключается в | Г, тек самым вьщавая сигнал запроса модуля на выполнение i-й опе эаадг-:. После ее выполнения модуль 6 1 |адает сигнал ответа путем переключения своего выхода 8-i из в О, что вызывает переход элемекта И-ИЛИ-НЕ 13-i из

, О в 1, а затем элемента НЕ 14-j лз 1 в О и элемента И-ИЛИ-НЕ 13-J из. 1 в О, после чего элемент НЕ 14-j переходит из О в 1, :вызывая переход управляющей линии j в состояние высокого потенциала (эффект проводного ИЛИ).

Таким образом, к моменту переключения линии j из состояния низкого потенциала О в состояние высокого потенциала 1 все модули завершили операцию i.

Далее начинается фаза гашения сиг- ;налов запроса и ответа по i-й операции. В задающем блоке она происходит, следующим образом. После перехода шины j в состояние 1 выход 10-j коммутатора 9 переходит из 1 в О, вызывая далее переход выхода элемен- та И-НЕ 12-i из О в 1 (гашение модуля 6 путем возврата сигнала запроса по входу 7-i в 1), а после гашения модуля 6 последний восстанавливает на выходе ,8-i ответа значение I, после чего элемент И-НЕ 12-k (для i , 2, 3; 1: 2, 3, 1) переключается из 1 в о, начиная тем

; самым выполнение фазы запроса и ответа k-й операции, которая выполняется ана; огично i-й с учетом того, что cHKiBojEi i, j, k описания заменяются на k, i, j соответственно.

Параллельно в остальных ячейках после перехода шины j в состояние 1 выход 10-j коммутатора 9 перехогтг дит из 5 в О, вызьюая далее переход выхода элемента НЕ 14-i из О

в М, а после гашения модуля 6 последний восстанавливает на выходе 8-i ответа значение затем оно служит условием для переключения элемента

5 формула изобретени

О - „

Устройство для синхронизации мо- дугей вычислительной системы, содер жаще группу блоков синхронизации

10 по числу модулей вычислительной сис темы, каждый из которых содержит коммутатор и распределитель функций причем в каждом блоке синхрониз.ации группы первый, второй и третий выхо

15 ды распределителя функций соединены с соответствующими информационными входами коммутатора и в совокупност образуют входы-выходы устройства дл подключения к командным шинам управ

20 ляющей магистрали вычислительной системы, четвертый, пятый и шестой выходы распределителя функций являются выходами устройства для подклю чения к первому, второму и третьему

25 входам запроса соответствующего модуля вычислительной системы, первый второй и третий входы распределител функций каждого блока синхронизации группы являются входами устройства

30 для подключения к первому, второму и третьему выходам ответа соответст вукицего модуля вычислительной систе M)j, в каждом блоке синхронизации группь первый, второй и третий выхо

35 коммутатора соединены соответственн с четвертым, пятым, шестым входами распределителя функций, отлич ющееся тем, что, с целью повы шения помехоустойчивости устройства

40 при одновременной работе нескольких модулей вычислительной системы, гру па блоков синхронизации состоит из активного и пассивных блоков синхро низации, в каждом блоке синхронизац

45 группы распределитель функций содер жит три элемента И-ИЛИ-НЕ, три элемента И-НЕ и три элемента НЕ с откры тым коллектором, выходы которых явля ются соответственно первым, вторым

50 и третьим выходами распределителя

функций, первый, второй и третий вхо ды которого соединены соответственно с объединенными первыми и вторыми : входами первого, второго, третьего

55 элементов И-ИЛИ-НЕ, выходы KOTOI IX соединены с входами соответствующих элементов НЕ с открытьм коллектором, в активном блоке синхронизации группы шестой вход распределителя функци

5 формула изобретения

О - „

Устройство для синхронизации мо- дугей вычислительной системы, содер- . жаще группу блоков синхронизации

0 по числу модулей вычислительной системы, каждый из которых содержит коммутатор и распределитель функций, причем в каждом блоке синхрониз.ации группы первый, второй и третий выхо5 ды распределителя функций соединены с соответствующими информационными входами коммутатора и в совокупности образуют входы-выходы устройства для подключения к командным шинам управ0 ляющей магистрали вычислительной системы, четвертый, пятый и шестой выходы распределителя функций являются выходами устройства для подключения к первому, второму и третьему

5 входам запроса соответствующего модуля вычислительной системы, первый, второй и третий входы распределителя функций каждого блока синхронизации группы являются входами устройства

0 для подключения к первому, второму и третьему выходам ответа соответст- вукицего модуля вычислительной систеп-.- M)j, в каждом блоке синхронизации группь первый, второй и третий выходы/

5 коммутатора соединены соответственно с четвертым, пятым, шестым входами распределителя функций, отличающееся тем, что, с целью повыт- шения помехоустойчивости устройства

0 при одновременной работе нескольких модулей вычислительной системы, группа блоков синхронизации состоит из активного и пассивных блоков синхронизации, в каждом блоке синхронизации

5 группы распределитель функций содержит три элемента И-ИЛИ-НЕ, три элемента И-НЕ и три элемента НЕ с открытым коллектором, выходы которых являются соответственно первым, вторым

0 и третьим выходами распределителя

функций, первый, второй и третий входы которого соединены соответственно с объединенными первыми и вторыми : входами первого, второго, третьего

5 элементов И-ИЛИ-НЕ, выходы KOTOI IX соединены с входами соответствующих i элементов НЕ с открытьм коллектором, в активном блоке синхронизации группы шестой вход распределителя функций

соединен с третьими входами первого и второго элементов И-ИЛИ-НЕ и с первым входом первого элемента И-НЕ,- четвертый вход распределителя функций соединен с первым входом второго элемента И-ИЕ, четвертым входом в то- рого элемента И-ИЛИ-НЕ, с третьим входом третьего элемента И-ИЛИ-НЕ,

пятый вход распределителя функций со- ю вого элемента И-ИЛИ-НЕ соединен с

соединен с первыми входами первого и второго элементов И-НЕ, пятый вход распределителя функций соединен с первым входом третьего элемента И-НЕ и с вторым входом второго элемента И-НЕ, шестой вход распределител;я функций соединен с вторыми входами первого и третьего элементов И-НЕ, выход пер

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство обмена данными распределенной управляющей системы | 1990 |

|

SU1718226A1 |

| Устройство для последовательного деления | 1986 |

|

SU1304017A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297051A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения двух вычислитель-НыХ МАшиН | 1979 |

|

SU805296A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

Изобретение относится к автоматике и вычислительной технике и может- быть использовано при построении вычислительных систем на основе об-:-. щей магистрали при необходимости организации надежной работы синхронизации нескольких одновременно работающих модулей. Целью изобретения является повьшение помехоустойчивости устройства при одновременной работе нескольких модулей вычислительной системы. Предложенное устройство состоит из активного и группы пассивных блоков синхронизации, каждый из которых связан с модулем вычислительной системы. В блок синхронизации входит коммутатор и распреде-пи гель, содержащий . три....алемента-1 И-ИЛИ-НЕ, три элемента НЕ, три элемента И-НЕ. 4 ил. (Л С

единен с четвертыми входами первого И третьего элементов И-ИЛИ-НЕ и с первым входом третьего элемента И-НЕ, вторые входы первого, второго и третьего элементов И-НЕ соединены соот- 15 зетственно с третьим, первым ,и вторым входами распределителя функций, в пассивных блоках синхронизации группы четвертый вход распределителя функций

третьими входами второго и третьего элементов И-ИЛИ-НЕ, выход второго элемента И-ИЛИ-НЕ соединён с третьим входом первого и четвертым входом третьего элементов И-ИЛИ-НЕ соответственно, выход третьего элемента И-РШИ-НЕ соединен с четвертыми входами первого и второго элементов И-ИЛИ-НЕ.

Фаг./

/

2

J

7-1

7-3

|.§ 8-J

8-3

7-1 I 7-2 §g7-J

8-3

Составитель Г. Стернин Редакторе. Юрковецкая Техред Л.Сердюкова Корректор М. Демчик

Заказ 6385/45

Тираж 704

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

ав.Ч

Подписное

| Sutherland I.E | |||

| et | |||

| al | |||

| The TRIMOSBUS.- Proc, Caltechconference on VLSI, 1979, p | |||

| 395-427, 409 fig | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Taub D.M | |||

| Hardware method of synhronising processes without a clock.- Electronic letters, 1983, V | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Телефонная трансляция с катодным реле | 1921 |

|

SU772A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-12-07—Публикация

1986-09-29—Подача