4 4

00

Од СО

Изобретение относится к импульсной технике, в частности к цифровым делителям частоты, и может быть использовано для деления частоты сигналов типа меандр на нечетное число

с сохранением скважности входных сигналов .

Цель изобретения - расширение функциональных возможностей путем ю обеспечения скважности выходного сигнала, равной двум, для входного сигнала типа меандр.

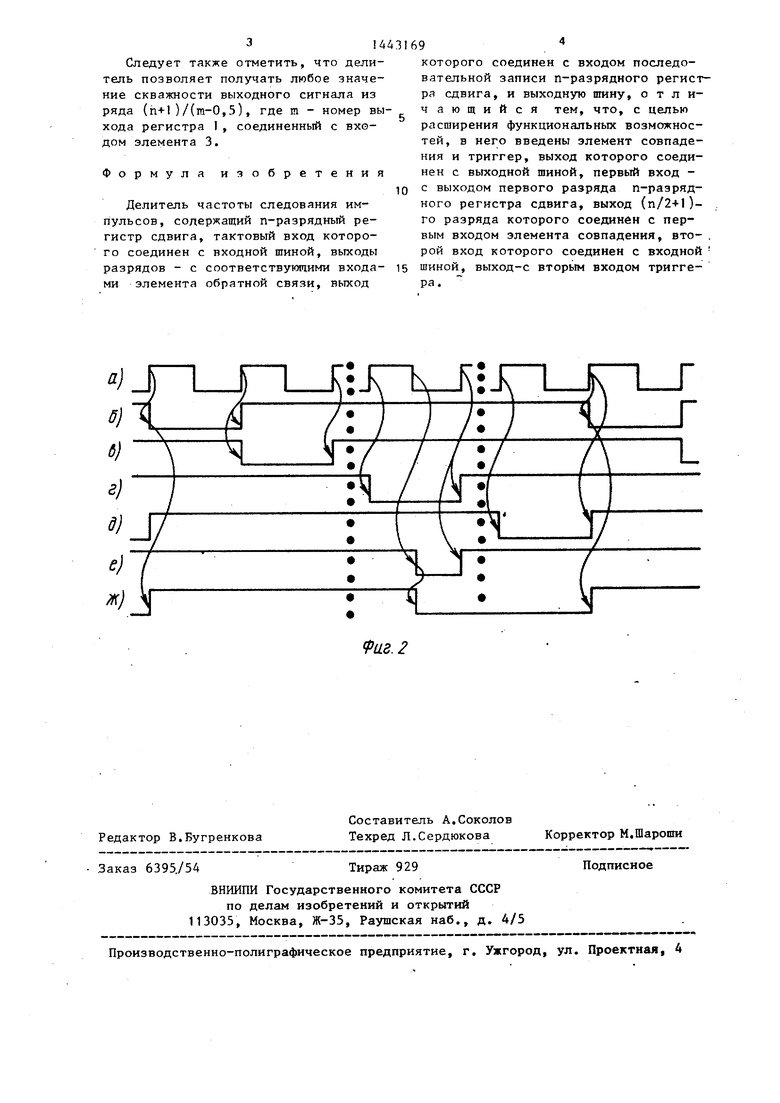

На фиг.1 приведена электрическая структурная схема делителя частоты; |5 на фиг,2 - временные диаграммы, поясняющие его работу.

Делитель частоты следования импульсов содержит п-разрядный (где п - четное число) регистр I сдвига, 20 выходы разрядов которого соединены с соответствующими входами.элемента

2обратной связи (например, элемента И-НЕ), выход которого соединен

с входом последовательной записи п- 25 разрядного регистра 1 сдвига, выход (n/2+l)-го разряда которого соединен с первым входом элемента 3 совпадения, выход первого разряда п-раз- рядного регистра 1 сдвига соединен 30 с первым входом триггера 4, выход которого соединен с выходной шиной 5, второй вход - с выходом- элемента

3совпадения, второй вход которого

регистра 1, т.е. в любой момент вр мени в нулевом состоянии находится только один из разрядов регистра 1 а остальные - в единичном (фиг.26, в,г). Когда разряд регистра 1 с но ром n/2+l установится в нулевое состояние, сигнал низкого уровня п тупает на первый вход элемента 3. Это происходит через п/2 тактов вх ного сигнала после того, как тригг 4 устанавливается в единичное состояние. Еще через 1/2 такта на в ром входе элемента 3 оказывается н кий уровень входного сигнала с щин 6, Это обуславливает появление на выходе элемента 3, а значит и на в ром входе триггера 4, сигнала низк го уровня (фиг.2е). Триггер 4 уста навливается в нулевое состояние. тем сдвиг нуля по разрядам регис ра продолжается до тех пор, пока последний его разряд, как и все ос тальные, не установится в единично состояние. Тогда на выходе элемент 2 появляется сигнал низкого уровня (фиг.2д) и цикл работы устройства этого момента повторяется. Во врем (п+)-го такта триггер 4 вновь уст навливается в единичное состояние. Таким образом, устройство имеет ко эффициент деления (n+l). Длительность интервала времени, в течение которого триггер 4 находится в еди

соединен с входной шиной бис такто- ничном состоянии, равна (in-l)- -0,5

вым входом п-разрядного регистра 1 сдвига.

Делитель частоты работает следующим образом.

В исходном состоянии все разряды 40 регистра 1 находятся в единичном состоянии, выход элемента 2 находится в нулевом состоянии, сигнал низкого уровня с выхода элемента 2 поступает на-вход последовательной записи 45 регистра 1.

При поступлении на шину 6 фронта входного импульса (фиг.2а) первый разряд регистра 1 устанавливается в нулевое состояние (фиг.2б). Осталь- JQ ные разряды регистра 1 остаются в единичном состоянии. Выходной сигнал низкого уровня с первого разряда регистра 1 поступает на первый вход триггера 4, устанавливая его в опре- j деленное состояние, например единичное (фиг.2ж). Далее при поступлении на шину 6 очередных импульсов происходит сдвиг нуля по всем разрядам

тактов входного сигнала, где m 2,3, ..., п - номер выхода регис ра 1 , к которому подключается вход элемента 3,

Таким образом, скважность выход

п + 1

ТтЛ7+П75

и, в частности, для предлагаемого в рианта делителя

ного сигнала равна q

q

n

TTn72+lT-l +0,5

2.

j

575

Предлагаемый делитель частоты м жет быть использован для получени гармонического сигнала, так как в спектре выходного сигнала делителя отсутствуют четные гармоники, кром того, делитель имеет незначительны искажения формы выходного сигнала при частоте входного сигнала, близ кой к предельной для выбранной эле ментной базы.

регистра 1, т.е. в любой момент времени в нулевом состоянии находится только один из разрядов регистра 1, а остальные - в единичном (фиг.26, . в,г). Когда разряд регистра 1 с номером n/2+l установится в нулевое состояние, сигнал низкого уровня поступает на первый вход элемента 3. Это происходит через п/2 тактов входного сигнала после того, как триггер 4 устанавливается в единичное состояние. Еще через 1/2 такта на втором входе элемента 3 оказывается низкий уровень входного сигнала с щины 6, Это обуславливает появление на выходе элемента 3, а значит и на втором входе триггера 4, сигнала низкого уровня (фиг.2е). Триггер 4 устанавливается в нулевое состояние. Затем сдвиг нуля по разрядам регистра продолжается до тех пор, пока последний его разряд, как и все остальные, не установится в единичное состояние. Тогда на выходе элемента 2 появляется сигнал низкого уровня (фиг.2д) и цикл работы устройства с этого момента повторяется. Во время (п+)-го такта триггер 4 вновь устанавливается в единичное состояние. Таким образом, устройство имеет коэффициент деления (n+l). Длительность интервала времени, в течение которого триггер 4 находится в едитактов входного сигнала, где m 2,3, ..., п - номер выхода регистра 1 , к которому подключается вход элемента 3,

Таким образом, скважность выходп + 1

ТтЛ7+П75

и, в частности, для предлагаемого варианта делителя

ного сигнала равна q

q

n

TTn72+lT-l +0,5

2.

j

575

Предлагаемый делитель частоты может быть использован для получения гармонического сигнала, так как в спектре выходного сигнала делителя отсутствуют четные гармоники, кроме того, делитель имеет незначительные искажения формы выходного сигнала при частоте входного сигнала, близкой к предельной для выбранной элементной базы.

3144,31

Следует также отметить, что делитель позволяет получать любое значение скважности выходного сигнала из ряда (h+1)/{га-0,5), где m - номер выхода регистра 1, соединенный с входом элемента 3.

Формула изобретения

Делитель частоты следования импульсов, содержащий п-разрядный регистр сдвига, тактовый вход которого соединен с входной шиной, выходы разрядов - с соответствующими входами элемента обратной связи, выход

694

которого соединен с входом последовательной записи п-разрядного регистра сдвига, и выходную шину, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены элемент совпадения и триггер, выход которого соединен с выходной шиной, первый вход - с выходом первого разряда п-разрядного регистра сдвига, выход (n/2+l)- го разряда которого соединен с первым входом элемента совпадения, вто- . рой вход которого соединен с входной шиной, выход-с вторым входом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU822377A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Генератор равномерно распределенных псевдослучайных чисел | 1977 |

|

SU674007A2 |

| Генератор последовательности импульсов с увеличивающейся длительностью | 1990 |

|

SU1713090A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Генератор последовательностей чисел | 1982 |

|

SU1067490A1 |

Изобретение относится к цифровым делителям частоты и может быть использовано для деления частоты сиг- . налов типа меандр на нечетное число с сохранением скважности входных сигналов. Цель изобретения - расширение функциональных возможностей - достигается путем обеспечения скважности выходного сигнала, равной двум, для входного сигнала типа меандр. Делитель частоты следования импульсов содержит п-разрядный регистр 1 сдвига, выходы разрядов которого соединены с соответствующими входами элемента 2 обратной связи, например элемента И-НЕ, выходную шину 5 и входную шину 6. В устройство дополнительно введены элемент 3 совпадения - и триггер 4. Предложенный вариант схемного построения обеспечивает сохранение указанной скважности при частоте входного сигнала, близкой к максимальной, для схемных элементов,входящих в делитель. 2 ил. (Л

Редактор В.Бугренкова

Составитель А.Соколов Техред Л.Сердюкова

Заказ 6395./54

Тираж 929

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Корректор М.Шароши

Подписное

| Делитель частоты следования импульсов | 1985 |

|

SU1243131A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Справочник | |||

| /Под ред | |||

| Б.Н.Файзу- лаева, Б.В.Тарабрина | |||

| - М.-; Радио и .связь, 1986, с.112, рис.5.54. | |||

Авторы

Даты

1988-12-07—Публикация

1987-05-27—Подача