Л

Изобретение относится к контрольно-измерительной технике и может быть использовано в аппаратуре контроля логических блоков.

Целью изобретения является расширение функциональных возможностей выходного узла устройства контроля логических блоков за счет обеспечения распознавания третьего высокоимпе.-- дансного состояния проверяемых логических элементов с одновременным обеспечением проверки логических уровней на соответствие их установленным пределам.

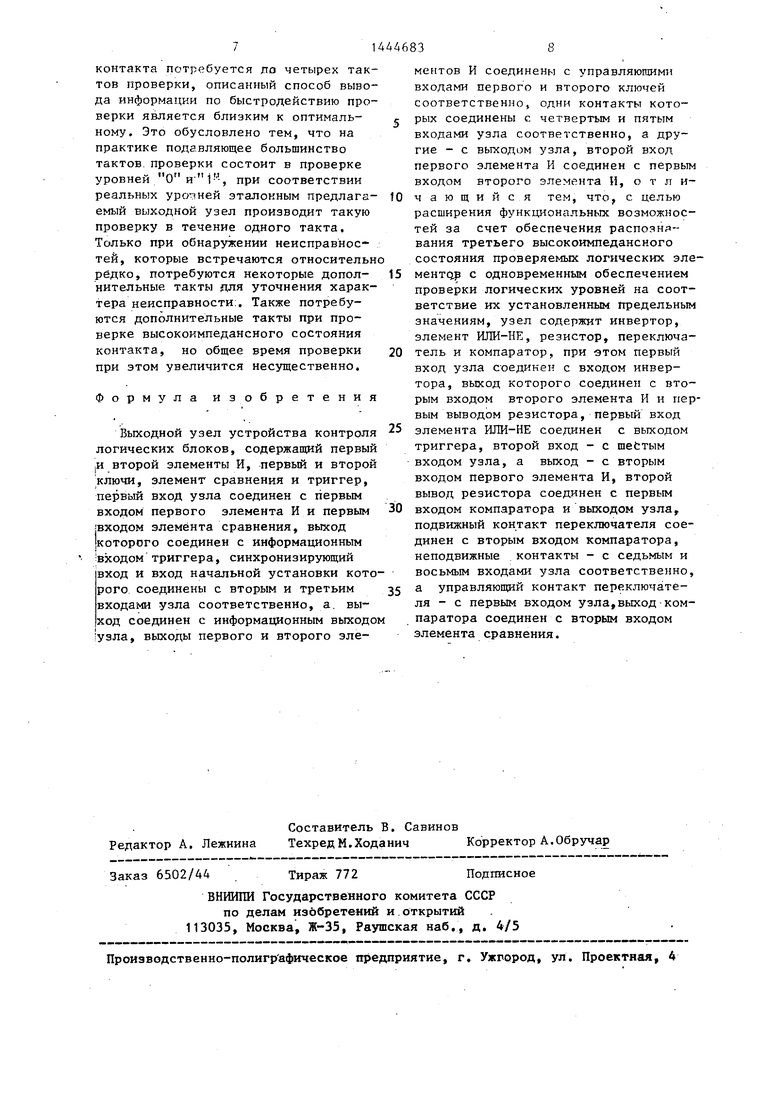

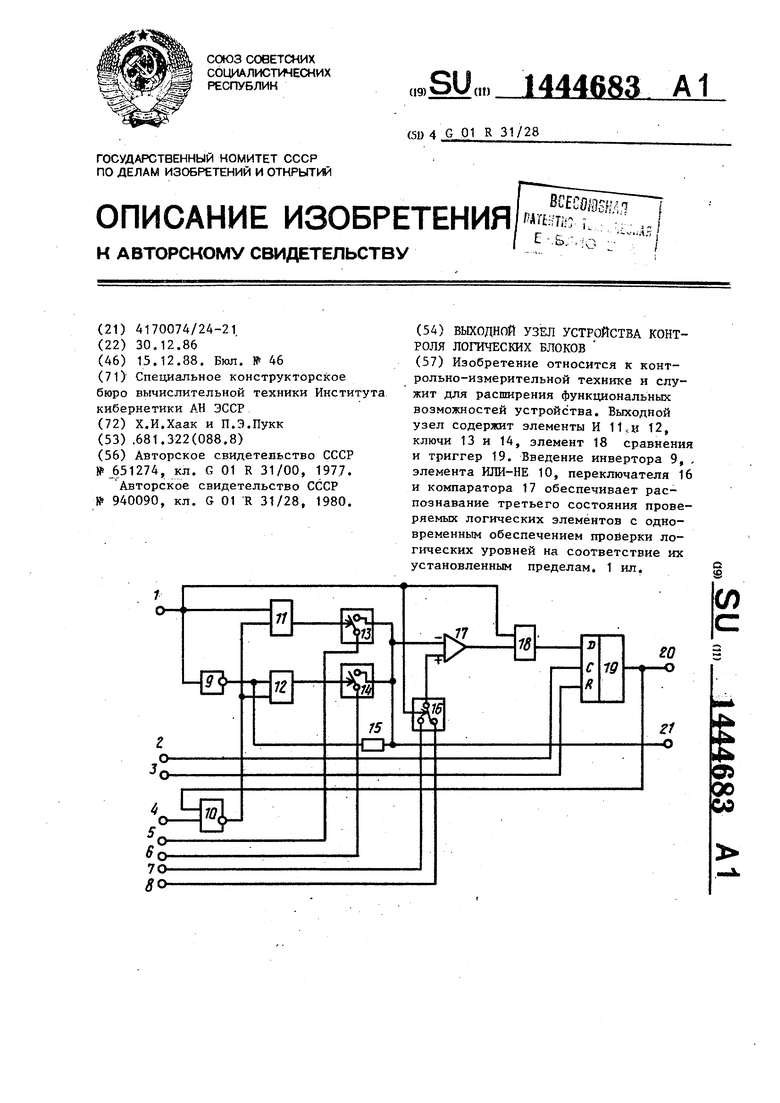

На чертеже изображена (Ьункциональ- ная схема выходного узла устройства контроля логических блоков.

Выходной узел содержит первый 1, второй 2, третий 3, четвертый 4, .пятый 5,шестой 6,седьмой 7 и восьмой 8 входы, инвертор 9, элемент ИЖ-НЕ 10, первый 11 и второй 12 элементы И, первый 13 и второй 14 ключи (на чертеже изображены в положении, соот- ветствующем сигналу О на управляющем входе), резистор 15, переключатель 16 (в положении, соответствующем сигналу О на управляющем входе), компаратор 17, элемент 18 сравнения, триггер 19, информационный выход 20 и выход 21.;

Вход 1 узла, на который подается тестовая информадая, соединен с первым входом элемента И 11, входом ни- вертора 9, управляющим входом переключателя 16 и первым входом элемента 18 свавнения. Вход 2 узла соединен с синхроиизирующмм входом триггера 19. Вход 3 соединен с входом началь- ной установки триггера 19. Вход 4 узла, сигнал на котором изменяется в зависимости от того, подключен выходной узел к входному или выходному контакту проверяемого блока, соединен с вторым входом элемента ИЛИ-НЕ. Вход 5 соединен с первым контактом ключа 13 и на него подается напряжение и. , величина:; которого

соответствует величине 1. Вход 6 узла соединен с первым контактом ключа 14 и слулмт для передачи величины напряжения U, соответствующей О. Входы 7 и соединены с пере- ключаень№Ш контактами переключателя 16 и на них подаются напряжения и„, и и„ соответствен но, соответствующие .пороговым напряжениям 1 и О, принятых в проверяемом блоке. Выход

) 5

5 0 5

0

элемента ИЛИ-НЕ lb соединен с вторым входом элементов.И 11 и 12, Выход инвертора 9 соединен с первым входом элемента И 12 и первым выводом резистора 15, а выходы элементов И 11 и 12 соединены с управляющим входом ключей 13 и 14 соответственно. Первый вход элемента ИЛИ-НЕ 10 соединен с выходом триггера 19 и выходом 20 узла. Вторые контакты ключей 13 и 14 с оединены с первым входом компаратора 17, вторым выводом резистора 15 и выходом 21 узла. Второй вход компаратора 17 соединен с центральным контактом переключателя 16, Выход компаратора 17 соединен с вторым входом элемента 18 сравнения, выход которого соединен,с информационным входом триггера 19,

Выходной узел работает -следующим образом,

В работе выходного узла имеется два режима в зависимости от вида контакта проверяемого логического блока. Б первом режиме выходной узел используется для подачи логических уровней на контакт проверяемого блока, который является его входом, а во втором режиме задачей выходного узла является распознавание логических уровней гсонтакта, который является выходом проверяемого блока, В обоих режимах работы проверяемым контактом является выход 21 узла, а его выход 20 является дополнительным информационным выходом,

Если проверяемый устройством контакт является входом логического блока, то на вход 4 подается уровень О, В начале каждого такта прЬверки на

вход 3 подается импульс, который устанавливает выход триггера 19 в нулевое состояние.

Уровень О поступает также на первый вход элемента ИЛИ-НЕ 10, на выходе которого образуется сигнал 1, который поступает на вторые входы элементов И 11 и 12,

-

5ходвм 1 узла определяется подаваемая на объект тестовая информация. При 1 на входе 1 этот уровень проходит через элемент И 11 на управля- кяций вход ключа 13 и напряжение U , определяющее уровень 1 с входа 5 узла, через замкутый ключ 13 постУ7 пает на второй вход 21 узла, которьй подключен к контакту проверяемого логического блока, В этом случае на

выходах элементов 9 и 12 уровни О и ключ 14 разомкнут.

При О на входе 1 замкнут ключ 14 и разомкнут ключ 13, следователь но, на второй выход 21 узла, а также на вход проверяемого блока от входа 6 узла поступает напряжение Up, определяющее уровень О,

Напряжение от выхода ключей 13 и 14 поступает также на компаратор 17, который в этом режиме совместно с элементом 18 и триггером 19 выполняет функцию защиты ключей выходного узла от nepf rpysKH, На второй вход компаратора поступает опорное напряжение с входа 7 кие и„д

сигнала на входе 1 узла. Напряжения Uj, ;и Ufio представляют собой предель но допустимые уровни для логических сигналов. Например, для ТТЛ-элементо

j,i .. , узла или напряже с входа 8 с зависимости от

обычно Uf,, 2,4 В и Uno 0,4 В. Для нормальной работы выходного у-зла необходимо, чтобы уровни U и Uo на входах 5 и 6 узла соответствовали условиям и,и„, и UQ

Если, например, на входе 1 узла уровень 1, то напряжение U, на втором выходе 21 узла отличается от напряжения U, только падением напряжения на ключе 13, которое при нормальном токе нагрузки незначительное, следовательно U,-;t U и„, . Так как на второй вход компаратора 17 через переключатель 16 поступает напряжение 1Т„ , выход компаратора приобретает уровень 1, а на выходе элемента 18 появляется уровень О. С определенной задержкой, которая нужна для завершения переходных процессов в ключах и в компараторе, подается синхроимпульс через вход 2 узла на синхронизирующий вход триггера 19 и триггер записывает информацию с его информационного входа на выход. Так как на выходе триггера 19, а также на первом выходе 20 : 1узла и заранее бьт уровень нули.

15 ключает его выход на О. Уровень О п оходит через элемент И 11 на управляющий вход ключа 13 и размыкает его, защищая его таким образом от перегрева. Время.задержки подачи синхроимпульса на вход 2 узла по отношению к моменту изменения входных воздействий на входах 1 и 4 .узла определяет быстродействие защиты .

25 Аналогично при подаче нуля на

вход 1 узла и при нормальной нагрузке выхода напряжение на выходе 21 приобретает значение UHQ. Через переключатель 16 на второй

30 вход компаратора 17 поступает напряжение Uj,o выход компаратора, а также выходы элемента 18 и триггера 19 приобретают значение О, что свидетельствует о нормальной работе уз35 ла. Если, например, в проверяемом блоке имеется замыкание данного контакта на уровень 1 (на цепь питания) , резко увеличивается ток через ключ 14. Напряжение U на выходе 21

40 узла становится больше опорного I f,o , компаратор переключается, на выходе 20 узла появляется уровень 1, в результате чего ключ 14 переводится в непроводящее состояние.

45 Второй режим узла используется при проверке устройством контактов, являющихся выходами проверяемого

блока. В этом резкиме на вход 4 пода- м 1 ti

ется уровень 1

элемента

на выходе

этот уровень не- изменяется. Уровень go ИЛИ-НЕ 10 .появляется уровень О, ко- 0 на информационном вьгходе 20 сви торый через элементы И 11 и 12 посту- о

детельствует о нормальной р абр-ге выходного узла при вьщаче логических уровней.

В случае короткого замыкания контакта проверяемого блока на нулевой потенциал резко увеличивается ток через ключ 13, увеличивается падение

55

пает на первые входы ключей 13 и 14 и держит их в непроводящем состоянии.

На вход 1 в этом режиме подаются эталонные реакции, т.е. ожидаемые логические уровни проверяемого контакта. Например, при подаче 1 на.

напряжения на ключе и напряжение

0

U) на выходе 21 становится меньше опорного Up, В результате компаратор 17 переключается, на его выходе появляется О, а на выходе элемента 18 1. При поступлении синхроимпульса уровень 1 поступает также на выход триггера 19 и на информационный выход 20 узла. Высокий уровень на выходе 20 узла в первом режиме свидетельствует о перегрузке ключей. Уровень 1 поступает также на первый вход элемента И.Щ-НЕ 10 и пере5 ключает его выход на О. Уровень О п оходит через элемент И 11 на управляющий вход ключа 13 и размыкает его, защищая его таким образом от перегрева. Время.задержки подачи синхроимпульса на вход 2 узла по отношению к моменту изменения входных воздействий на входах 1 и 4 .узла определяет быстродействие защиты .

5 Аналогично при подаче нуля на

вход 1 узла и при нормальной нагрузке выхода напряжение на выходе 21 приобретает значение UHQ. Через переключатель 16 на второй

0 вход компаратора 17 поступает напряжение Uj,o выход компаратора, а также выходы элемента 18 и триггера 19 приобретают значение О, что свидетельствует о нормальной работе . Если, например, в проверяемом блоке имеется замыкание данного контакта на уровень 1 (на цепь питания) , резко увеличивается ток через ключ 14. Напряжение U на выходе 21

0 узла становится больше опорного I f,o , компаратор переключается, на выходе 20 узла появляется уровень 1, в результате чего ключ 14 переводится в непроводящее состояние.

5 Второй режим узла используется при проверке устройством контактов, являющихся выходами проверяемого

блока. В этом резкиме на вход 4 пода- м 1 ti

ется уровень 1

элемента

на выходе

go ИЛИ-НЕ 10 .появляется уровень О, ко- торый через элементы И 11 и 12 посту-

55

пает на первые входы ключей 13 и 14 и держит их в непроводящем состоянии.

На вход 1 в этом режиме подаются эталонные реакции, т.е. ожидаемые логические уровни проверяемого контакта. Например, при подаче 1 на.

вход 1 через переключатель 16 на второй вход компаратора поступает напряжение и, и в случае, если U ц ги вы- ходах элемента 18 и триггера 19г1оявля- ются уровни О. Элементы 17, 18 и 1 работают аналогично первому режиму с той/разницей, что теперь уровень О на информационном выходе 20 свидетелствует о том, что действительный уровень на данном контакте проверя емого блока соответствует эталонному а задержка, подачи синхроимпульса на вход 2.узла должна быть выбрана с учетом задержки распространения сиг налов в проверяемом блоке (должна быть больше задержки блока).

. В случае, если вместо ожидаемой 1 на данном контакте проверяемого блока обнаруживается уровень.О или недопустимо низкий уровень 1, переключается компаратор 17 и после подачи синхроимпульса на выходе 20 появляется уровень 1, свидетельствующий о том, что действит-ельный уровень на данном контатсте проверяемого блока не соответствует эталонному .

Аналогично при подаче на вход 1 узла уровня О напряжение U от выхода проверяемого блока сравнивается с опорным напряжением . Если , на информационном выходе 20 сохраняется уровень О, а в случае, если действительный уровень вьше опорного Uno выходе 20 появляется 1.

Величина резистора 15 выбрана такой, что ток через этот резистор

5

0

5

0

резистора 15 поря дка нескольких десяткон килоом.

Если при проверке контакта, кото- рьй находится в высокоимпеданс- ном состоянии, в качестве эталона, на вход 1 узла поступает уровень 1, на выходе инвертора 9 образуется уровень О и через резистор 15 вы-, ход 21 также приобретает уровень напряжения, близкий к О, После подачи синхроимпульса на информационный выход 20 узла поступает сигнал 1, который указывает, что уровень U не соответствует 1. Аналогично при подаче на вход 1 узла в качестве эталона уровня О на выходе инвертора 9 появляется уровень 1, напряжение и ц. на выходе 21 также приобретает значение, близкое к уровню 1 и уровень 1 на выходе 20 узла индицирует, что контакт не имеет уровня Следовательно, высокоимпеданс- ное состояние характеризуется тем, что на информационном выходе 20 узла появляется уровень 1 при обоих эталонных уровнях на входе 1 узла.

Такой же результат получается при проверке логического элемента, выход которого находится в промежуточном состоянии между уровнями О и 1

(

) . Такое состояние

возможно при дефектном элементе или при-перегрузке его выхода другими элементами проверяемого блока.

Для различения такого дефектного состояния от высокоимпедансного,- : оторое является нормальным для ряда

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1164711A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Выходной узел тестера для контроля логических устройств | 1977 |

|

SU651274A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| УСТРОЙСТВО КОНТРОЛЯ КОНТАКТИРОВАНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1991 |

|

RU2020498C1 |

| Устройство для управления встречно-параллельно включенными тиристорами | 1989 |

|

SU1697211A1 |

| Устройство преобразования аналогового видеосигнала в двухуровневый | 1982 |

|

SU1107335A1 |

Изобретение относится к контрольно-измерительной технике и служит для расширения функциональных возможностей устройства. Выходной узел содержит элементы И 11,и 12, ключи 13 и 14, элемент 18 сравнения и триггер 19. Введение инвертора 9, , элемента ШШ-НЕ 10, переключателя 16 и компаратора 17 обеспечивает распознавание третьего состояния проверяемых логических элементов с одновременным обеспечением проверки логических уровней на соответствие их установленным пределам. 1 ил. с

не превьпиает допустимого для применя-дд логических элементов, производят доемых в контролируемых логических блоках логических элементов .Таким-обра зом, этот резистор существенно не влияет на уровень выходного напряжения контакта и на выходе 21 узла, если логический элемент проверяемого блока, который связан с этим контактом, находится в состоянии О или 1.

Однако,в случае, если указанный элемент находится в высокоимпеданс- ном состоянии, поскольку величина резистора 15 выбрана существенно меньше выходного сопротивления логических элементов в этом состоянии, напряжение U| на выходе 21 становится близким к Уровню напряжения на выходе инвертора 9. Например, для ТТЛ-элементов подходящая величина

45

50

55

полнительные такты npoBepkn. Для этого данный контакт со стороны входа 4 узла переключается нак вход проверяемого блока и на вход 1 узла последовательно задают уровни О и 1 согласно описанному первым режиму. Если контакт в высокоимпе- дансном состоянии, на обоих контактах проверки выход 20 узла сохраняет уровень нуля. Б случае промежуточного уровня от дефектного элемента на одном или обоих тактах проверки появляется перегрузка ключей и срабатывает схема защиты, о чем индицирует появление уровня 1 на выходе 20 .узла.

Несмотря на то,что в некоторых случаях для точного определения состояния

5

0

5

полнительные такты npoBepkn. Для этого данный контакт со стороны входа 4 узла переключается нак вход проверяемого блока и на вход 1 узла последовательно задают уровни О и 1 согласно описанному первым режиму. Если контакт в высокоимпе- дансном состоянии, на обоих контактах проверки выход 20 узла сохраняет уровень нуля. Б случае промежуточного уровня от дефектного элемента на одном или обоих тактах проверки появляется перегрузка ключей и срабатывает схема защиты, о чем индицирует появление уровня 1 на выходе 20 .узла.

Несмотря на то,что в некоторых случаях для точного определения состояния

контакта потребуется до четырех тактов проверки, описанный способ вывода информации по быстродействию проверки является близким к оптимальному. Это обусловлено тем, что на практике подавляющее большинство тактов, проверки состоит Б проверке уровней О И I- -, при соответствии реальных урсганей эталонным предлагаемый выходной узел производит такую проверку в течение одного такта. Только при обнаружении неисправностей, которые встречаются относительн редко, потребуются некоторые дополнительные такты для уточнения характера неисправности:. Также потребуются дополнительные такты при проверке высокоимпедансного состояния контакта, но общее время проверки при этом увеличится несущественно.

Формула изобретения

Выходной узел устройства контроля логических блоков, содержащий первый ,и второй элементы И, первый и второй ключи, элемент сравнения и триггер, первый вход узла соединен с первым входом первого элемента И и первым шходом элемента сравнения, выход которого соединен с информационным :входом триггера, синхронизирующий вход и вход начальной установки которого соединены с вторым и третьим входами узла соответственно, а. выход соединен с информационным выходом iysna, выходы первого и второго элементов И соединены с управляющими входами первого и второго ключей соответственно, одни контакты которых соединены с четвертым и пятым входами узла соответственно, а другие - с выходом узла, второй вход первого элемента И соединен с первым входом второго элемента И, о т л и10 чающийся

тем.

5

0

5

0 5

расширения функциональных возможностей за счет обеспечения распозня-- вания третьего высокоимпедансного состояния проверяемых логических эле- ментор с одновременным обеспечением проверки логических уровней на соответствие их установленным предельным значениям, узел содержит инвертор, элемент ИЛИ-НЕ, резистор, переключатель и компаратор, при этом первый вход узла соединен с входом инвертора, выход которого соединен с вторым входом второго элемента И и первым выводом резистора, первый вход элемента ИЛИ-НЕ соединен с выходом триггера, второй вход - с щеЬтым входом узла, а выход - с вторым входом первого элемента И, второй вывод резистора соединен с первым входом компаратора и выходом узла, подвижный контакт переключателя соединен с вторым входом компаратора, неподвижные контакты - с седьмым и восьмым входами узла соответственно, а управляющий контакт переключателя - с первым входом узла,выход компаратора соединен с вторым входом элемента сравнения.

| Выходной узел тестера для контроля логических устройств | 1977 |

|

SU651274A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Выходной узел тестера для контроля логических блоков | 1980 |

|

SU940090A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-12-15—Публикация

1986-12-30—Подача