Изобретение относится к вычислительной технике, в частности к устройствам сопряжения, и может быть использовано для программно-аппаратного вычисления булевых функций, зависящих от локальных дискретных сигналов.

Целью изобретения является увеличения быстродействия.

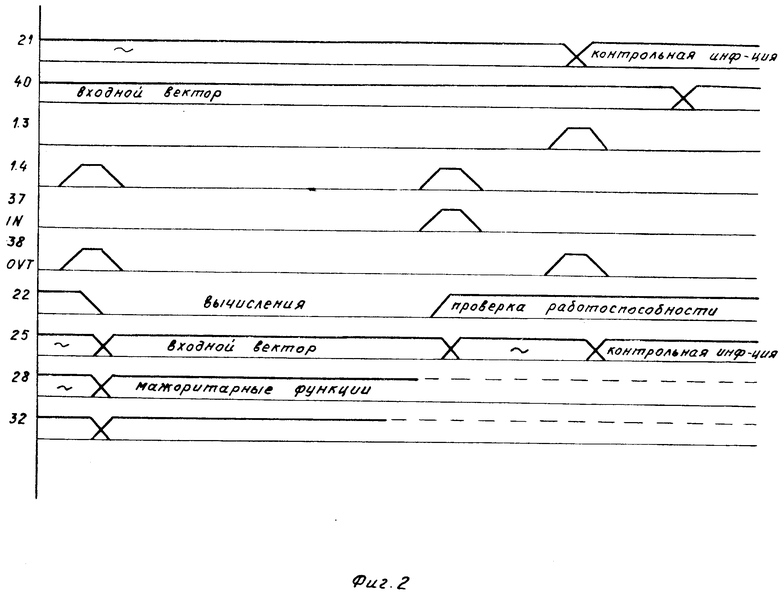

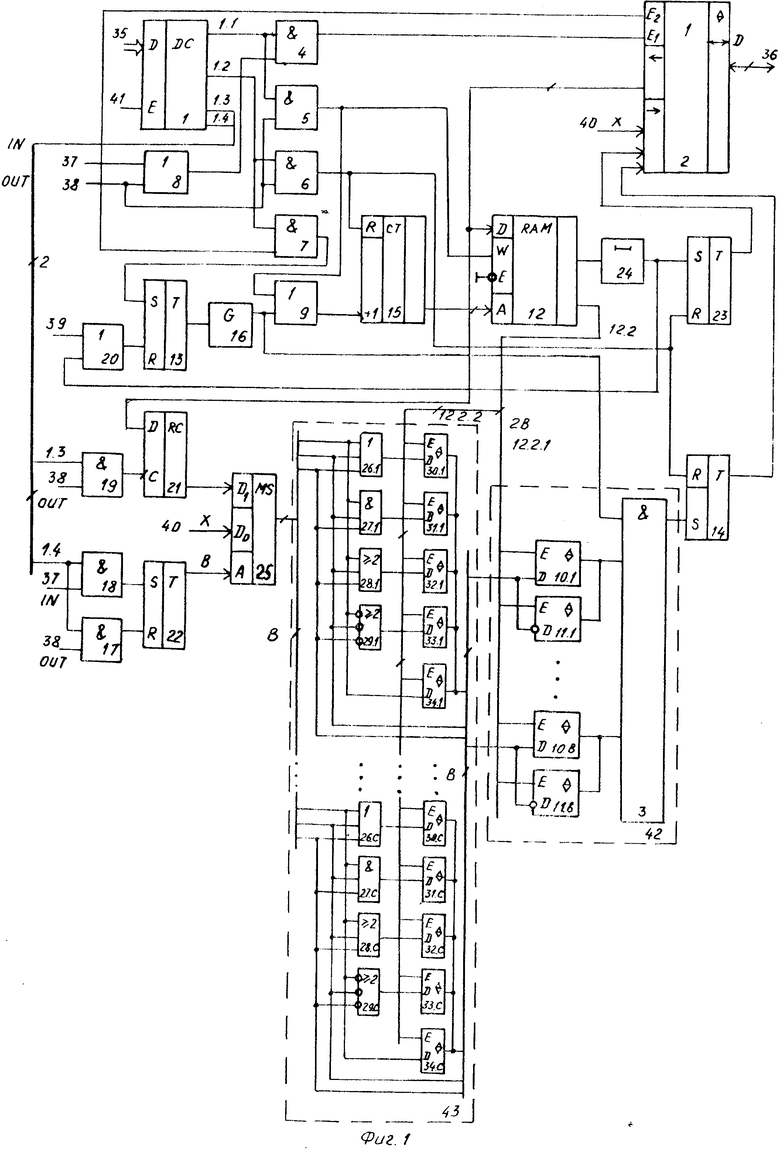

На фиг. 1 изображена функциональная схема предлагаемого устройства для ввода в микроЭВМ дискретных сигналов; на фиг. 2 - временная диаграмма работы устройства при настройке и при вычислении значения функции.

Устройство для ввода в микроЭВМ дискретных сигналов содержит дешифратор адреса 1, шинный формирователь 2, пять элементов И 3-7, два элемента ИЛИ 8, 9, группу элементов И 10.1-10. В с тремя состояниями на выходе, где В - количество разрядов входного дискретного сигнала, группу элементов И-НЕ 11.1-11. В с тремя состояниями на выходе, оперативную память 12, два триггера 13, 14, счетчик 15, генератор 16 импульсов, элементы И 17. . . 19, элементы ИЛИ 20, регистр 21, триггеры 22, 23, элемент 24 задержки, мультиплексор 25, группу элементов ИЛИ 26.1, . . . , 26. С, где С = B/3, группу элементов И 27, группу мажоритарных элементов 28, группу мажоритарных элементов 29 с инверсией на входах, группу магистральных элементов И 30. . . 34 (с тремя состояниями на выходе), входы 35 адреса, входы-выходы 36 данных, входы 37, 38 управления, вход 39 сброса, информационные входы 40, вход 41 разрешения, мультиплексор 42, образованный элементом И 3, группой элементов И 10, группой элементов И-НЕ 11, шифратор 43, образованный группой элементов ИЛИ 26, группой элементов И 27, группой мажоритарных элементов 28, группой мажоритарных элементов 29 с инверсией на входах и группой магистральных элементов 30, . . . , 34.

Устройство для ввода в микроЭВМ дискретных сигналов работает следующим образом.

1. Настройка. При этом внешняя микроЭВМ, подключенная к устройству ко входам адреса 35, входам/выходам данных Ш6, входам управления 37 ("Чтение"), 38 ("Запись"), обращается к нему как к порту вывода с фиксированным адресам. Активируется вход 41. Активируется вход управления 38 ("Запись"), на входах 35 выставляется адрес, активирующий выход 1.1 дешифратора 1, активируется выход элемента ИЛИ 8. Поэтому активируется выход элемента И 4, подключающий шинный формирователь 2 по первому входу управления (Е1) ко входам/выходам 35, а так как второй вход управления (Е2) неактивирован, то шинный формирователь 2 подключается в режиме ввода со входом-выходом 36, информация с которых передается на входы данных оперативной памяти 12. Оперативная память 12 имеет постоянно активированный вход управления, поэтому активированный выход элемента И 5 переводит ее в режим записи по входу записи. Счетчик 15 обнулен в исходном положении по цепям сброса, не указанным на фиг. 1, поэтому на входах адреса оперативной памяти 12 выставлен адрес нулевой ячейки (см. фиг. 1).

В оперативную память 12 записывается первое слово информации с выходов блока 2. По заднему фронту сигнала на выходе элемента И 5 (и, соответственно, по заднему фронту сигнала на выходе элемента ИЛИ 9) изменяется состояние счетчика 15 и его выходные сигналы адресуют следующую ячейку оперативной памяти 12.

При очередном обращении к устройству аналогично запишется второе слово информации. Далее устройство работает аналогично. Далее внешняя микроЭВМ обнуляет счетчик 15, причем на входах адреса 35 устанавливается код, возбуждающий выход 1, 2 дешифратора 1, и активируется вход 38. Поэтому сигнал с выхода элемента И 6 обнуляет счетчик 15 и триггеры 14, 13. Для ввода информации с локальной обработкой внешняя микроЭВМ обнуляет также триггер 22, при этом выставляется адрес (на входах 35, активирующий выход 1.4) дешифратора 1 и возбуждается вход 37, что приводит к возбуждению выхода элемента И 17 и обнулению триггера 22, т. е. на выходы мультиплексора 25 подключается информация с его первой группой входов, подключенной к выходам триггеров 13, 14. Устройство готово к локальной обработке сигналов на информационных входах 40, либо контрольной информации на выходах регистра 21.

2. Вычисление функций от резервированных дискретных сигналов. Для производства таких вычислений в оперативную память 12 выводятся константы, имеющие следующий формат: 1) поле 12.2.1 - после управления группами элементов 10, 11 - заполняются аналогично прототипу; 2) поле 12.2.2 - поле управления группами элементов 26, 27, 28, 29, 34 - унитарный пятиразрядный код, единица в позиции которого определяет вариант предварительной обработки резервированных сигналов - либо обработка по функции ИЛИ (сработала хотя бы одна цепь датчика) - включается в работу группа элементов ИЛИ 260 либо обработка по функции И (сработали все цепи датчика) - включается в работу группа элементов И 27, либо обработка по мажоритарной функции (сработало ≥2 цепей датчиков) - включаются в работу группа мажоритарных элементов 28, либо обработка по мажоритарной функции от инверсных сигналов (не сработало ≥2 цепей датчиков) - включаются в работу группа мажоритарных элементов 29 с инверсными входами, либо обработка предварительная отсутствует - включаются в работу магистральные элементы 34 (при наличии единицы на одном из пяти разрядов выходов 12.2.2 подключаются соответствующие магистральные элементы групп 30, 31, 32, 33, 34, а выходы остальных находятся в высокоимпедансном состоянии и не влияют на работу элементов групп 10, 11); 3) поле 12.1 содержит один разряд и предназначено для фиксации факта выборки последней константы массива, оно управляет элементом задержки 24.

Таким образом, при необходимости предварительной обработки резервированных сигналов датчиков они проходят через соответствующий элемент групп 26, 27, 28, 29, при отсутствии такой необходимости сигнал с первой цепи проходит через соответствующий магистральный элемент 34. Тогда на входы 1, 4, 7. . . +3-го элемента 10(11) может поступать предварительно обработанная информация, что сокращает время вычисления основной функции, которая зависит от результатов предварительно вычисленных функций от троированных сигналов с датчиков.

Так, для вычисления функции (х1 ≥2)& & (х2 ≥2) . . . & (хn ≥2), где х1-хn-n датчиков, цепи которых троированы, на выходах 12.2.2 блока 12 должна быть константа 0 0 1 0 0, на выходах 12.2.1 - константа 10 10 10. . . 10 (функция В) и вычисления будут закончены за один такт (необходима всего одна константа).

Для вычисления функции (х1 ≥2) V V(х2 ≥2) V. . . V(хn ≥2) необходимо констант (по выходу 12.2.1 блока 12) 10 00. . . 00, соответственно для каждой на выходе 12.2.2 должен быть тот же код 0 0 1 0 0.

Аналогично можно представить константами другие функции. Очевидно, что наблюдается выигрыш во времени за счет предварительного вычисления функций от троированных сигналов датчиков, которые производят параллельно с вычислениями, аналогичными вычислениям в прототипе на элементах групп 10, 11.

На фиг. 2 показано, что для производства вычислений обнуляется триггер 22, на выходе мультиплексора 25 устанавливается входной вектор, а на выходах элементов групп 28, 32 - мажоритарные функции от троированных сигналов датчиков.

Запись констант и вычисления аналогичны прототипу (не указаны на фиг. 2), за исключением - по окончании вычислений, когда выбирается последняя константа - устанавливается триггер 23.

Кроме того, в предлагаемом устройстве возможно вычисление логических функций, зависящих от аргументов, формируемых самой микроЭВМ и выводимых в регистр 21 так, как будет описано в разделе проверки работоспособности.

3. Проверка работоспособности устройства.

В этом режиме предварительно устанавливается триггер 22 (см. фиг. 1.2). Для этого внешняя микроЭВМ обращается к устройству как к порту с фиксированным адресом, который будучи установлен на входах 35 приводит к возбуждению выхода 1.4 дешифратора 1, у которого, кроме того, возбужден вход разрешения 41. Возбуждается вход 37 устройства. Поэтому возбуждается выход элемента И 18, который, воздействуя на вход установки триггера 22, устанавливает его. В связи с этим на выход мультиплексора 25 подключаются выходы регистра 21. Затем в оперативную память 12 аналогично прототипу записываются константы, описывающие контрольную функцию (не указано на фиг. 2, аналогично прототипу). Для записи в регистр 21 контрольного входного вектора он передается с выходов шинного формирователя 1, у дешифратора 1 возбуждается выход 1.3, причем внешняя микроЭВМ обращается к устройству как к порту вывода, т. е. возбуждается и вход 38 устройства. Поэтому возбуждается выход элемента И 19 и контрольный входной вектор записывается в регистр 21. Затем аналогично прототипу инициируются вычисления, по окончании которых устанавливается триггер 23 готовности результата (с задержкой, определяемой элементом задержки 24, после того, как считывается последняя константа и возбуждается отдельный выход блока 12). Если вычисленная функция равна 1, то аналогично прототипу устанавливается триггер 14. Внешняя микроЭВМ сканирует состояние триггера 23 и при наличии логической единицы на его выходе анализирует состояние триггера 14. Затем аналогично прототипу обнуляются триггеры 23, 14 (триггер 14 обнуляется сигналом с выхода блока 24), а регистр 21 выводится очередной контрольный вектор, в блок 12 выводится константа очередной контрольной функции и вновь инициируются вычисления. По результатам контроля внешняя микроЭВМ делает вывод о работоспособности устро- йства. После этого в блоке 12 выводятся константы основной функции, обнуляется триггер 22 (возбуждается выход 1.4 дешифратора 1 при обращении к устройству как к порту вывода - возбуждается вход 38 и выход элемента И 17), после чего через мультиплексор 25 подключаются входы 40 входного вектора - дискретные сигналы с датчиков. Затем устройство работает аналогично прототипу.

Проверка работоспособности устройства может приводиться как проверка оперативной памяти, т. е. , например, контро- лируется реакция на "бегущий ноль" и "бегущую единицу".

Тогда контрольные входные векторы, выводимые в регистр 21, имеют вид:

0111. . . 1, 101. . . 1; . . . . . . ; 111. . . 0. А соответствующие константы, записываемые в блок 12, реализуют такие булевые функции:

f1 = x1, f2 = x2, . . . , fn = xn Для "бегущей единицы":

100. . . 0; 010. . . 0; 000; 00. . . 01.

f1 = x1, f2 = x2, . . . , fn = xn. Аналогично можно реализовать более сложные тексты, например, вычисление конъюнкции или последовательность конъюнкции от разрядов контрольного входного вектора, вычисления дизъюнкций от его разрядов и т. д.

При необходимости ввода части информации без локальной обработки соответствующие дискретные сигналы могут быть подключены непосредственно к части входов шинного формирователя 2 (на фиг. 1 показано подключение тех же информационных сигналов 40).

(56) Авторское свидетельство СССР N 1314345, кл. G 06 F 19/00, 1987.

Авторское свидетельство СССР N 1503043, кл. G 06 F 13/00, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| Устройство для ввода в ЭВМ дискретных сигналов | 1990 |

|

SU1786481A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1987 |

|

SU1503043A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Устройство для ввода-вывода дискретных сигналов микроЭВМ | 1989 |

|

SU1681306A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1986 |

|

SU1314345A1 |

Изобретение относится к вычислительной технике, в частности к устройствам сопряжения, и может быть использован для программно-аппаратного вычисления булевых функций, зависящих от локальных дискретных сигналов. Устройство позволяет повысить быстродействие в задачах обслуживания резервированного оборудования и контроле пригодности путем введения дисциплины предварительной логической обработки троированных сигналов датчиков и формирования контрольного входного вектора. Устройство содержит дешифратор адреса, шинный формирователь, пять элементов И, два элемента ИЛИ, группу элементов И с тремя состояниями на выходе, группу элементов И - НЕ с тремя состояниями на выходе, оперативную память, два триггера, счетчик, генератор импульсов, элементы И, элемент ИЛИ, регистр, триггеры, элемент задержки, групповой мультиплексор, группу элементов ИЛИ, группу элементов И, группу мажоритарных элементов, группу мажоритарных элементов с инверсией на входах, группу магистральных элементов И (с тремя состояниями на выходе), входы адреса, входы - выходы данных, входы управления, вход сброса, информационные входы, вход разрешения. 2 ил.

УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ, содержащее дешифратор адреса, шинный формирователь, пять элементов И, два элемента ИЛИ, первый мультиплексор, оперативную память, два триггера, генератор тактовых импульсов и счетчик, причем информационный вход дешифратора адреса является входом устройства для подключения к шине адреса микроЭВМ, первый выход дешифратора адреса соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с входом выборки шинного формирователя, вход задания направления передачи которого является входом устройства для подключения к выводу команды ввода шины управления микроЭВМ и соединен с первыми входами третьего элемента И, первого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, вторые входы первого элемента ИЛИ, второго элемента И, первый вход четвертого элемента И объединены и являются входом устройства для подключения к выводу команды вывода шины управления микроЭВМ, вход/выход шинного формирователя соединен с входом/выходом устройства для подключения к шине данных микроЭВМ, информационные входы оперативной памяти соединены с выходами шинного формирователя, вход записи оперативной памяти соединен с выходом второго элемента И и с первым входом второго элемента ИЛИ, адресные входы оперативной памяти соединены с разрядными выходами счетчика, второй выход дешифратора адреса соединен с вторым входом третьего и четвертого элементов И, выход третьего элемента И соединен с входом установки первого триггера, выход которого соединен с входом пуска генератора тактовых импульсов, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с счетным входом счетчика, выход первого мультиплексора соединен с входом установки второго триггера, вход сброса которого соединен с выходом четвертого элемента И, первый выход оперативной памяти соединен с управляющим входом первого мультиплексора, выход второго триггера соединен с первым информационным входом шинного формирователя, отличающееся тем, что, с целью увеличения быстродействия, оно содержит пятый, шестой и седьмой элементы И, третий элемент ИЛИ, регистр, третий и четвертый триггеры, элемент задержки, второй мультиплексор, шифратор, причем первые входы пятого и шестого элементов И подключены к входу устройства для подключения к выводу команды вывода шины управления, микроЭВМ, третий выход дешифратора адреса соединен с вторым входом пятого элемента И, выход которого соединен с входом синхронизации, регистра, выход которого соединен с первым информационным входом второго мультиплексора, выход которого соединен с информационными входами шифратора, вход разрешения которого соединен с вторым выходом оперативной памяти, выходы шифратора соединены с информационными входами первого мультиплексора, стробирующий вход которого соединен с выходом генератора тактовых импульсов, первый вход седьмого элемента И соединен с входом устройства для подключения к выводу команды ввода шины управления микроЭВМ, четвертый выход дешифратора адреса соединен с вторыми входами шестого и седьмого элементов И, выходы которого соединены с входами сброса и установки третьего триггера, выход которого соединен с входами управления второго мультиплексора, информационные входы регистра соединены с выходами шинного формирователя, вход сброса устройства соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом сброса первого триггера, второй вход второго элемента ИЛИ соединен с выходом элемента задержки и входом установки четвертого триггера, вход которого соединен с третьим выходом оперативной памяти, вход сброса четвертого триггера соединен с выходом четвертого элемента И и с входом сброса счетчика, выход четвертого триггера соединен с вторым информационным входом шинного формирователя, второй информационный вход второго мультиплексора и третий информационный вход шинного формирователя соединен с входом устройства для подачи дискретных сигналов.

Авторы

Даты

1994-02-15—Публикация

1990-12-17—Подача