и

:

U

СЛ

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих микроэвм

Целью изобретения является повышение быстродействия устройства за. счет ускоренного формирования адресов при последовательных обращениях к ячейкам, расположенным внут- ри страницы.

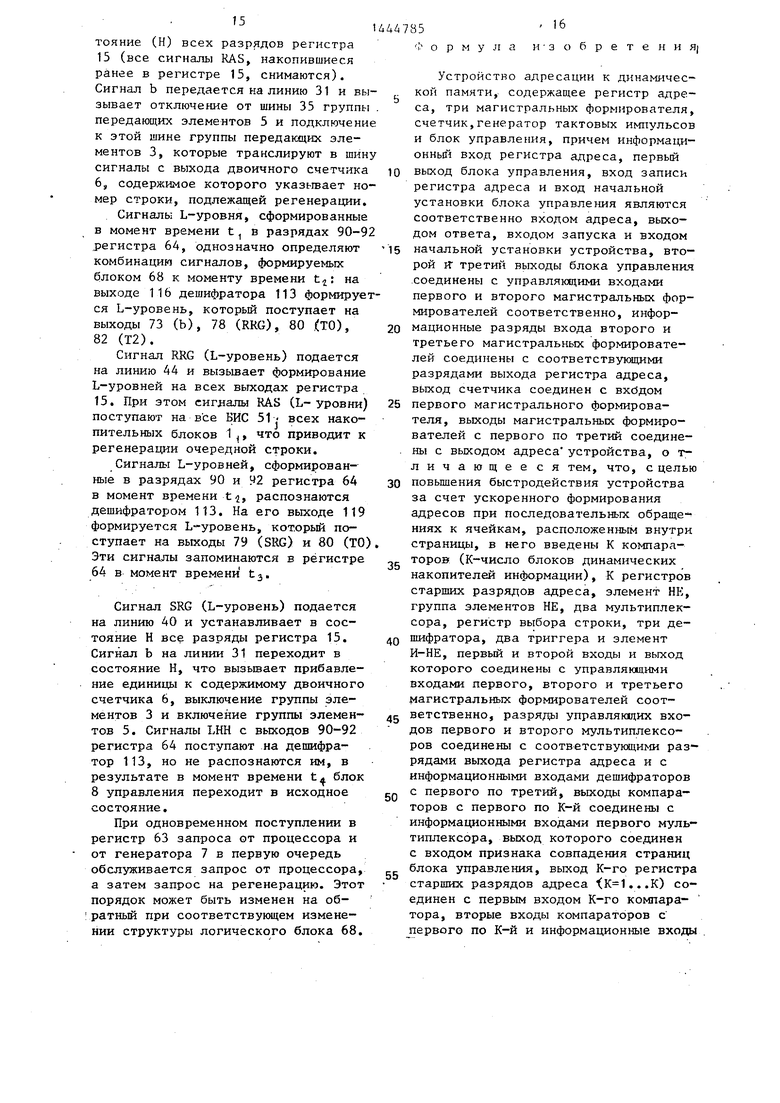

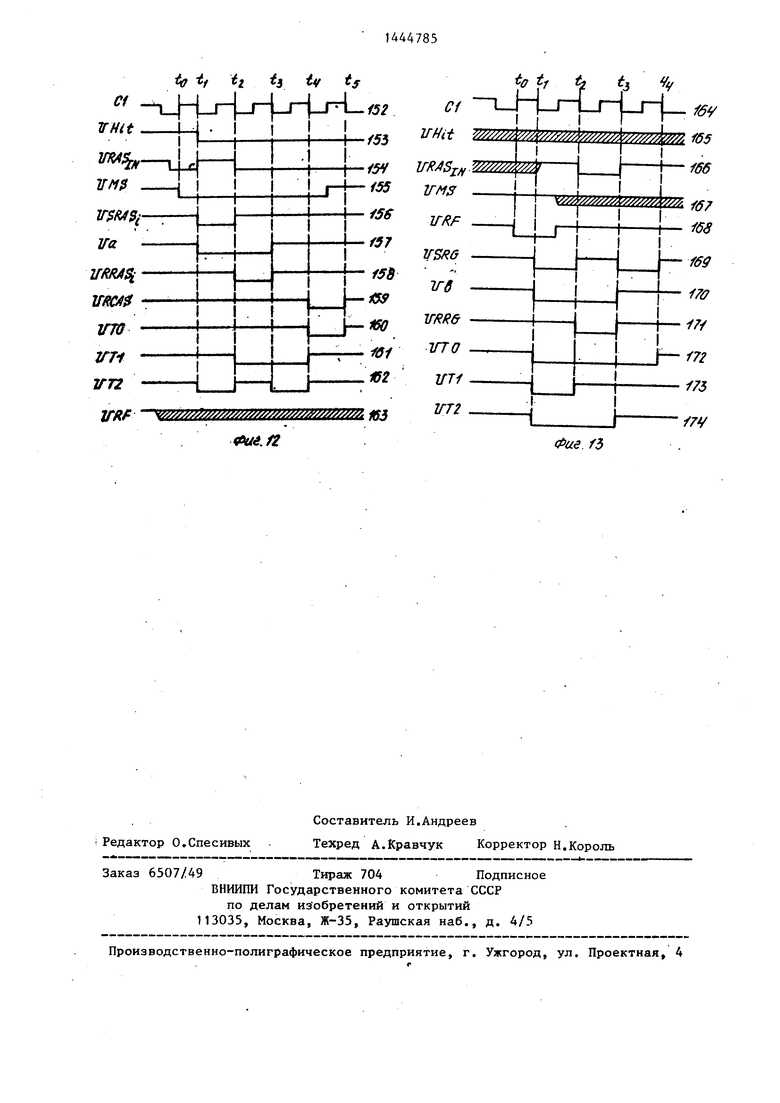

На фиг.1 приведена функциональная схема устройства; на фиго2 - пример реализации накопительного блока; на фиг.З - пример реализа- ции регистра выбора строки; на фиг,4 пример реализации блока управления; на фиг.5 - пример реализации логического блока; на фиг„6 - пример расположения адресного пространства; на фиг.7 - временные диаграммы работы динамических элементов памяти; на фиг.З - временная диаграмма регенерации данных; на фиг.9, 10 - временные диаграммы работы элементов памяти в режимах страничной записи и считывания; на фиг.11, 12 и 13 - временные диаграммы работы блока управления в режимах сокращенного цикла, полного цикла и при регенерации данных.

Устройство (фиг.1) содержит п накопительных блоков 1 - 1 (п далее принято равным 8), регистр 2 адреса, магистральные формирователи 3,..5, двоичный счетчик 6, генератор 7 импулвсов, блок 8 управления, а также п компараторов 9 -9, п регистров 101- 10(,;, старших разрядов адреса, группу п элементов НЕ 11, - 11, элемент НЕ 12, мультиплексоры 13, 14, регистр 15 выбора строки, дешифраторы 16,..18, триггеры 19,20 и элемент И-НЕ 21, вход 22 адреса устройства, вход 23 выборки последо- вательных блоков, информационньм вход 24 накопительных блоков, информационный выход 25 накопительных блоков, первый выход 26 блока управления, выход 27 ответа устройства, вхо 28 запуска устройства, входы 29 и 30 начальной установки блока 8 управления и устройства соответственно, первый 31 и второй 32 выходы блока управления, группу 33 старших и группу 34 младиих разрядов адреса,, выход 35 адреса устройства, группу 36 управляющих разрядов регистра адреса, вход 37 признака совпадения страниц

0 0

5 0

0

блока 8, четвертый 38, пятый 39 и шестой 40 выходы блока управле)шя, третий вход 41 признака запроса на регенерацию памяти и вход 42 запроса на обслуживание процессора блока 8 управления, информационные входы 43 первого и второго триггеров, седьмой выход 44 блока управления, выход 45 выбора строки устройства, входы 46 выбора строки накопительных блоков, Егход 47 признака наличия сигнала в .г- борки строки блока 8 управления,выход 48 выбора столбца устройства.

Выходы дешифратора 16 соединены с индивидуальными входами 48,- 48 выбора столбца п накопительных блоков IT - , Выходы дешифратора 17 соединены с разрядными входами 49 установки в нуль регистра 15. Выходы дешифратора 18 соединены с разрядными входами 50 установки единицы регистра 15 и с входами элементов НЕ 11,, выходы которых соединены с управляющими входами регистров 10,- Юп.

Накопительный блок 1 .(,2,...n), показанньй на фиг.2, содержит m БИС запоминающих устройств 51 ,-51 „(та - разрядность слов, хранимых в ОЗУ). БИС 51j (,2,..„,m) содержит группу адресных входов 52, соединенных с группой адресных входов 35 блока 1, вход записи 53 соединенный с входом 23 блока 1., вход 54 выбора строки, соединенный с входом 46 блока 1., вход 55 выбора столбца, соединенный с входом 48 блока 1,., вход 56 данных, входящий в состав группы входов 24 блока 1., выход 57 данных, входящий в состав группы выходов 25 .блока 1,,- о

Регистр 15 сигналов выбора строки Б приведенном на фиг.З примере () содержит элементы И 58, 59 и регистр 60, состоящий из триггеров 61. Входы 50 регистра соединены с первыми входами элементов И 58, вторые входы которых соединены с входом 44 регистра 15. Входы 49 регистра 15 соединены с первыми входами элементов И 59, вторые входы которых соединены с входом 40 регистра 15. Выходы элементов И 58 и 59 соединены с входами установки единицы и нуля триггеров 61 регистра 60, выходы которого являются выходами 45 регистра 15.

Блок 8 управления (фиг.4) содер- жит генератор 62 импульсов, входной

регистр 63, выходной регистр 64,: элементы И 65, 66, элемент НЕ 67 и логический блок 68. Первый вход 69 логического блока 68 соединен с входом 37 блока 8 управления, второй 70 и третий 71 входы блока 68 соединены с выходами первого и второго разрядов входного регистра 63, Четвертьй вход 72 блока 68 соединен с входом 47 блока 8. Первый - десятый 73 - 82 выходы логического блока 68 соединены с информационными входами первого - десятого 83 - 92 разрядов выходного регистра 64.

Выходы восьмого - десятого 90-92 разрядов выходного регистра 64 соединены с пятым - седьмым 93-95 входами логического блока 68. Выходы первого - седьмого 83-89 разрядов выходного регистра 64 соединены соответственно с выходами 31,32 блока 8, с первым входом элемента И 65, с выходами 38, 39,44 блока 8 и с первым входом элемента И 66, выход которого соедийен с выходом 40 блока 8. Выход.элемента И 65 соединен с выходом 26 блока 8.

Информационные входы первого и второго разрядов входного регистра 63 соединены с входами 42 и 41 блока 8. Вход 29 блока 8 соединен с входами установки единицы регистров 63,64 и с вторыми входами элементов И 65, 66. Выход генератора 62 импульсов соединен с входом синхронизации регистра 63 и с входом элейен- та НЕ 67, выход которого соединен .с входом синхронизации регистра 64.

Блок 68 может быть выполнен в виде ПЗУ, Ш1М или комбинационной схемы из стандартных логических элементов, как показано в примере, приве-; денном на фиг.5, где блок 68 содержит элементы НЕ 96-100, элементы И-НЕ 101-104, элементы И 105-112 и дешифратор 113..

Вход 69 блока 68 соединен с входом элемента НЕ 96, выход которого соединен с первыми входами элементов И-НЕ 101 и 102. Вход 70 блока 68 соединен с первым входом элемента И- НЕ 104 и с входом элемента НЕ 97, выход которого соединен с вторым входом элемента И-НЕ 102 и с первым входом элемента И-НЕ 103. Вход 71 блока 68 соединен с входом элемента НЕ 99, выход которого соединен со вторым входом элемента И-НЕ 104. Вхо

0

5

0

72 блока 68 соединен с входом элемента НЕ 98, выход которого соединен с вторым входом элемента И-НЕ 101 и с третьим входом элемента И-НЕ 102. Входы 93-95 блока 68 соединены с информационными входами дешифратора 113. Выход 114 дешифратора 113 соединен с входом элемента НЕ 100, вьг- ход которого соединен с третьим входом элемента И-НЕ 104, с вторым входом элемента И-НЕ 103 и с четвертым входом элемента И-НЕ 102. Выход 115 дешифратора 113 соединен с первым входом элемента И 105, второй вход которого соединен с выходом элемента И-НЕ 102, а выход - с выходом 75 блока 68 и с первым входом элемента И 106, выход которого соединен с выходом 80 блока 68. Выход 116 дешифратора 113 соединен с выходом 78 блока 68 и с первыми входами элементов И 108 и 112.

Выход 117 дешифратора 113 соеди- 5 нен с выходом 76 блока 68 и с первыми входами элементов И 109 и 111. Выход 118 дешифратора 113 соединен с первым входом-элемента И 110, второй вход которого соединен с выходом элемента 0 И-НЕ 104, с вторым входом элемента И 108 и с первым входом элемента И 107, второй вход которого соединен с выходом 119 дешифратора и с вторым входом элемента И 106, третий вход которого соединен с выходом элемента И 108 и с выходом 73 блока 68.

Выход элемента И-НЕ 101 соединен с третьим входом элемента И-НЕ 103, выход которогоо соединен с-выходом 77 блока 68, с вторыми входами элементов И 109, 112, выходы которых соединены с выходами 74 и 82 блока 68« Выход элемента И 110 соединен с третьим входом элемента И 112 и с вторым входом элемента И 111, выход которого соединен с выходом 81 блока 68. Выход элемента И 107 соединен с выходом 79 блока 68.

Эпюра 120, приведенная на фиг.6, показьшает возможный вариант распределения адресного простр|анства ОЗУ между накопительными блоками 1 (). адресов, обозначенные через ВО, соответствуют ячейкам па- . мяти, размещенным в блоке 1-,, зоны В1 соответствуют блоку и т.д., зоны В7 соответствуют Ц.

Эпкры 121-125, приведенные на фиг.7а, соответствуют режиму записи

5

0

5

0

5 14447856

бита данных в БИС запоминающего уст- ра 171 - сигнал RRG на выходе разряройства 51j (,2,...,m), см.фиг.2,да 88 регистра 64.

Эпюры 126-130, приведенные на фиг.76,Устройство работает-следугадим

соответствуют режиму считывания битаg образом.

из БИС 51joРабота процессора ЭВМ,с памятью

Эпюры 131 и 132 (фиг.В) соответст-характеризуется тем, что адреса

вуют режиму регенерации информацион-ячеек, к которым обрап;ается процесных битов, хранимых в строке нако-сор, не являются случайными, а группительной матрицы, размещенной внут-ю пируются в некоторые множества, от- ри БИС 51.

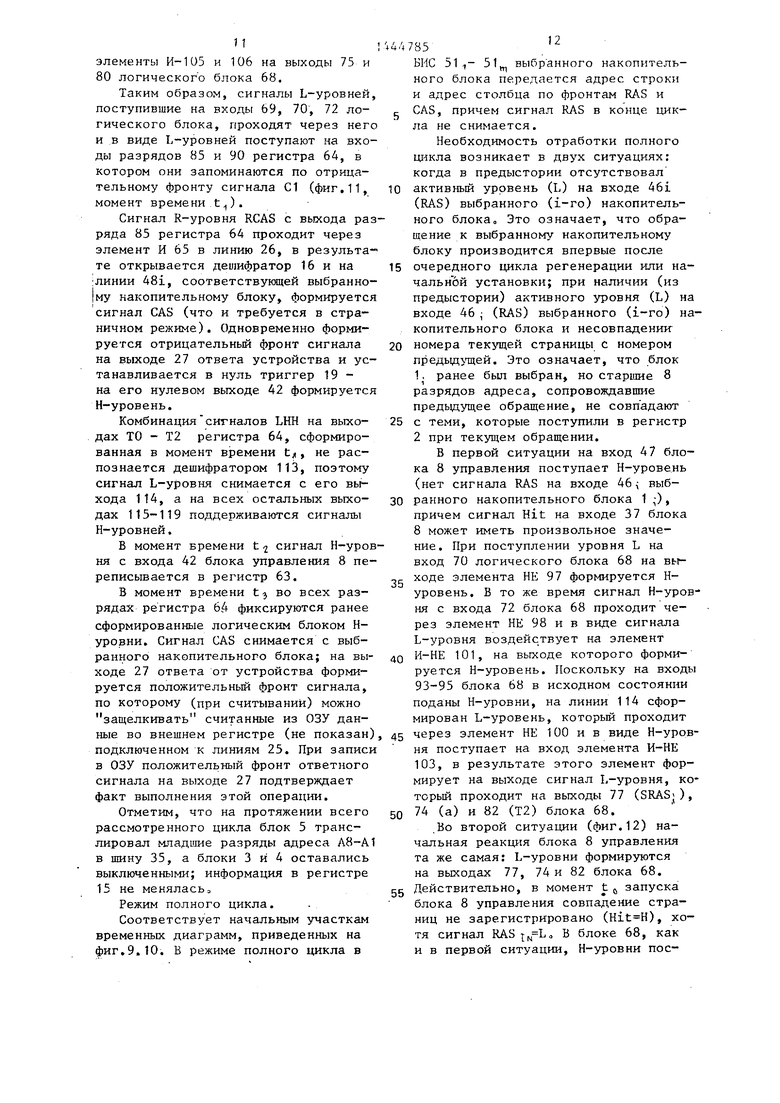

Эпюры 133-137, приведенные на фиг.9, соответствуют страничному режиму записи; эпюры 138-142 (фиг.10)страничному режиму считывания инфор-is всего не разбросаны по памяти,

мации из БИС 51 j.а сосредоточены в виде о дного или

Эг1юры 121, 126, 131, 133, 138нескольких массивов.

отображают сигнал KAS на входе 54Области памяти Р1, Р2 и РЗ, как

БИС 51J; эпюры 122, 12/, 134, 139 -предполагается, представляет собой

сигнал CAS на входе 55 БР1С 51 j; эшсг-20 область программы, область локальры 123, 128, 132, 135, 140 - адрес-ных данных и область глобальных данносительно стабильные во времени. Это связано с тем, что программы имеют циклический характер, а данные, которыми оперирует процессор, чаще

ные сигналы А на входах 52 БИС 51j; эпюры 124, 129, 136, 141 - сигнал записи WR на входе 53 БИС 51j; эпюры 125, 137 - сигнал входных данных Dj на входе 56 БИС 51j; эпюры 130, 142- сигнал выходных данных 1) на выходе 57 БИС 51j.

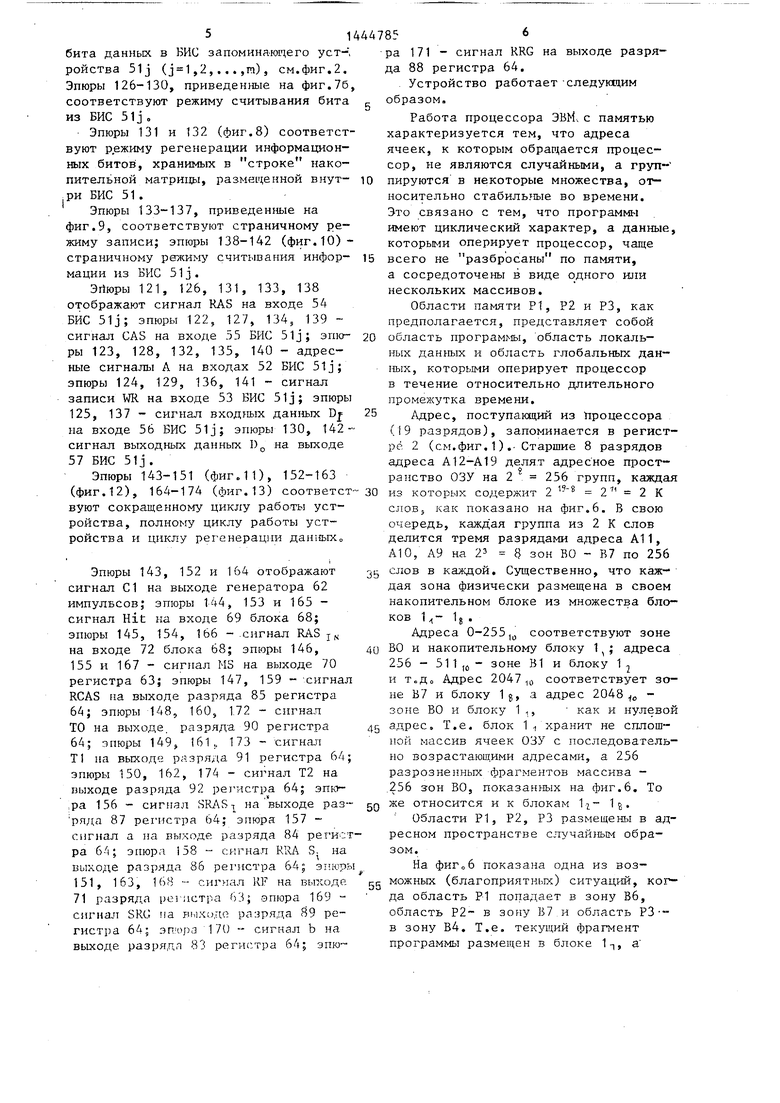

Эпюры 143-151 (фиг.11), 152-163

25

ных, которыми оперирует процессор в течение относительно длительного промежутка времени.

Адрес, поступающий из Процессора (19 разрядов), запоминается в регистре 2 (см.фиг.1),. Старшие 8 разрядов адреса А12-А19 делят адресное просто

ранство ОЗУ на 2 . 256 групп, каждая

(фиг.12), 164-174 (фиг.13) соответст- 30 из которых содержит 2 2 К

пируются в некоторые множества, от-

носительно стабильные во времени. Это связано с тем, что программы имеют циклический характер, а данные, которыми оперирует процессор, чаще

ных, которыми оперирует процессор в течение относительно длительного промежутка времени.

Адрес, поступающий из Процессора (19 разрядов), запоминается в регистре 2 (см.фиг.1),. Старшие 8 разрядов адреса А12-А19 делят адресное просто

ранство ОЗУ на 2 . 256 групп, каждая

из которых содержит 2 2 К

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления виртуальной памятью | 1986 |

|

SU1327113A2 |

| Устройство управления виртуальной памятью | 1980 |

|

SU1023336A1 |

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| КОНТРОЛЛЕР ПАМЯТИ, КОТОРЫЙ ВЫПОЛНЯЕТ КОМАНДЫ СЧИТЫВАНИЯ И ЗАПИСИ НЕ В ПОРЯДКЕ ПРОСТОЙ ОЧЕРЕДИ | 1996 |

|

RU2157562C2 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

| Устройство для трансляции логических адресов в адреса памяти на магнитных дисках | 1981 |

|

SU966695A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Запоминающее устройство | 1984 |

|

SU1243033A1 |

Изобретение относится к вычислительной технике и мсясет быть использовано при построении быстродействующих микроэвм. Целью изобретения является повышение быстродействия устройства за счет ускоренного формирования адресов при последовательных обращениях к ячейкам, расположенным внутри страницы. При обращении к накопительным блокам и совпадении номеров текущей и предыщущей страниц выполняется режим ускоренного (страничного) доступа к ячейке. При этом время доступа к ячейке сокращается вдвое. 13 ил.

вуют сокращенному циклу работы устройства, полному циклу работы устройства и циклу регенерации дангыХо

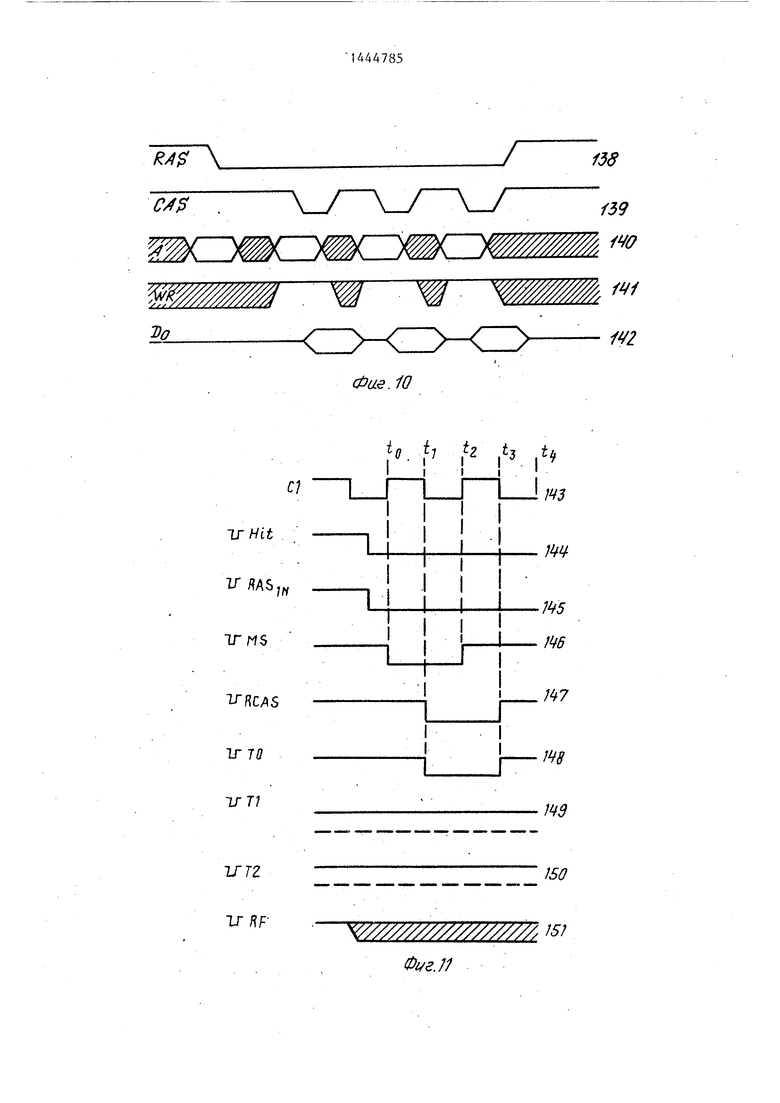

Эпюры 143, 152 и 164 отображают сигнал С1 на выходе генератора 62 импульсов; эпюры 144, 153 и 165 - сигнал Hit на входе 69 блока 68; эпюры 145, 154, 166 - сигнал RAS j . на входе 72 блока 68; эпюры 146, 155 и 167 - сигнал MS на выходе 70 регистра 63; эпюры 147, 159 - -сигна RCAS на выходе разряда 85 регистра 64; эпюры 148, 160, 1,72 - сигнал ТО на выходе, разряда 90 регистра 64; эпюры 149, 161,, 173 - сигнао Т1 на выходе разряда 91 регистра 64 эпюры 150, 162, 174 - сигнал Т2 на выходе разряда 92 рет истра 64; эпю.ра 156 - сигнал SRAS-j на выходе раз- 50 - относится и к блокам 1g.

ряда 87 регистра 64; эпюра 157 - Области Р1, Р2, РЗ размещены в ад- сигнал а на выходе разряда 84 регист- ресном пространстве случайным обра- ра 64; эпюра 158 - сигнал RRA S. на зом. выходе разряда 86 регистра 64; эпюры.

На фиГоб показана одна из воз151, 163, 168 - сигнал IF на выходеgg можных (благоприятных) ситуаций, козг71 разряда регистра 63; эпюра 169 - да область Р1 поцадает в зону Вб, сигнал SRG tia выхиде разряда 89 ре- область Р2 в зону В7 и область РЗ- гистра 64; эп,ч)ра 170 - сигнал b на в зону В4. Т.е. текуьций фрагмент выходе разряди 83 регистра 64; эпю™ программы размещен в блоке 1-,, а

слоБз как показано на фиг.6. В свою очередь, каждая группа из 2 К слов делится тремя разрядами адреса А11, А10, А9 на 23 § зон ВО - В7 по 256

слов в каждой. Существенно, что каждая зона физически размещена в своем накопительном блоке из множества блоков 1 - 1j .

Адреса 0-255, соответствуют зоне

ВО и накопительному блоку 1,; адреса 256 - 51 1 ,5 - зоне В1 и блоку 1 и ТоДо Адрес соответствует зоне Б7 и блоку 1j, а адрес 2048 зоне ВО и блоку 1 ,, - как и нулевой

адрес. Т.е. блок 1 хранит не сплошной массив ячеек ОЗУ с последовательно возрастающими адресами, а 256 разрозненных фрагментов массива - 256 зон ВО, показанных на фиг.6, То

Области Р1, Р2, РЗ размещены в ном пространстве случайным обра .

На фиГоб показана одна из возданные, которыми она оперирует, - в блоках In и 1с. Такое или иное .

t) бесконфликтное попадание областей Р1, Р2 и РЗ в блоки 1i - Ig обеспечивает каксимальньш выигрыш в быстродействии. С другой стороны, выигрыш полностью отсутствует,. если области Р1, Р2 и РЗ попадают в один и тот же блок из ряда 1,- Ig. Однако вероят- ность такой ситуации невелика:

1

Т

L

8

5Т2

. С учетом наличия восьми равно- правных блоков 1 - 1 вероятность одновременного попадания областей Р1, Р2 и РЗ в один из блоков ряда 1 - .1 g в восемь раз большая:

1

64

При;;наличии конфликтов между двумя областями трех быстродействие теряется только при строго попере- менных обращениях процессора к конкурирующим областям.

При бесконфликтном отображении областей Р1, Р2 и РЗ на блоки 1,- 1j оказывается возможным использовать одновременно в трех соответствующих блоках режимы страничной записи и считывания, описанные ранее (см. фиг,9, 10), при которых вреачя достзг- па к ячейкам памяти сокращается.

После совершения очередного цикла регенерации (см.фиг.8) устройство переходит в исходное состояние, при котором сигналы RA.S, CAS, поступаю) щие на всё БИС 51j всех блоков Ij, принимают пассивное значение (Н).

При первом (после регенерации) обращении .процессора в область Р1(Р2, РЗ) на входах блока ,( ч 1j) формируется пара сигналов RAS- CAS, причем сигнал RAS не снимается, а номер страницы (разряды А12-А19, группа 33) запоминается в регистре lOvdOj, 10,,)о Т.е. при первом обращении реализуется начальный учас- ток временной диаграммы, приведенной на фиг.9 или фиго 10 с запоминанием текущего номера страницы. При последующем обращении процессора в область Р1 (Р2, РЗ) компаратор ) (9g, 9j) регистрирует совпадение поступившего номера страницы с ранее использованнымо Это означает, что создались УСЛОВИЯ для продолQ

5

0

5

0 g

0

5 0 g

жения начатого ранее страничного ре- жима работы выбранного накопительного блока (см.фиг.9,10) Поэтому с помощью блока 8 управления и дешифратора 16 вырабатывается импульсный сигнал CAS, поступающий в блок 1-;(8 s) сигнал RAS, поступающий в. блок lyds 1) по-прежнему остается в активном состоянии (L),

А течение промежутка времени между циклами регенерации (16.мкс) процессор многократно, в нужной ему последовательности обращается к области программы изданных (Р1, Р2 и РЗ); при этом в блоках 1:,, Ig и 1 реализуются режимы страничной . записи и считывания.

Если номер текущей страницы при обращении к блоку { , 1j) не совпадает с ранее принятым на регнстр 10т(105, lOj), то блок В управления формирует последовательность сигналов, обеспечивающих снятие сигнала RAS с входа 46 7(46 j, 465) с последующей отработкой процедуры первого обращения к ячейке памяти-в страничном режиме (см.начальные участки временных диаграмм приведенных на фиг.9 и 10jl При этом номер первой страницы запоминается в регистре 107(103, 165) в расчете на то, что в дальнейшем можно будет продолжить работу в страничном режиме. При обработке очередного запроса на регенерацию устройство возвращается в пассивное состояние, при котором, в частности, ранее накопленные в регистре 15 сигналы RAS переходят в состоярше Н.

Устройство приводится в исходное состояние при поступлении L-уровня на вход 30 начальной установки (см« фиг.1); при этом на входы 23 и 28 поданы Н-уровни. Сигнал с входа 30 устройства поступает на вход 29 блока 8 управления и далее (см.фиг.4) устанавливаются в единичное состояние регистры 63 и 64, на выходах которых устанавливаются Н-уровни. В то же время сигнал сброса (L) воздей-г ствует на входы элементов И 65 и 66 и передается на их выходы, что приводит к сбросу триггеров 19, 20 (на их нулевых выходах устанавливаются Н-уровни) и к установке всех разря-t дов регистра 15 в единичные состояния (Н-уровни на выходах)о На время действия сигнала сброса открьгоается

дешифратор 16 и на один из блоков 1j поступает сигнал CAS, что.

однако, не может привести к искажению хранимой в блоке информации, поскольку на входе 23 (WR) присутст вует Н-уровеньо Начальная установка устройства завершается снятием L- уровня с входа 30.

Устройство работает в трех режи- мах: сокращенного цикла, полного цикла и регенерации.

Режим сокращенного цикла.

Соответствует рассмотренной, ранее благоприятной ситуации, когда текущий номер страницы совпадает с предьщущим, что позволяет продол- жать отработку ранее начатой процедуры страничного обращения (смофиг Э 10).

При обращении к ОЗУ на адресных входах 22 устройства устанавливается 19-разрядный код адреса ячейки, к которой будет производиться доступ. В режиме считывания на входе 23 уста навливается Н-уровень, в режиме записи - L-уровень, а записьшаемые данные (га-разрядное слово) подаются на входы 24., На входе 28 пока присуттвует Н-уровень.

Регистр 2 при наличии Н-уровня на входе 28 транслирует код с входов 22 на выходы 33, 34, 36. Разряды All А10, А9 адреса содержат информацию о номере накопительного блока 1 о который будет активизирован. С помощью этих разрядов мультиплексор 13 настраивается на передачу в точку 37 сигнала с выхода одного из компараторов 9 -, соответствующему блоку 1 - j к которому будет производиться обращение.

Компаратор 9 ,- сравнивает номер страницы, поступаютий с линий 33, с

номером, хранимым в регистре 10- (из предыстории), В рассматриваемом режиме номера указанных страниц совпадают, так что в точке 37 устанавливается L-уровень. Это первое необходимое условие выполнения сокращенного цикла, которое проверяется блоком 8 управления.

Второе необходимое условие, при котором возможно выполнение сокращенного цикла, является наличие (из предыстории) активного уровня (L) на входе 46 (RAS) выбранного накопительного блока. Это условие такг же проверяется блоком 8 управления.

1444785

на вход 47 которого поступает информация о состоянии выбранного мультиплексором 14 сигнала RAS. Мультиплексор 14 выбирает нужный сигнал RAS с выхода регистра 15, который отражает предь:сторию работы блоков

1 : те блоки, к которым ранее производилось обращение, помещены в регистре 15 сигналами L-уровня, а невостребованные блоки - сигналами Н-уровня.

Таким образом, на начальном этапе работы устройства в режиме сокращенного цикла на входах 37 и 47 блока 8 управления присутствуют L-уровни, .а на входах 29, 41 и 42 - Н-уровни (пока предполагается, что запрос на регенерацию в линии 41 отсутствует).

После окончания переходных процессов в точках 37 и 47 на вход 28 (MS) устройства поступает сигнал L-уровня, подтверждающий истинность информации, ранее установленной на входах 22,23 и, если выполняется операция запи- си, - на входах 24. Сигнал L-уровня на входе 28 защелкивает в регистре 2 информацию, которая .ранее через него транслировалась, и, пройдя через элемент НЕ 12, переводит триггер 19 в единичное состояние, при котором на его нулевом выходе 42 формируется активный сигнал (L) запроса на обслуживание процессора.

По положительному фронту сигнала 01 с выхода генератора 62 (см.фиг.4, 11) запрос на обслуживание процессора фиксируется в регистре 63. Начиная с этого момента времени (t) вступает в действие блок 8 управления (ранее он в каждом цикле работы подтверждал единичные состояния всех разрядов регистра 64).

При прохождении через логический

блок (фиг.5) входные сигналы L-уровня с линий 69,70 и 72 инвертируются элементами НЕ 96-98 и в виде Н-уров- ней поступают на первый - третий входы элемента И-НЕ 102. На четвер- тьй вход -этого элемента поступает Н-уровень с выхода элемента НЕ 100, на вход которого подан L-уровень с выхода 114 дещифратора 113, который в данном случае распознает комбинацию ННН на своих входах 93-95. На . выходе элемента И-НЕ 102 формируется L-уровень, которьй проходит через

11

элементы И-105 и 106 на выходы 75 и 80 логического блока 68.

Таким образом, сигналы L-уровней поступившие на входы 69, 70, 72 логического блока, проходят через него и в виде L-уровней поступают на входы разрядов 85 и 90 регистра 64, в котором они запоминаются по отрицательному фронту сигнала С1 (фиг.11, момент времени t).

Сигнал R-уровня RCAS с выхода разряда 85 регистра 64 проходит через элемент И 65 в линию 26, в результате открывается дешифратор 16 и на линии 481, соответствующей выбранному накопительному блоку, формируется сигнал CAS (что и требуется в страничном режиме). Одновременно формируется отрицательный фронт сигнала на выходе 27 ответа устройства и устанавливается в нуль триггер 19 - на его нулевом выходе 42 формируется Н-уровень.

Комбинация сигналов LHH на выходах ТО - Т2 регистра 64, сформированная в момент времени tj,, не распознается дешифратором 113, поэтому сигнал L-уровня снимается с его выхода 114, а на всех остальных выходах 115-119 поддерживаются сигналы Н-уровней.

Б момент времени t 2 сигнал Н-уров ня с входа 42 блока управления 8 переписывается в регистр 63.

В момент времени tj во всех разрядах регистра 64 фиксируются ранее сформированные логическим блоком Н- уровни. Сигнал CAS снимается с выбранного накопительного блока; на выходе 27 ответа от устройства формируется положительный фронт сигнала, по которому (при считываний) можно защелкивать считанные из ОЗУ данные во внешнем регистре (не показан) подключенном к линиям 25. При записи в ОЗУ положительный фронт ответного сигнала на выходе 27 подтверждает факт выполнения этой операции.

Отметим, что на протяжении всего рассмотренного цикла блок 5 транслировал младшие разряды адреса А8-А1 в шину 35, а блоки 3 и 4 оставались выключенными; информация в регистре 15 не менялась о

Режим полного цикла.

Соответствует начальным участкам временных диаграмм, приведенных на фиг.9.10. В режиме полного цикла в

/4785

БИС 51,- 51 выбранного накопительного блока передается адрес строки и адрес столбца по фронтам RAS и

с- CAS, причем сигнал RAS в конце цикла не снимается.

Необходимость отработки полного цикла возникает в двух ситуациях: когда в предыстории отсутствовал

0 активный уровень (L) на входе 461 (RAS) выбранного (1-го) накопительного блока. Это означает, что обращение к выбранному накопительному блоку производится впервые после

5 очередного цикла регенерации или начальной установки; при наличии (из предыстории) активного уровня (L) на входе 46 j (RAS) выбранного (i-го) накопительного блока и несовпадении

0 номера текущей страницы с номером предыдущей. Это означает, что блок 1, ранее был выбран, но старшие 8 разрядов адреса, сопровождавщие предыдущее обращение, не совпадают

5 с теми, которые поступили в регистр 2 при текущем обращении.

В первой ситуации на вход 47 блока 8 управления поступает Н-уровень (нет сигнала RAS на входе 46 выб0 ранного накопительного блока 1 ), причем сигнал Hit на входе 37 блока 8 может иметь произвольное значение. При поступлении уровня L на вход 70 логического блока 68 на вьт- ходе элемента НЕ 97 формируется Н- уровень. В то же время сигнал Н-уровня с входа 72 блока 68 проходит через элемент НЕ 98 и в виде сигнала L-уровня воздейс твует на элемент

0 И-НЕ 101, на выходе которого формируется Н-уровень. Поскольку на входы 93-95 блока 68 в исходном состоянии поданы Н-уровни, на линии 114 сформирован L-уровень, который проходит

5 через элемент НЕ 100 и в виде Н-уров- ня поступает на вход элемента И-НЕ 103, в результате этого элемент формирует на выходе сигнал L-уровня, который проходит на выходы 77 (SRAS;),

0 74 (а) и 82 (Т2) блока 68.

Во второй ситуации (фиг.12) начальная реакция блока 8 управления та же самая: L-уровни формируются на выходах 77, 74 и 82 блока 68.

5 Действительно, в момент t запуска блока 8 управления совпадение страниц не зарегистрировано (), хотя сигнал RAS В блоке 68, как и в первой ситуации, Н-уровни пос5

тупают на все входы элемента И-НЕ 10 что приводит к формированию сигналов L-уровня на выходах SRAS;, а и Т1 (см.фиг.12, момент времени t ,) Сигнал L-уровня а с выхода 32 блока 8 проходит через элемент И- НЕ 21 и выключает блок 5 передающих элементов, вместо которого включается блок 4, который транслирует в шину 35 старшие разряды адреса А19- А12. В то же время сигнал L-уровня с выхода 39 (SRAS) блока 8 управления открывает дешифратор18, который формирует сигнал установки единицы выбранного разряда регистра 15 Сигнал RAS на входе 46 i выбранного блок I. переходит в состояние Н, если он находился в состоянии L (вторая ситуация из рассмотренных выше); если же он уже находился в состоянии Н (первая ситуация),то его состояние не изменяется. Сигнал L-уровня с выхода дешифратора 18, кроме того, передается через элемент НЕ 11; на управляющий вход регистра 10 ;, кото- рьй открывается по входам, готовясь в дальнейшем зафиксировать номер новой страницы. При этом компаратор 9; регистрирует совпадение кодов, что, однако, уже не влияет на дальнейшую последовательность микрокоманд, генерируемых блоком 8 управ- ле ния.

Информация, зарегистрированная в разрядах 90-92 регистра 64 в момент времени t ,(HHL), однозначно определяет дальнейшее поведение блока 8. Действительно, указанная комбинация распознается дешифратором 113, в результате на его выходе 117 формируется L-уровень, который проходит на выходы 74 («), 76 (RRAS) и 81 (Т1), см.фиг.12, момент времени В момент времени ti устанавливается в состоянии L выбранный дешифратором 17 i-й разряд-регистра 15, в результате на выбранный блок 1 . подается сигнал HAS (L-уровень), а регистр 9; защелкивает старшие разряды адреса, поскольку на выходе элемента НЕ 11 ; установился L-урове

Комбинация HLH в разрядах ТО, Т1 Т2 регистра 64 опознается дешифратором 113, на выходе 118 которого формируется L-уровень, который проходит на выходы 81 (Т1) и 82 (Т2)

блока 68. В момент времени t -j эта кодовая комбинация фиксируется в регистре 64. Сигнал л принимает значение Н, что приводит к включению группы передающих элементов 5 и к выключению группы 4 (приведена подготовка к передаче младших разрядов адреса в БИС 51 ,-51 выбранного накопительного блока 1.).

Комбинация HLL вызывает формирование L-уровня в линии 115, который проходит на выходы 75 (RCAS) и 80 (то) блока 68 и фиксируется в регистре 64 в момент времени t. При этом открывается дешифратор 16 и производится выдача сигнала CAS (L-ypoB- нем) на выбранньй накопительный блок. На выходе 27 формируется ответный

сигнал, триггер 19 устанавливается в О.

Комбинация LHH, сформированная в разрядах ТО, Т1, Т2 регистра 64 в момент времени t.,, не распознается

дешифратором 113, поэтому.в момент времени t § на всех выходах блока 8 управления формируются Н-уровни, т.е. устройство переходит в исходное состояние.

Режим регенерации.

При поступлении положительного фронта сигнала с генератора 7 импульсов на вход синхронизации триггера 20 на его нулевом выходе 41 устанавливается напряжение низкого уровня - сигнал запроса на регенерацию. В момент времени t (фиг.13) запрос принимается в регистр 63. При отсутствии запроса от процессора () блок 8

управления вырабатывает последовательность сигналов, обеспечивакхцих выполнение цикла регенерации (см. фиг.8) одновременно во всех БИС 51- всех накопительных блоков 1.

В момент времени t на входы 70 и 71 блока 68 действуют сигналы Н и L, причем на выходе 114 дешифратора 113 в исходном состоянии сформирован сигнал L, поскольку на входы 93- 95 поданы Н-уровни. Это приводит к формированию L-уровня на выходе элемента И-НЕ 104, который поступает на выходы 73 (Ь), 79 (SRG), 80 (ТО), 81 (Т1) и 82 (Т2). Эти сигналы в момент времени t, фиксируются в регистре 64 „

Сигнал SRG (L-уровень) подается. на линию 40 и вы зьшает сброс тригге ра 20 и установку в единичное сос t5

тояние (Н) всех разрядов регистра 15 (все сигналы RAS, накопившиеся ранее в регистре 15, снимаются). Сигнал b передается на линию 31 и вызывает отключение от шины 35 группы передающих элементов 5 и подключени к этой шине группы передающих элементов 3, которые транслируют в шин сигналы с выхода двоичного счетчика 6, содержимое которого указьгоает номер строки, подлежащей регенерации.

Сигналы L-уровня, сформированные в момент времени t, в разрядах 90-9 .регистра 64, однозначно определяют комбинации сигналов, формируемых блоком 68 к моменту време ш на выходе 116 дешифратора 113 формируеся L-уровень, который поступает на выходы 73 (Ь), 78 (RKG), 80 ,(ТО), 82 (Т2).

Сигнал RRG (L-уровень) подается на линию 44 и вызывает формирование L-уровней на всех выходах регистра 15. При этом сиглалы RAS (L-уровни) поступают на все ВИС 51- всех накопительных блоков 1 что приводит к регенерации очередной строки.

Сигналы L-уровней, сформированные в разрядах 90 и 42 регистра 64 в момент времени t, распознаются дешифратором 113. На его выходе 119 формируется L-уровень, кот.орьй поступает на выходы 79 (SRG) и 80 (ТО Эти сигналы запоминаются в регистре 64 в момент времени t Сигнал SRG (L-уровень) подается на линию 40 и устанавливает в состояние Н все разряды регистра 15. Сигнал b на линии 31 переходит в состояние Н, что вызьшает прибавление единицы к содержимому двоичного счетчика 6, выключение группы элементов 3 и включение группы элементов 5. Сигналы LHH с выходов 90-92 регистра 64 поступают на дешифратор 113, но не распознаются им, в результате в момент времени t блок 8 управления переходит в исходное состояние.

При одновременном поступлении в регистр 63 запроса от процессора и от генератора 7 в первую очередь обслуживается запрос от процессора, а затем запрос на регенерацию. Этот порядок может быть изменен на об- ратный при соответствующем изменении структуры логического блока 68.

.

U44785

, 16 о р м у л а и 3 о б р е т е Н и Я|

5

0

5

0

5

0

5

0

5

Устройство адресации к динамической памяти, содержащее регистр адреса, три магистральных формирователя, счетчик,генератор тактовых импульсов и блок управления, причем информаци- онньй вход регистра адреса, первый вькод блока управления, вход записи регистра адреса и вход начальной установки блока управления являются соответственно входом адреса, выходом ответа, входом запуска и входом начальной установки устройства, второй и третий выходы блока управления соединены с управляющими входами первого и второго магистральных формирователей соответственно, информационные разряды входа второго и третьего магистральных формирователей соединены с соответствукяцими разрядами выхода регистра адреса, вькод счетчика соединен с вхбдом первого магистрального формирователя, выходы магистральных формирователей с первого по третий соединены с выходом адреса устройства, о т- личающее ся тем, что, с целью повьшения быстродействия устройства за счет ускоренного формирования адресов при последовательных обращениях к ячейкам, расположенным внутри страницы, в него введены К компараторов (К-число блоков динамических накопителей информации), К регистров старших разрядов адреса, элемент НЕ, группа элементов НЕ, два мультиплексора, регистр выбора строки, три дешифратора, два триггера и элемент И-НЕ, первый и второй входы и выход которого соединены с управляющими входами первого, второго и третьего магистральных формирователей соответственно, разряды управляющих входов первого и второго мультиплексоров соединены с соответствующими разрядами выхода регистра адреса и с информационными входами дешифраторов с первого по третий, выходы компараторов с первого по К-й соединены с информационными входами первого мультиплексора, выход которого соединен с входом признака совпадения страниц блока управления, выход К-го регистра старших разрядов адреса ...К) соединен с первым входом К-го компаратора, вторые входы компараторов с первого по К-й и информационные входы

7

регистров старших разрядов адреса с первого по К-й соединены с информационным входом магистрального формирователя, управлякхцие входы дешифраторов с первого по третий соединены с первыми, четвертым и пятым выхо дами блока управления, вход сброса первого триггера соединен с первым выходом блока управления, вход сброса второго триггера соединен с шестым выходом блока управления и с входом общей установки в 1 регистра выбора строки, выход генератора импульсов соединен с входом синхронизации второго триггера, инверсный выход которого соединен с входом признака запроса на регенерацию па- мя ти блока управления, вход и выход элемента НЕ соединены соответственн с управлям и-ш входом регистра адреса и входом синхронизации первого триггера, инверсный выход которого соединен с входом признака запроса на обслуживание процессора блока управления, и формационные входы первого и второго триггеров соедине

r-4Jf9{if8 k/1 rtw

31

- - IZbiJ :

-|-r---Jj/;

85

ны с входом уровня логической единицы устройства, счетный вход счет- чика соединен с вторым выходом блока управления, седьмой выход которого соединен с входом общего сброса регистра выбора строки, выход которого соединен с информационным входом второго мультиплексора и с выхо

дом выбора строки устройства, выход второго мультиплексора соединен с входом признака -наличия сигнала выбора строки блока управления, выход первого дешифратора является

выходом выбора столбца устройства, выход второго де1йИфратора соединен с входом поразрядного сброса регистра выбора строки, разряды выхода третьего дешифратора соединены с со

ответствукхцими разрядами входа поразрядной установки в 1 регистра

выбора строки и входами соответствующих элементов НЕ группы, выходы которых соединены с входами записи соответствующих регистров старших разрядов адреса с первого по К-й.

-ЗЛ,

-. . .Ги«2Ь

.«, Лг

f t Vg/7

So 25

A/h

-t

RAMD

KAftID

2

V

6

56

6ii aOti7

RAS

1Ю CAS

W

Di

57

52

5

55

ДЗ

56

5ii aO-a7

R/t

C4S

Po

WR

I

51,

L.

Of$

e/

2

. r

RAMD

52

aO-a

o

57

Sf,

5

55

53,

56

RA

% CAS

WR

5Г

35

Фие. 2

RA$

Vtfx

«jf

256 epf/лп по

ЯЛ 5

.i

Фие.6

C/l$

w

жзшошсэ

HAS

, /

i

ь

iZ9

f50

Фае 7

/

/j;

фиг. 8

f

/33

fd

fi7

Pui.9

K/l

C

f

%

f

т

f39 /447

т

Фие. 10

.П

a.fZ

Фие fb

| Патент США | |||

| 4623986, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Электромагнитная вязальная машина | 1922 |

|

SU1201A1 |

| Техническое описание, 1986, с.8.,.103. | |||

Авторы

Даты

1988-12-15—Публикация

1987-07-13—Подача