Изобретение относится к вычислительной технике и-можеТ быть использовано в качестве энергонезависимого накопителя информахщи микропроцессорной электронной вычислительной машины

Цель изобретения - повышение надежности и расширение функциональных возможностей устройства за счет обеспечения побайтовой записи и выборочного стирания данных, а также обеспе- чение возможности страничной адресации.

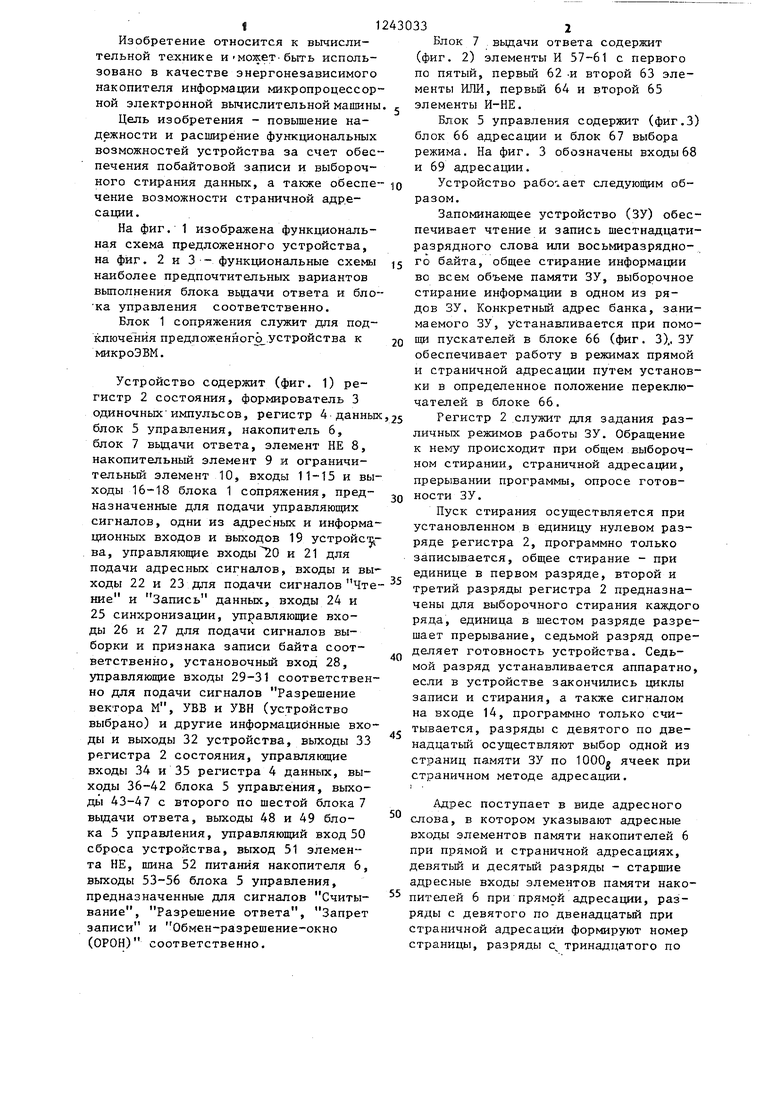

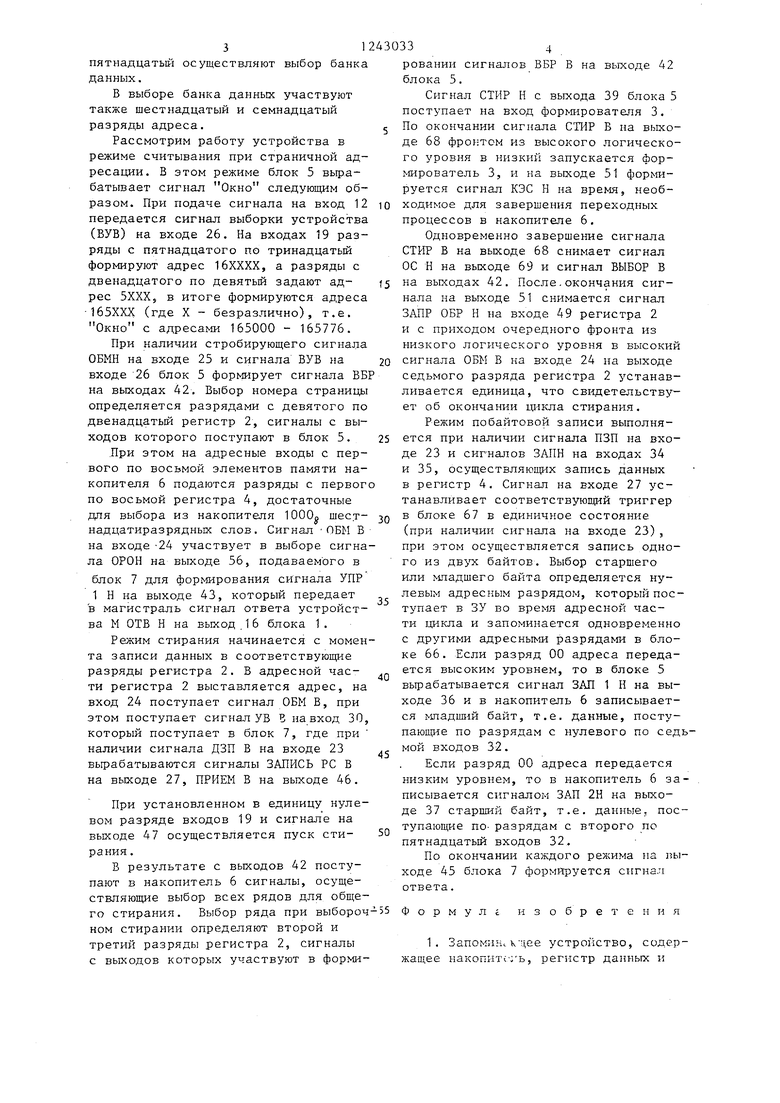

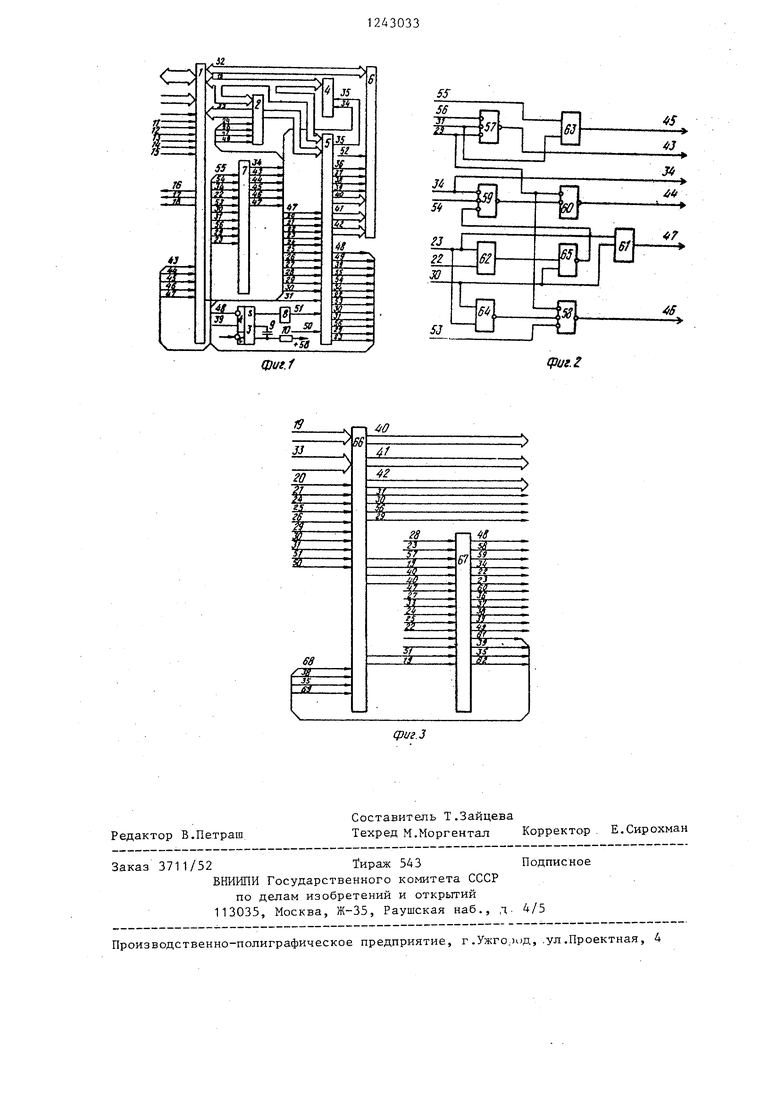

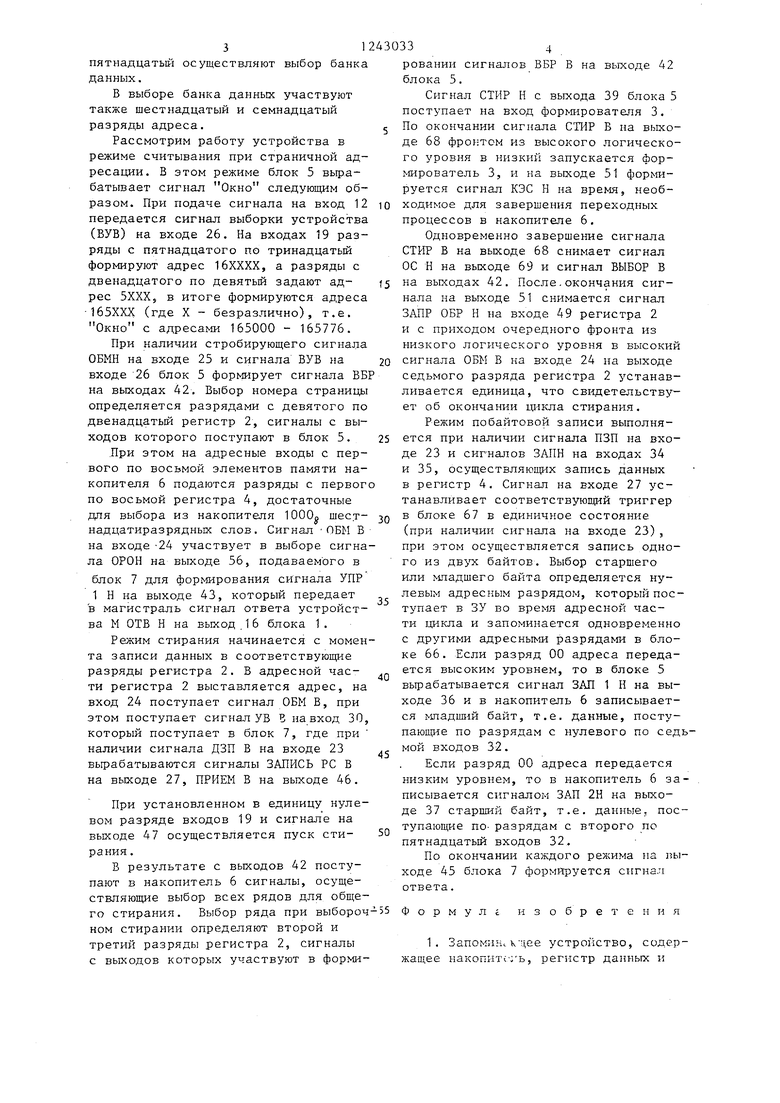

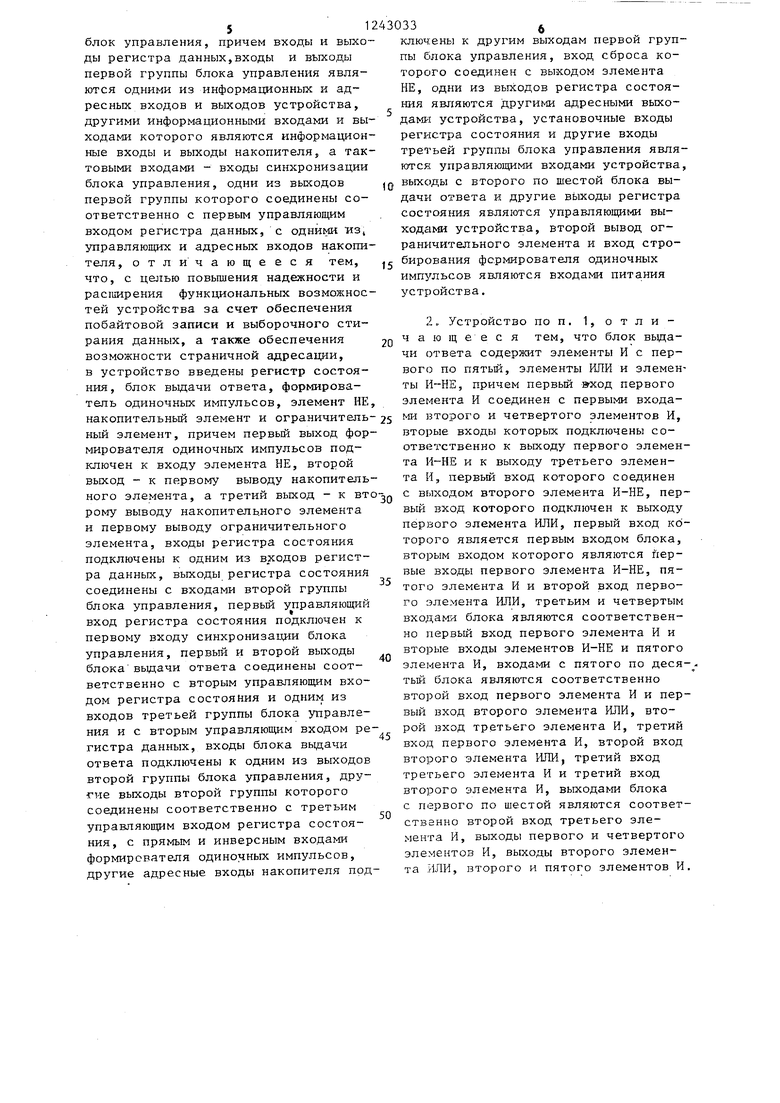

На фиг. 1 изображена функциональная схема предложенного устройства, на фиг. 2 и 3 - функциональные схемы наиболее предпочтительных вариантов выполнения блока вьщачи ответа и бло- ка управления соответственно.

Блок 1 сопряжения служит для под- ключе1€ия предложенног).устройства к микроэвм.

Устройство содержит (фиг. 1) регистр 2 состояния, формирователь 3 ОДИНОЧНЫХ импульсов, регистр 4 данных блок 5 управления, накопитель 6, блок 7 вьщачи ответа, элемент НЕ 8, накопительный элемент 9 и ограничительный элемент 10, входы 11-15 и выходы 16-18 блока 1 сопряжения, пред- назначенные для подачи управляющих сигналов, одни из адресных: и информационных входов и выходов 19 устройст;,- ва, управляющие входы 20 и 21 для подачи адресных сигналов, входы и выходы 22 и 23 для подачи сигналов Чте ние и Запись данных, входы 24 и 25 синхронизации, уп1 авляющие входы 26 и 27 для подачи сигналов выборки и признака записи байта соответственно, установочньй вход 28, управляющие входы 29-31 соответственно для подачи сигналов Разрешение вектора М, УВВ и УВН (устройство выбрано) и другие информационные входы и выходы 32 устройства, выходы 33 регистра 2 состояния, управлякнцие входы 34 и 35 регистра 4 данных, выходы 36-42 блока 5 управления, выходы 43-47 с второго по шестой блока 7 вьщачи ответа, выходы 48 и 49 бло- ка 5 управления, управляющий вход 50 сброса устройства, выход 51 элемента НЕ, шина 52 питания накопителя 6, выходы 53-56 блока 5 управления, предназначенные для сигналов Считы- вание, Разрешение ответа, Запрет записи и Обмен-разрешение-окно (ОРОН) соответственно.

0

5

0

5

Блок 7 выдачи ответа содержит (фиг. 2) элементы И 57-61 с первого по пятый, первый 62 -и второй 63 элементы ИЛИ, первьй 64 и второй 65 элементы И-НЕ.

Блок 5 управления содержит (фиг.З) блок 66 адресации и блок 67 выбора режима. На фиг. 3 обозначены входы 68 и 69 адресации.

Устройство рабо ает следующим образом.

Запоминающее устройство (ЗУ) обеспечивает чтение и запись шестнадцатиразрядного слова или восьмиразрядного байта, общее стирание информации во всем объеме памяти ЗУ, выборочное стирание информации в одном из рядов ЗУ. Конкретный адрес банка, занимаемого ЗУ, устанавливается при помощи пускателей в блоке 66 (фиг. 3),, ЗУ обеспечивает работу в режимах прямой и страничной адресации путем установки в определенное положение переключателей в блоке 66.

Регистр 2 служит для задания различных режимов работы ЗУ. Обращение к нему происходит при общем выборочном стирании, страничной адресации, прерывании программы, опросе готовности ЗУ.

Пуск стирания осуществляется при установленном в единицу нулевом разряде регистра 2, программно только записывается, общее стирание - при единице в первом разряде, второй и третий разряды регистра 2 предназначены для выборочного стирания каждого ряда, единица в шестом разряде разрешает прерывание, седьмой разряд определяет готовность устройства. Седьмой разряд устанавливается аппаратно, если в устройстве закончились циклы записи и стирания, а также сигналом на входе 14, программно только считывается, разряды с девятого по две- надцатьш осуществляют выбор одной из страниц памяти ЗУ по 1000 ячеек при ст)раничном методе адресации.

Адрес поступает в виде адресного слова, в котором указывают адресные входы элементов памяти накопителей 6 при прямой и страничной адресациях, девятьй и десятый разряды - старшие адресные входы элементов памяти накопителей 6 при прямой адресации, разряды с девятого по двенадцатый при страничной адресации формируют номер страницы, разряды с тринадцатого по

31

пятнадцатый осуществляют выбор банка данных.

В выборе банка данных участвуют также шестнадцатый и семнадцатый разряды адреса.

Рассмотрим работу устройства в режиме считывания при страничной адресации. В этом режиме блок 5 вырабатывает сигнал Окно следующим образом. При подаче сигнала на вход 12 передается сигнал выборки устройства (ВУВ) на входе 26. На входах 19 разряды с пятнадцатого по тринадцатьш формируют адрес 16ХХХХ, а разряды с двенадцатого по девятый задают ад- pec 5XXXj в итоге формируются адреса 165ХХХ (где X - безразлично), т.е. Окно с адресами 165000 - 165776.

При наличии стробирующего сигнала ОБМН на входе 25 и сигнала ВУВ на входе 26 блок 5 формирует сигнала ВБ на выходах 42. Выбор номера страницы определяется разрядами с девятого по двенадцатью регистр 2, сигналы с выходов которого поступают в блок 5.

.При этом на адресные входы с первого по восьмой элементов памяти накопителя 6 подаются разряды с первог по восьмой регистра 4, достаточные для выбора из накопителя lOOOg шест- надцатиразрядных слов. Сигнал ОБЫ В на входе -24 участвует в выборе сигнала ОРОН на выходе 56, подаваемого в блок 7 для формирования сигнала УПР 1 Н на выходе 43, который передает в магистраль сигнал ответа устройства М ОТВ Н на выход. 16 блока 1.

Режим стирания начинается с момента записи данных в соответствующие разряды регистра 2. В адресной части регистра 2 выставляется адрес, на вход 24 поступает сигнал OEM В, при этом поступает сигнал УВ В на вход 30 который поступает в блок 7, где при наличии сигнала ДЗП В на входе 23 вырабатываются сигналы ЗАПИСЬ PC В на выходе 27, ПРИЕМ В на выходе 46.

При установленном в единицу нулевом разряде входов 19 и сигнале на

выходе 47 осуществляется пуск стирания .

В результате с выходов 42 поступают в накопитель 6 сигналы, осуществляющие выбор всех рядов для общего стирания. Выбор ряда при выборо ном стирании определяют второй и третий разряды регистра 2, сигналы с выходов которых участвуют в форми

Формула

ровании сигналов ВБР В на выходе 42 блока 5.

Сигнал СТИР Н с выхода 39 блока 5 поступает на вход формирователя 3. По окончании сигнала СТИР В на выходе 68 фронтом из высокого логического уровня в низкий запускается формирователь 3, и на выходе 51 формируется сигнал КЭС Н на время, необходимое для завершения переходных процессов в накопителе 6.

Одновременно завершение сигнала СТИР В на выходе 68 снимает сигнал ОС Н на выходе 69 и сигнал ВЫБОР В на выходах 42. После.окончания сигнала на выходе 51 снимается сигнал ЗАПР ОБР Н на входе 49 регистра 2 и с приходом очередного фронта из низкого логического уровня в высокий сигнала OEM В на входе 24 на выходе седьмого разряда регистра 2 устанавливается единица, что свидетельствует об oкoнчaшiи ipiKxra стирания.

Режим побайтовой записи выполняется при наличии сигнала ПЗП на входе 23 и сигналов ЗАПН на входах 34 и 35, осуществляющих запись данных в регистр 4. Сигнал на входе 27 устанавливает соответствующий триггер в блоке 67 в единичное состояние (при наличии сигнала на входе 23), при этом осуществляется запись одного из байтов. Выбор старшего или младшего байта определяется нулевым адресным разрядом, который поступает в ЗУ во время адресной части цикла и запоминается одновременно с другими адресными разрядами в блоке 66. Если разряд 00 адреса передается высоким уровнем, то в блоке 5 вырабатывается сигнал ЗАП 1 Н на выходе 36 и в накопитель 6 записывается maдший байт, т.е. данные, посту- пающйе по разрядам с нулевого по седьмой входов 32.

Если разряд 00 адреса передается низким уровнем, то в накопитель 6 за- , писывается сигналом ЗАП 2Н на выходе 37 старший байт, т.е. данные, поступающие по- разрядам с второго по пятнадцатый входов 32.

По окончании каждого режима па лы- ходе 45 блока 7 формируется сигнал ответа.

и 3 о б р е т е и и я

Формула

1. ЗапомиНс к цее устройство, содержащее накопитесь, регистр данных и

блок управления, причем входы и выходы регистра данных,входы и выходы первой группы блока управления являются одними из информационных и адресных входов и выходов устройства, другими информационными входами и выходами которого являются информационные входы и выходы накопителя, а тактовыми входами - входы синхронизации блока управления, одни из выходов первой группы которого соединены соответственно с первым управляющим входом регистра данных, с одними из, управляющих и адресных входов накопителя, отличающееся тем, что, с целью повышения надежности и расширения функциональных возможностей устройства за счет обеспечения побайтовой записи и выборочного стирания данных, а также обеспечения возможности страничной адресации, в устройство введены регистр состояния, блок вьщачи ответа, формирователь одиночных импульсов, элемент НЕ,

накопительный элемент и ограничитель- 25 ззторого и четвертого элементов И,

вт

ный элемент, причем первый выход формирователя одиночных импульсов подключен к входу элемента НЕ, второй выход - к первому выводу накопительного элемента, а третий выход - к рому выводу накопительного элемента и первому выводу ограничительного элемента, входы регистра состояния подключены к одним из входов регистра данных, выходы регистра состояния соединены с входами второй группы блока управления, первый управляющий вход регистра состояния подключен к первому входу синхронизации блока управления, первый и второй выходы блока выдачи ответа соединены соответственно с вторым управляющим входом регистра состояния и одним из входов третьей группы блока управления и с вторым управляющим входом регистра данных, входы блока выдачи ответа подключены к одним из выходов второй группы блока управления, другие выходы второй группы которого соединены соответственно с третьим управляющим входом регистра состояния, с прямым и инверсным входами формирователя одиночных импульсов, другие адресные входы накопителя под

ключены к другим выходам первой группы блока управления, вход сброса которого соединен с выходом элемента НЕ, одни из выходов регистра состояния являются другими адресными выходами устройства, установочные входы регистра состояния и другие входы третьей группы блока управления являются управляющими входами устройства,

выходы с второго по шестой блока выдачи ответа и другие вьгходы регистра состояния являются управляющими выходами устройства, второй вывод ограничительного элемента и вход стробирования формирователя одиночных импульсов являются входами пита.ния устройства.

20

2. Устройство по п. 1, о т л и - а ю щ е е с я тем, что блок вьзда- чи ответа содержит элементы И с первого по пятьй, элементы ИЛИ и элементы И-НЕ, причем первьш ход первого элемента И соединен с первыми входао зо

35

40

45

50

вто1)ые входы которых подключены соответственно к выходу первого элемента И-НЕ и к выходу третьего элемента И, первый вход которого соединен с выходом второго элемента И-НЕ, первый вход которого подключен к выходу первого элемента ИЛИ, первый вход которого является первым входом блока, вторым входом которого являются йер- вые входы первого элемента И-НЕ, пятого элемента И и второй вход первого элемента ИЛИ, третьим и четвертым входами блока являются соответственно первый вход первого элемента И и вторые входы элементов И-НЕ и пятого элемента И, входами с пятого по деся-. тьй блока являются соответственно второй вход первого элемента И и первый вход второго элемента ИЛИ, второй вход третьего элемента И, третий вход первого элемента И, второй вход второго элемента ИЛИ, третий вход третьего элемента И и третий вход второго элемента И, выходами блока с первого по шестой являются соответственно второй вход третьего элемента И, выходы первого и четвертого элементов И, выходы второго элемента ИЛИ, второго и пятого элементов И.

фuг.f

4f

SJ

сриг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Счетчик адресации для прямого доступа к памяти | 1986 |

|

SU1388879A1 |

| Устройство для сопряжения ЭВМ с внешним накопителем | 1988 |

|

SU1672459A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Запоминающее устройство | 1979 |

|

SU849299A1 |

| Запоминающее устройство | 1975 |

|

SU639016A1 |

| Запоминающее устройство | 1975 |

|

SU555440A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является повьшение надежности и расширение функциональных возможностей устройства за счет обеспечения побайтовой записи и считывания данных, а также возможности страничной адресации. Предложенное устройство содержит регистр состояния, формирователь одиночных импульсов, регистр данных, блок управления, накопитель, бл ок выдачи ответа, элемент НЕ, накопительный и ограничительный элементы. Введенные вновь регистр состояния и блок выдачи ответа служат для обеспечения различных режимов работы, в том числе записи и чтения байтов, выборочного стирания, страничной адресации, и для ответа о готовности устройства по окончании каждого режима работы.Вновь введенные формирователь одиночных им- § пульсов, элемент НЕ, накопительный и ограничит ельный элементы формируют сигнал задержки на время окончания переходных процессов в накопителе. 1 3 .п.- ф-лы, 3 ил. (О (Л 1чЭ со со со

Редактор В.Петраш

Заказ 3711/52Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, .ул .Проектная, 4

Составитель Т.Зайцева

Техред М.Моргентал Корректор Е.Сирохман

| Авторское свидетельство СССР , № 911614, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Полупроводниковые запоминающие устройства./Под ред | |||

| А.Ю.Гордонова | |||

| М.: Радио и связь, 1981, с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-07-07—Публикация

1984-10-01—Подача