Изобретение относится к вычислительной технике и может быть использовано для управления адресацией памяти вычислительных устройств.

Целью изобретения является расширение функциональных возможностей за счет увеличения числа режимов адресации ячеек памяти и введения контроля за соблюдением границ выделенного адресного пространства.

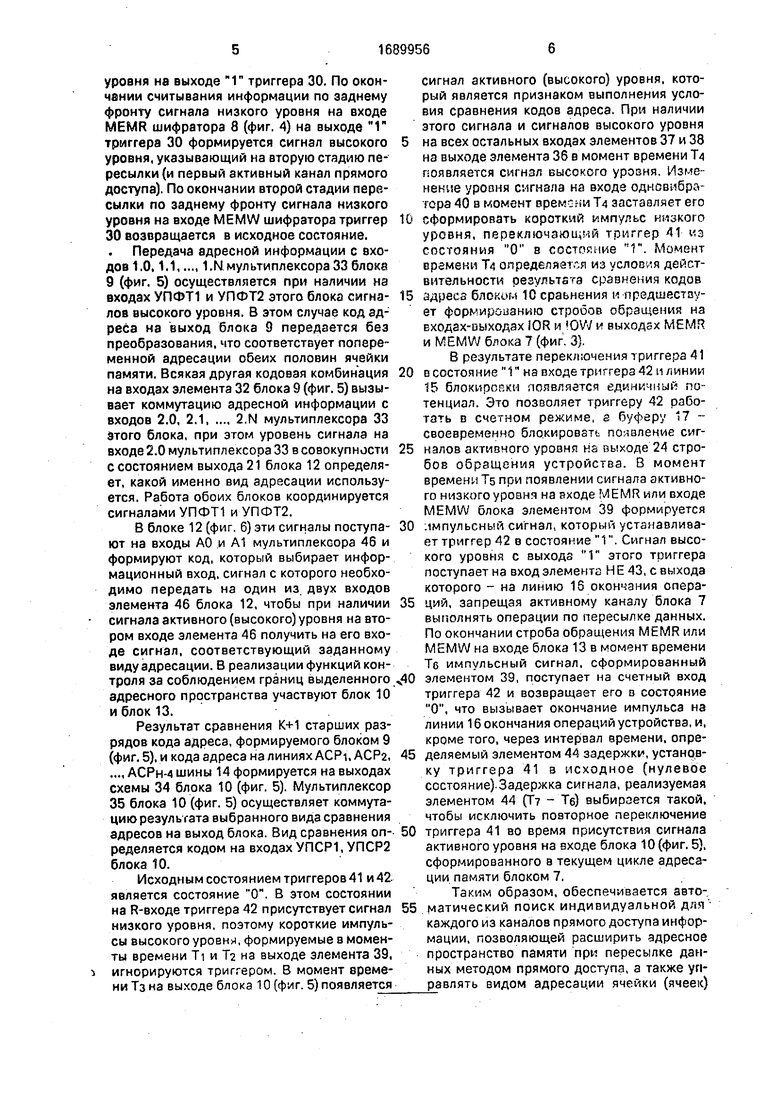

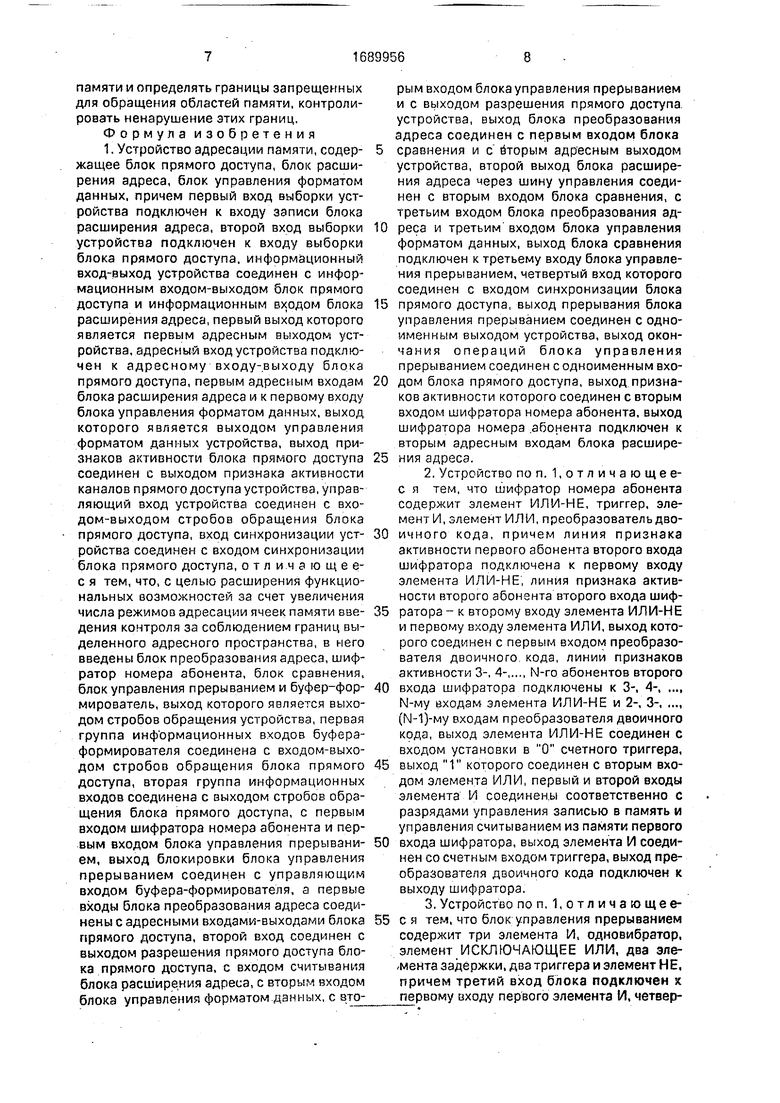

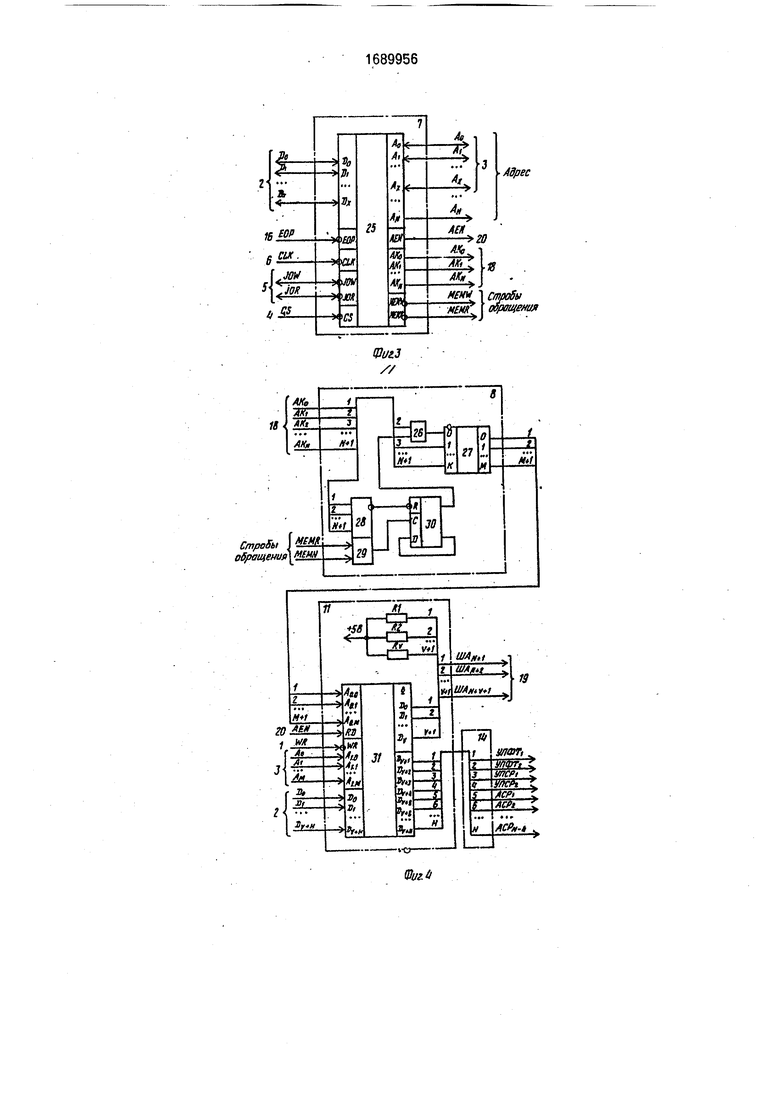

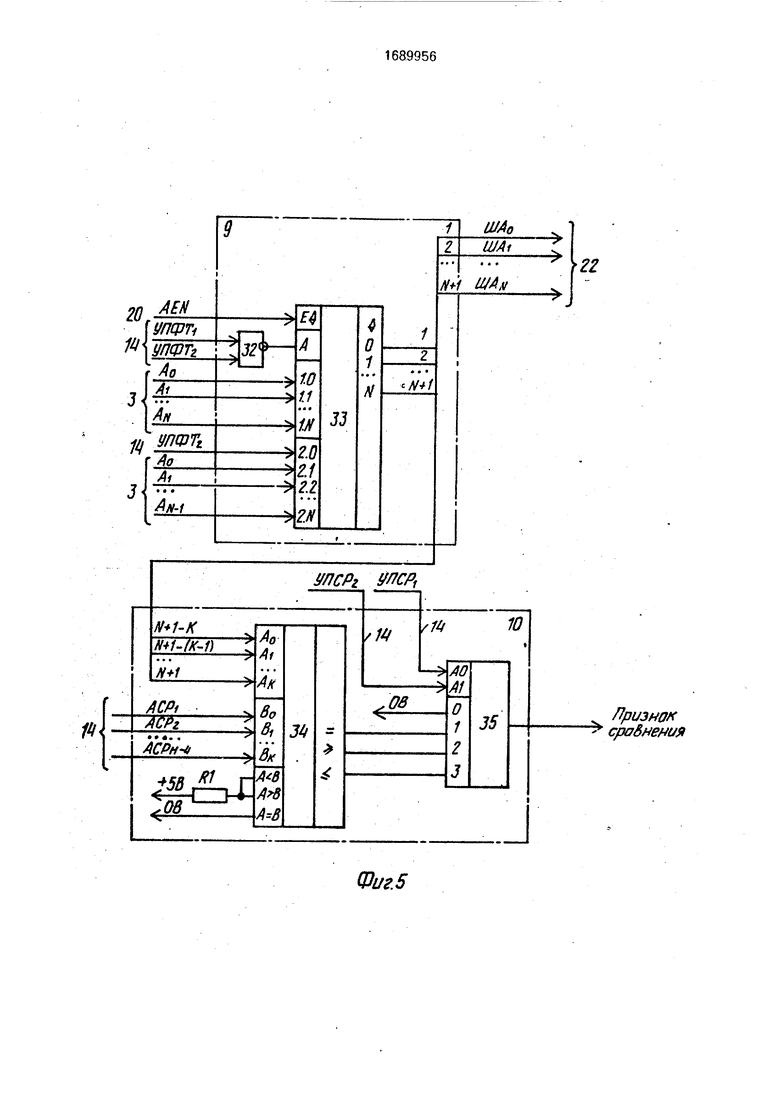

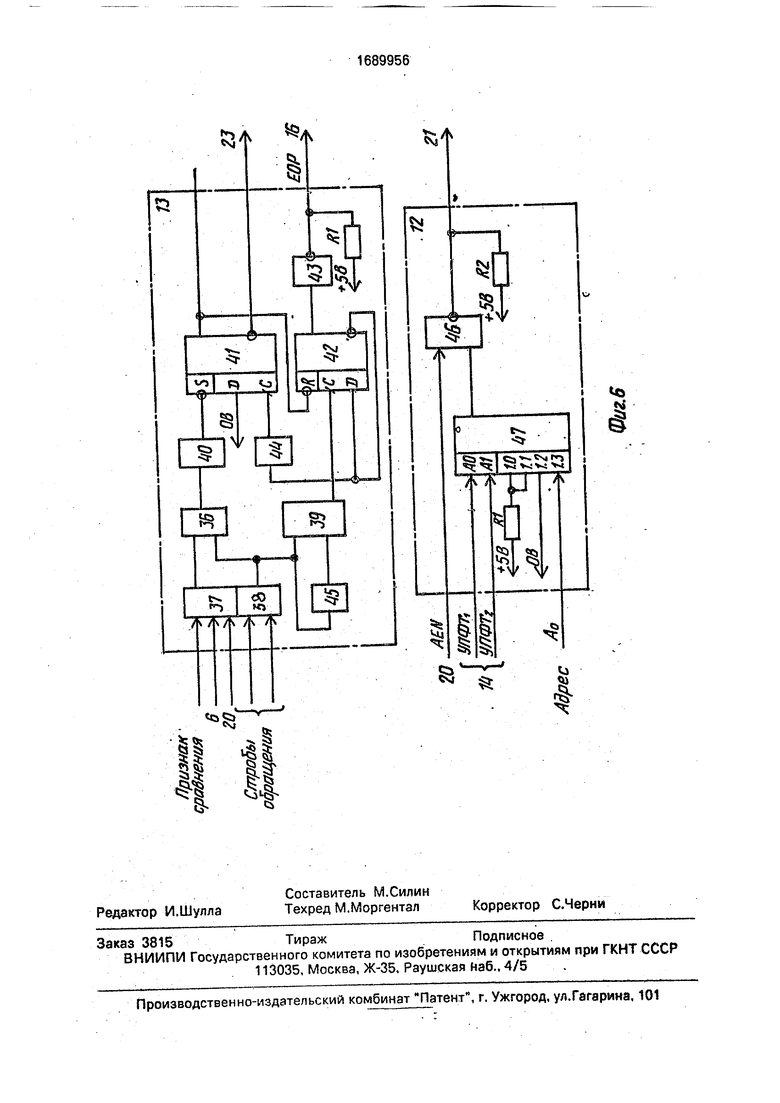

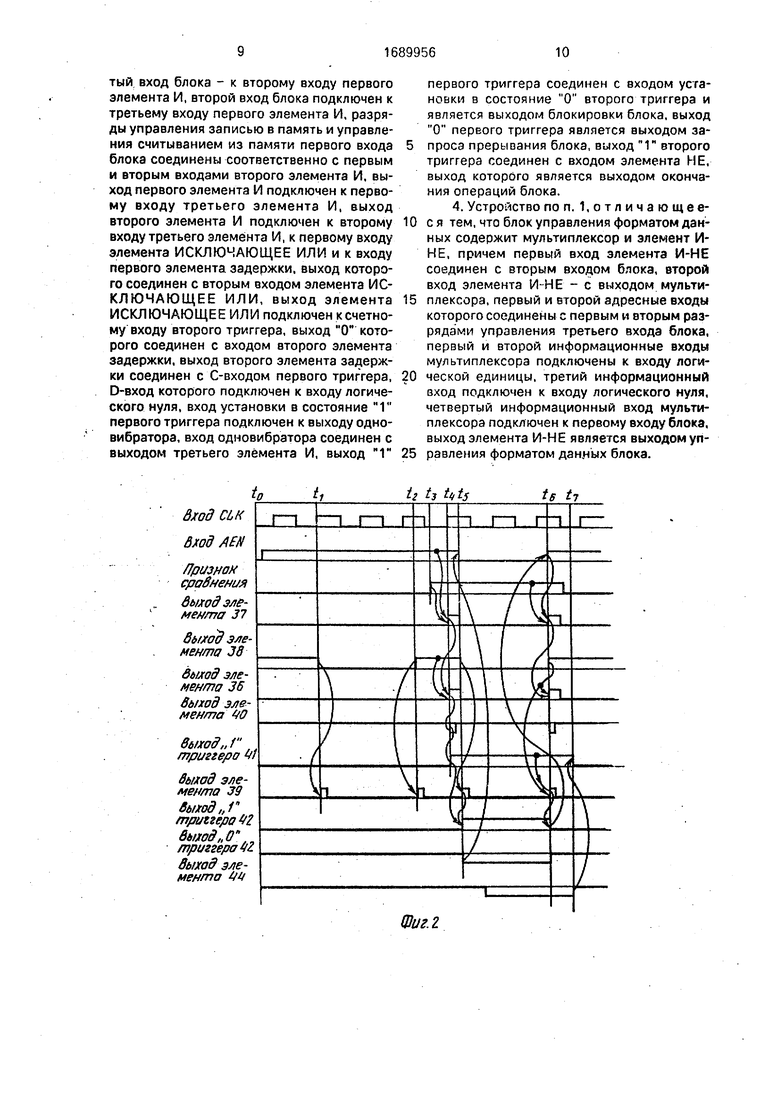

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временная диаграмма работы блока управления прерыванием; на фиг. 3 - функциональная схема блока прямого доступа; на фиг. 4 - функциональные схемы шифратора номера абонента и блока расширения адреса; на фиг. 5 - функциональные схемы блока преобразования адреса и блока сравнения; на фиг. 6 - функциональные схемы блока управления форматом данных, блока управления прерыванием и буфера-формирователя.

Устройство адресации памяти содержит первый вход 1 выборки, информационный вход-выход 2, адресный вход 3, второй вход Л выборки, управляющий вход 5, вход 6 синхронизации, блок 7 прямого доступа, шифратор 8 номера абонента, блок 9 преобразования адреса 3, блок 10 сравнения, блок 11 расширения адреса, блок 12 управления форматом данных, блок 13 управления прерыванием, шину 14 управления, линию 15 блокировки, линию 16 окончания операций, буфер-формирователь 17, выход 18 признаков активности каналов прямого доступа, первый адресный выход 19, выход 20 разрешения прямого доступа, выход 21 управления форматом данных, второй адресный выход 22, выход 23 прерывания, выход 24 стробов обращения.

Блок прямого доступа может быть реализован с использованием микросхем 25 типа КР580 ИР82, К1810ВТ37. Шифратор номера абонента содержит элемент ИЛИ 26, преобразователь27 двоичного кода, элемент ИЛИ-НЕ 28, элемент И 29, триггер 30. Блок расширения адреса реализован с использованием блока 31 памяти. Блок преобразования адреса содержит элемент И-НЕ 32, мультиплексор 33.

Блок сравнения содержит схему 34 сравнения и мультиплексор 35. Блок управления прерыванием содержит элементы И 36-38, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 39, одновибратор 40, триггеры 41 и 42, элемент НЕ 43, элементы 44 и 45 задержки. Блок управления форматом данных содержит элемент И-НЕ 46 и мультиплексор 47. Буфер-формирователь реализован на шинном формирователе.

Устройство работает в двух режимах: програмирования и адрнсации. Под режимом программирования подразумевается программная настройка блока прямого доступа 7 и (или) блока 11 расширения адреса, осуществляемая с использованием входов устройства.

В режиме программирования устройство работает следующим образом.

0 При обращении к блоку 7 (фиг. 3) данные

поступают на входы (с входов) D0, 61Dx

и записываются по стробу записи на входе IOW или считываются по стробу считывания на входе IOR при наличии сигнала выборки

5 на входе CS и синхросерии на входе CLK. Адрес внутренних регистров, к которым осуществляется обращение, определяется кодом на входах-выходах А0, AIАх блока.

При обращении к блоку 11 (фиг. 4) дан0 ные поступают на входы D0, Di Dv+н и

записываются при наличии сигнала низкого уровня на входе WR по адресу, определяемому кодом на входах Ai.o, AI.IАш.

В режиме адресации устройства, при5 знаком которого является наличие сигнала активного (высокого) уровня на выходе 20, осуществляется считывание информации с выходов Do, Di, Dv, блока 11 (фиг. 4). Адрес ячейки памяти блока 11 определяется

0 кодом на выходах 0,1М шифратора 8(фиг.

4), значение которого зависит от номера активного канала. Появление сигнала активного уровня на входах 0,1,,.., К элемента 27 является признаком активизации 1-, 2-, N-ro

5 канала блока 7, отсутствие сигнала активного уровня на этих входах - признак активности нулевого канала, При пересылке данных типа память - внешнее устройство триггер 30 шифратора устанавливается в состояние

0 О сигналом низкого уровня на его входе и таким образом исключается из активной работы.

Особым случаем является пересылка данных методом прямого доступа типа па5 мять - память, когда признаки активности каналов не отражаются на выходах АКо...АКы блока 7 (фиг. 3). Номер активного канала в этом случае определяется стадией пересылки: наличие сигнала MEMR на входе

0 шифратора 8 (фиг. 4) при отсутствии активных уровней на входах АК0 ... AKN однозначно определяет первую стадию (считывание из памяти) и нулевой активный канал, наличие сигнала М ЕМ W - вторую стадию (запись

5 в память) и первый активный канал. Благодаря сигналу высокого уровня на R-входе триггер 30 открыт для активной работы, именно он определяет стадию пересылки (а значит, и номер активного канала). Первая стадия определяется сигналом низкого

уровня на выходе Г триггера 30. По окончании считывания информации по заднему фронту сигнала низкого уровня на входе MEMR шифратора 8 (фиг. 4) на выходе Г триггера 30 формируется сигнал высокого 5 уровня, указывающий на вторую стадию пересылки (и первый активный канал прямого доступа). По окончании второй стадии пересылки по заднему фронту сигнала низкого уровня на входе MEMW шифратора триггер 10 30 возвращается в исходное состояние.

Передача адресной информации с входов 1.0,1.1,.... 1 .N мультиплексора 33 блока 9 (фиг. 5) осуществляется при наличии на входах УПФТ1 и УПФТ2 этого блока сигна- 15 лов высокого уровня, В этом случае код адреса на выход блока 9 передается без преобразования, что соответствует попеременной адресации обеих половин ячейки памяти. Всякая другая кодовая комбинация 20 на входах элемента 32 блока 9 (фиг. 5) вызывает коммутацию адресной информации с входов 2.0, 2.1, ..., 2.N мультиплексора 33 этого блока, при этом уровень сигнала на входе 2.0 мультиплексора 33 в совокупности 25 с состоянием выхода 21 блока 12 определяет, какой именно вид адресации используется. Работа обоих блоков координируется сигналами УПФТ1 иУПФТ2.

В блоке 12 (фиг. 6) эти сигналы поступа- 30 ют на входы АО и А1 мультиплексора 46 и формируют код, который выбирает информационный вход, сигнал с которого необходимо передать на один из двух входов элемента 46 блока 12, чтобы при наличии 35 сигнала активного (высокого) уровня на втором входе элемента 46 получить на его входе сигнал, соответствующий заданному виду адресации. В реализации функций контроля за соблюдением границ выделенного Ч40 адресного пространства участвуют блок 10 и блок 13.

Результат сравнения К+1 старших разрядов кода адреса, формируемого блоком 9 (фиг. 5), и кода адреса на линиях ACPi, АСРг, 45 ..., АСРн-4 шины 14 формируется на выходах схемы 34 блока 10 (фиг. 5). Мультиплексор 35 блока 10 (фиг. 5) осуществляет коммутацию результата выбранного вида сравнения адресов на выход блока. Вид сравнения оп- 50 ределяется кодом на входах УПСР1, УПСР2 блока 10.

Исходным состоянием триггеров 41 и 42 является состояние О. В этом состоянии на R-входе триггера 42 присутствует сигнал 55 низкого уровня, поэтому короткие импульсы высокого уровни, формируемые в моменты времени Ti и Т2 на выходе элемента 39, игнорируются триггером. В момент времени Тз на выходе блока 10 (фиг. 5) появляется

сигнал активного (высокого) уровня, который является признаком выполнения условия сравнения кодов адреса. При наличии этого сигнала и сигналов высокого уровня на всех остальных входах элементов 37 и 38 на выходе элемента 36 в момент времени ТА появляется сигнал высокого уровня. Изме некие уровня сигнала на входе одновибра- iopa 40 в момент времени Т4 заставляет его сформировать короткий импульс низкого уровня, переключающий триггер 41 ко состояния О в состояние Г. Момент времени Т олредепяатля из условия действительности оезультата сравнения кодов адреса блоком 10 сравнения м предшествует формированию стробов обращения на входах-оыходах 10R и OW и выходах MEMR и MEMW блока 7 (фиг. 3).

В результате переключения триггера 41 в состояние 1я на входе триггера 42 и линии 15 блокировки появляется единичный по тенциал. Это позволяет триггеру 42 работать в счетном режиме, е буферу 17 - своевременно блокировав появление сигналов активного уровня на выходе 24 стробов обращения устройства. В момент времени Ts при появлении сигнала активного низкого уровня на входе MEMR или входе MEMW блока элементом 39 формируется импульсный сигнал, который устанавливает триггер 42 в состояние 1. Сигнал высокого уровня с выходз 1 этого тоиггера поступает на вход элементе НЕ 43, с выхода которого - на линию 16 окончания операций, запрещая активному каналу блока 7 выполнять операции по пересылке данных. По окончании строба обращения MEMR или MEMW на входе блока 13 в момент времени Те импульсный сигнал, сформированный элементом 39, поступает на счетный вход триггера 42 и возвращает его в состояние О, что вызывает окончание импульса на линии 16 окончания операций устройства, и, кроме того, через интервал времени, определяемый элементом 44 задержки, установку триггера 41 в исходное (нулевое состояние) Задержка сигнала, реализуемая элементом 44 (Ту - Те) выбирается такой, чтобы исключить повторное переключение триггера 41 во время присутствия сигнала активного уровня на входе блока 10 (фиг. 5), сформированного в текущем цикле адресации памяти блоком 7.

Таким образом, обеспечивается автоматический поиск индивидуальной для каждого из каналов прямого доступа информации, позволяющей расширить адресное пространство памяти при пересылке данных методом прямого доступа, а также управлять видом адресации ячейки (ячеек)

памяти и определять границы запрещенных для обращения областей памяти, контролировать ненарушение этих границ. Формула изобретения 1. Устройство адресации памяти, содержащее блок прямого доступа, блок расширения адреса, блок управления форматом данных, причем первый вход выборки устройства подключен к входу записи блока расширения адреса, второй вход выборки устройства подключен к входу выборки блока прямого доступа, информационный вход-выход устройства соединен с информационным входом-выходом блок прямого доступа и информационным входом блока расширения адреса, первый выход которого является первым адресным выходом устройства, адресный вход устройства подключен к адресному входу-выходу блока прямого доступа, первым адресным входам блока расширения адреса и к первому входу блока управления форматом данных, выход которого является выходом управления форматом данных устройства, выход признаков активности блока прямого доступа соединен с выходом признака активности каналов прямого доступа устройства, управляющий вход устройства соединен с входом-выходом стробов обращения блока прямого доступа, вход синхронизации устройства соединен с входом синхронизации блока прямого доступа, отличаю щее- с я тем, что, с целью расширения функциональных возможностей за счет увеличения числа режимов адресации ячеек памяти введения контроля за соблюдением границ выделенного адресного пространства, в него введены блок преобразования адреса, шифратор номера абонента, блок сравнения, блок управления прерыванием и буфер-формирователь, выход которого является выходом стробов обращения устройства, первая группа информационных входов буфера- формирователя соединена с входом-выходом стробов обращения блока прямого доступа, вторая группа информационных входов соединена с выходом стробов обращения блока прямого доступа, с первым входом шифратора номера абонента и первым входом блока управления прерыванием, выход блокировки блока управления прерыванием соединен с управляющим входом буфера-формирователя, а первые входы блока преобразования адреса соединены с адресными входами-выходами блока прямого доступа, второй вход соединен с выходом разрешения прямого доступа блока прямого доступа, с входом считывания блока расширения адреса, с вторым входом блока управления форматом данных, с вторым входом блока управления прерыванием и с выходом разрешения прямого доступа устройства, выход блока преобразования адреса соединен с первым входом блока

сравнения и с вторым адресным выходом устройства, второй выход блока расширения адреса через шину управления соединен с вторым входом блока сравнения, с третьим входом блока преобразования ад0 реса и третьим входом блока управления форматом данных, выход блока сравнения подключен к третьему входу блока управления прерыванием, четвертый вход которого соединен с входом синхронизации блока

5 прямого доступа, выход прерывания блока управления прерыванием соединен с одноименным выходом устройства, выход окончания операций блока управления прерыванием соединен с одноименным вхо0 дом блока прямого доступа, выход признаков активности которого соединен с вторым входом шифратора номера абонента, выход шифратора номера .абонента подключен к вторым адресным входам блока расшире5 ния адреса.

2,Устройство поп. 1,отличающее- с л тем, что шифратор номера абонента содержит элемент ИЛИ-НЕ, триггер, элемент И, элемент ИЛИ, преобразователь дво0 ичного кода, причем линия признака активности первого абонента второго входа шифратора подключена к первому входу элемента ИЛИ-НЕ, линия признака активности второго абонента второго входа шиф5 ратора - к второму входу элемента ИЛИ-НЕ и первому входу элемента ИЛИ, выход которого соединен с первым входом преобразователя двоичного кода, линии признаков активности 3-, 4-,..., N-ro абонентов второго

0 входа шифратора подключены к 3-, 4-, ..., N-му входам элемента ИЛИ-НЕ и 2-, 3-, ..., (М-1)-му входам преобразователя двоичного кода, выход элемента ИЛИ-НЕ соединен с входом установки в О счетного триггера,

5 выход 1 которого соединен с вторым входом элемента ИЛИ, первый и второй входы элемента И соединены соответственно с разрядами управления записью в память и управления считыванием из памяти первого

0 входа шифратора, выход элемента И соединен со счетным входом триггера, выход преобразователя двоичного кода подключен к выходу шифратора.

3.Устройство поп, 1,отличающее- 5 с я тем, что блок управления прерыванием

содержит три элемента И, одновибратор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента задержки, два триггера и элемент НЕ, причем третий вход блока подключен х первому входу первого элемента И, четвертый вход блока - к второму входу первого элемента И, второй вход блока подключен к третьему входу первого элемента И, разряды управления записью в память и управления считыванием из памяти первого входа блока соединены соответственно с первым и вторым входами второго элемента И, выход первого элемента И подкпючен к первому входу третьего элемента И, выход второго элемента И подключен к второму входу третьего элемента И, к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к входу первого элемента задержки, выход которого соединен с вторым входом элемента ИС- КЛЮЧАЮЩЕЕ ИЛИ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к счетному входу второго триггера, выход О которого соединен с входом второго элемента задержки, выход второго элемента задержки соединен с С-входом первого триггера, D-вход которого подключен к входу логического нуля, вход установки в состояние 1 первого триггера подключен к выходу одно- вибратора, вход одновибратора соединен с

первого триггера соединен с входом установки в состояние О второго триггера и является выходом блокировки блока, выход О первого триггера является выходом запроса прерывания блока, выход 1 второго триггера соединен с входом элемента НЕ, выход которого является выходом окончания операций блока.

4. Устройство по п. 1,отличающеес я тем, что блок управления форматом данных содержит мультиплексор и элемент И- НЕ, причем первый вход элемента И-НЕ соединен с вторым входом блока, второй вход элемента - с выходом мультиплексора, первый и второй адресные входы которого соединены с первым и вторым разрядами управления третьего входа блока, первый и второй информационные входы мультиплексора подключены к входу логической единицы, третий информационный вход подключен к входу логического нуля, четвертый информационный вход мультиплексора подключен к первому входу блока, выход элемента И-НЕ является выходом уп18

Стробы обращена

ША

-

М ШАн

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации памяти | 1987 |

|

SU1411756A1 |

| Буферное устройство для передачи данных | 1987 |

|

SU1418725A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

Изобретение относится к вычислительной технике и может Быть использовано дня управления адресацией памяти, допускающей обращение к любой из двух независимых половин ячеек, Целью изобретения является расширение функциональных возможностей за счет увеличения числа режимов адресации ячеек памяти и введения контроля за соблюдением границ выделенного адресного пространства. Устройство содержит первый и второй входы 1 и 4 выборки информационный вход-выход 2, адресный вход 3, управляющий вход 5, вход 6 синхронизации, блок 7 прямого доступа, шифратор 8 номера абонента, блок 9 преобразования адреса, блок 10 сравнения, блок 11 расширения адреса, блок 12 управления форматом данных, блок 13 управления прерыванием, формирователь 17. Цель достигается введением новых элементов и связей. 3 з.п.ф-лы, 6 ил.

АЕН

0,

УПФТ1

УПФТ2.

А0

AI

AN

Я

УПФТг

Г АО

AI

AN-I

32(

Е4

W

1Я

33

N+1

i

Признак сравнения

Фиг.5

1 |

§4

Ci

fc

I

I

t

| Устройство адресации памяти | 1987 |

|

SU1411756A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Манипулятор на большое число комбинаций, передаваемых по проводу или по радио | 1922 |

|

SU1840A1 |

| Манипулятор на большое число комбинаций, передаваемых по проводу или по радио | 1922 |

|

SU1840A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Манипулятор на большое число комбинаций, передаваемых по проводу или по радио | 1922 |

|

SU1840A1 |

Авторы

Даты

1991-11-07—Публикация

1989-07-31—Подача