Изобретение относится к вычислительной технике и может быть исполь- зовано в устройствах пассивной радиолокации.Целью изобретения является повышение быстродействия.

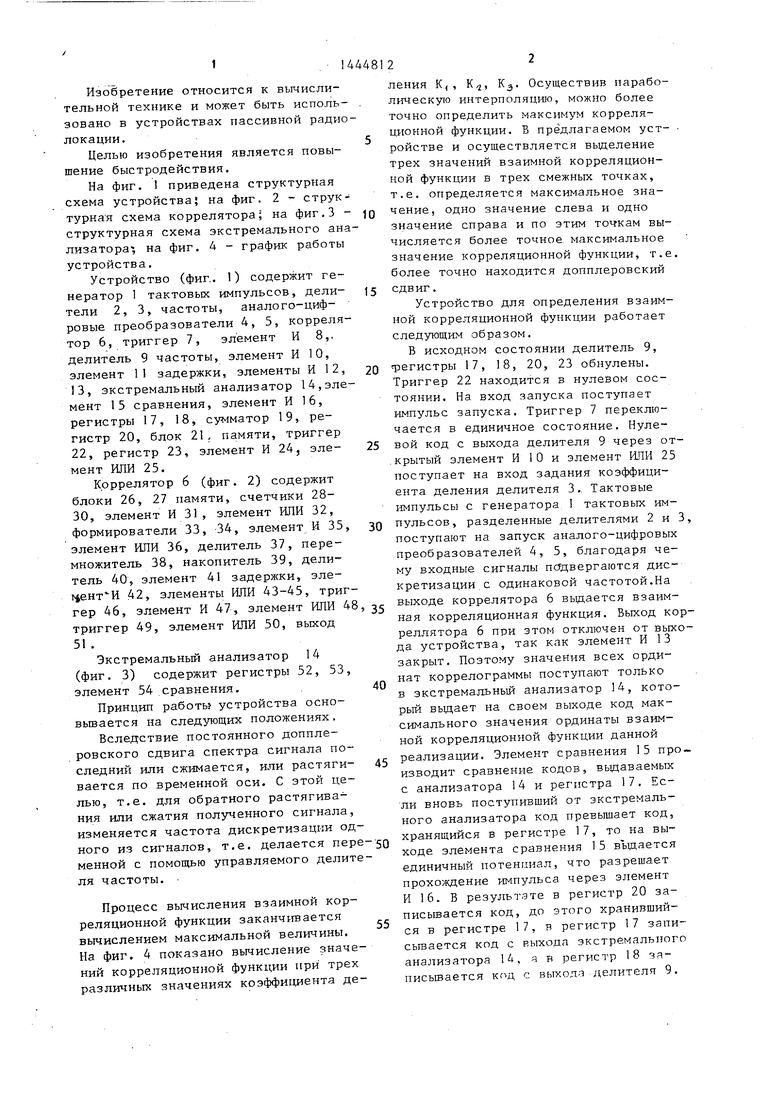

На фиг. приведена структурная схема устройства; на фиг. 2 - структурная схема коррелятора; на фиг.З - структурная схема экстремального анализатора ; на фиг. 4 - график работы устройства.

Устройство (фиг.. ) содержит генератор 1 тактовых импульсов, дели- тели 2, 3, частоты, аналого-цифровые преобразователи 4, 5, коррелятор 6, триггер 7, элемент И 8,. делитель 9 частоты, элемент И 10, элемент 11 задержки, элементы И 12, 13, экстремальный анализатор 14,элемент 15 сравнения, элемент И 16, регистры 17, 18, сумматор 19, регистр 20, блок 21, памяти, триггер 22, регистр 23, элемент И 24, эле- мент ИЛИ 25.

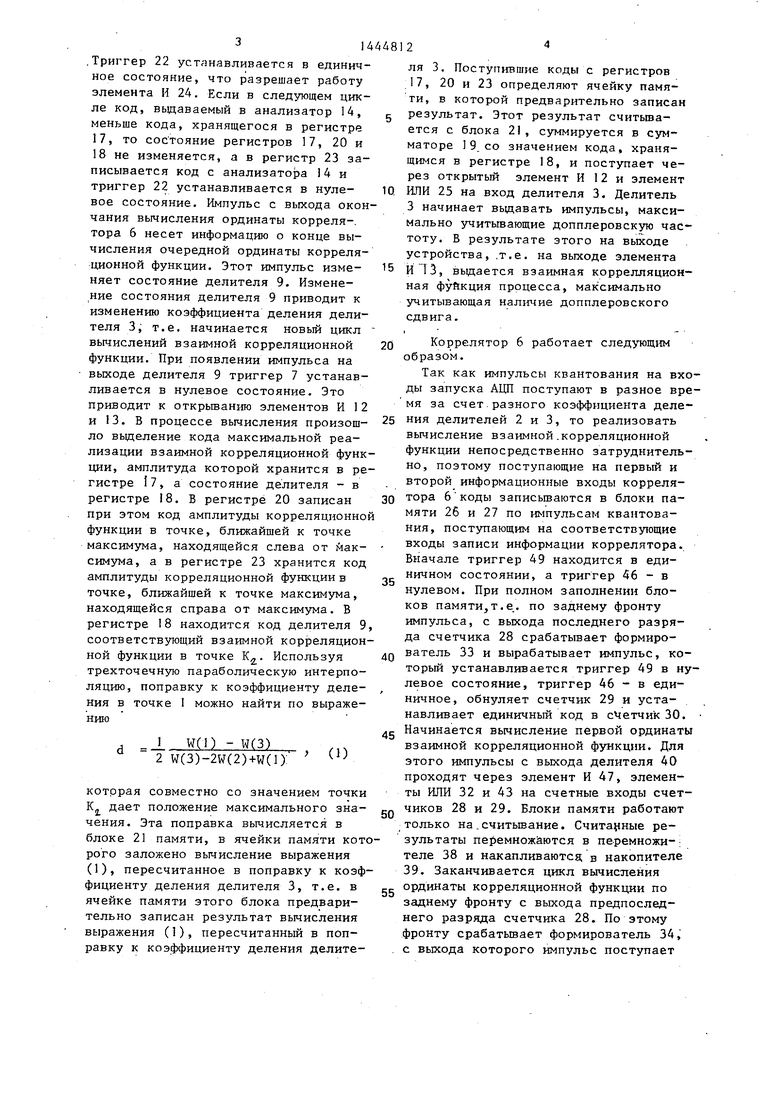

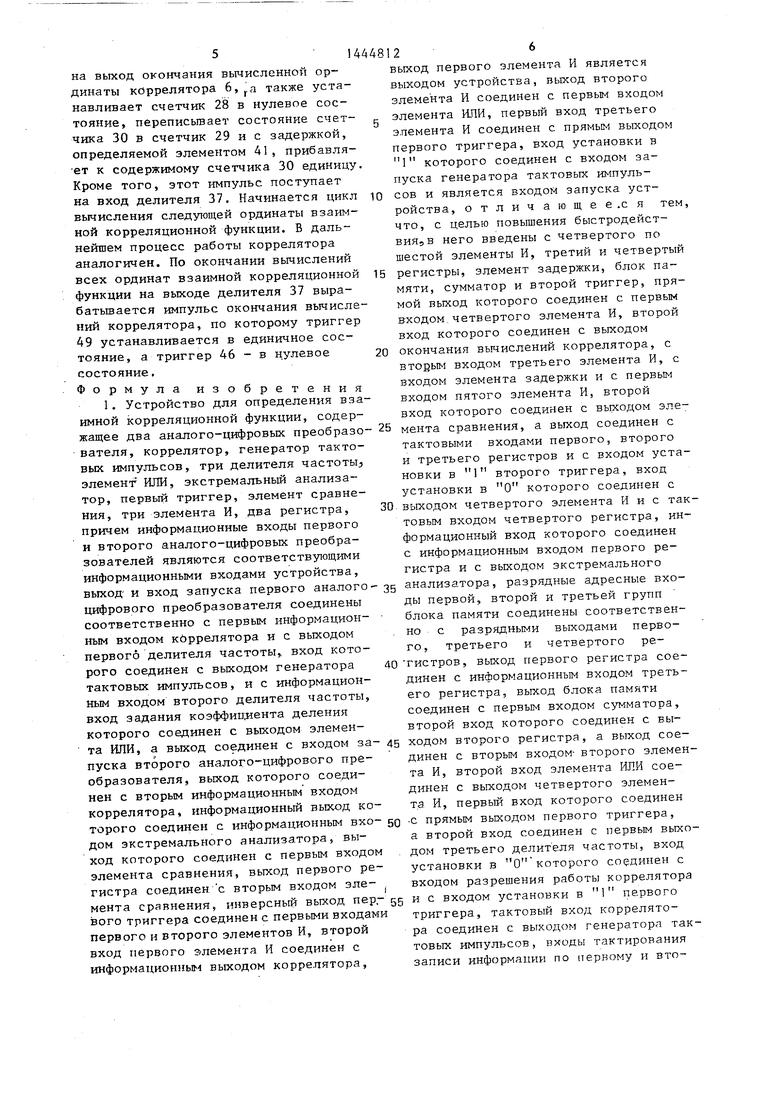

Коррелятор б (фиг. 2) содержит блоки 26, 27 памяти, счетчики 28- 30, элемент И 31, элемент ИЛИ 32, формирователи 33, 34, элемент И 35, элемент ИЛИ 36, делитель 37, перемножитель 38, накопитель 39, делитель 40, элемент 41 задержки, эле- 4eнт И 42, элементы ИЛИ 43-45, триггер 46, элемент И 47, элемент ИЛИ 48 триггер 49, элемент ИЛИ 50, выход 51 .

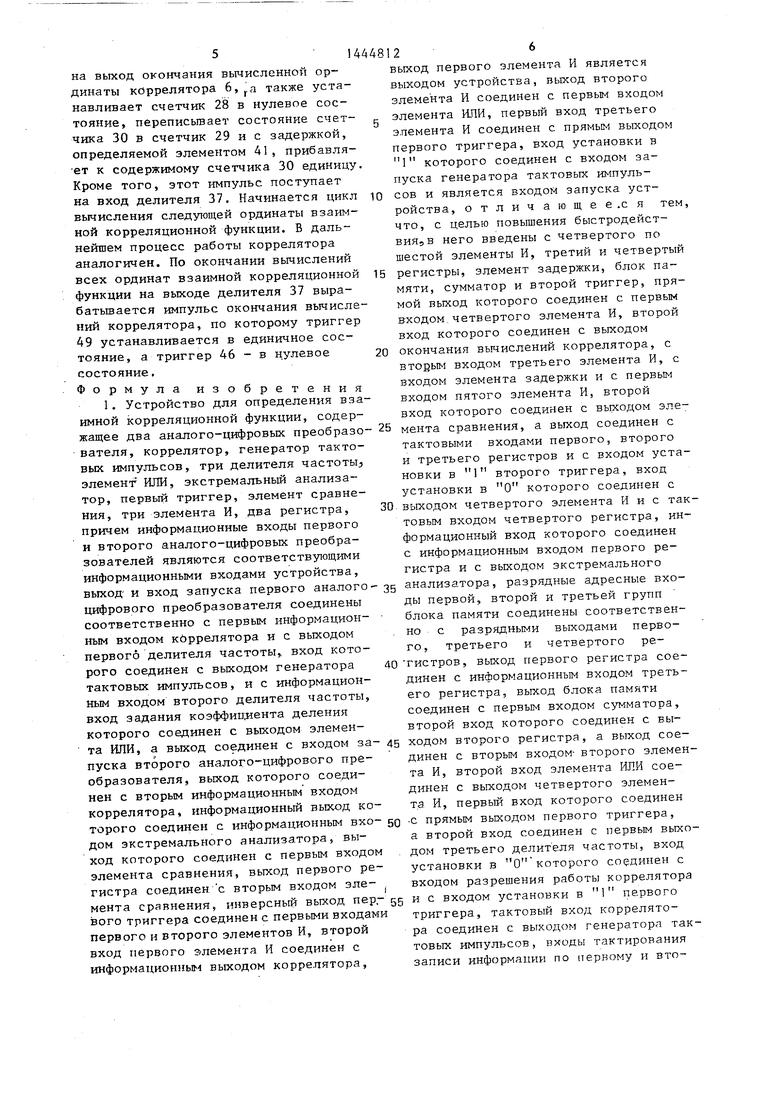

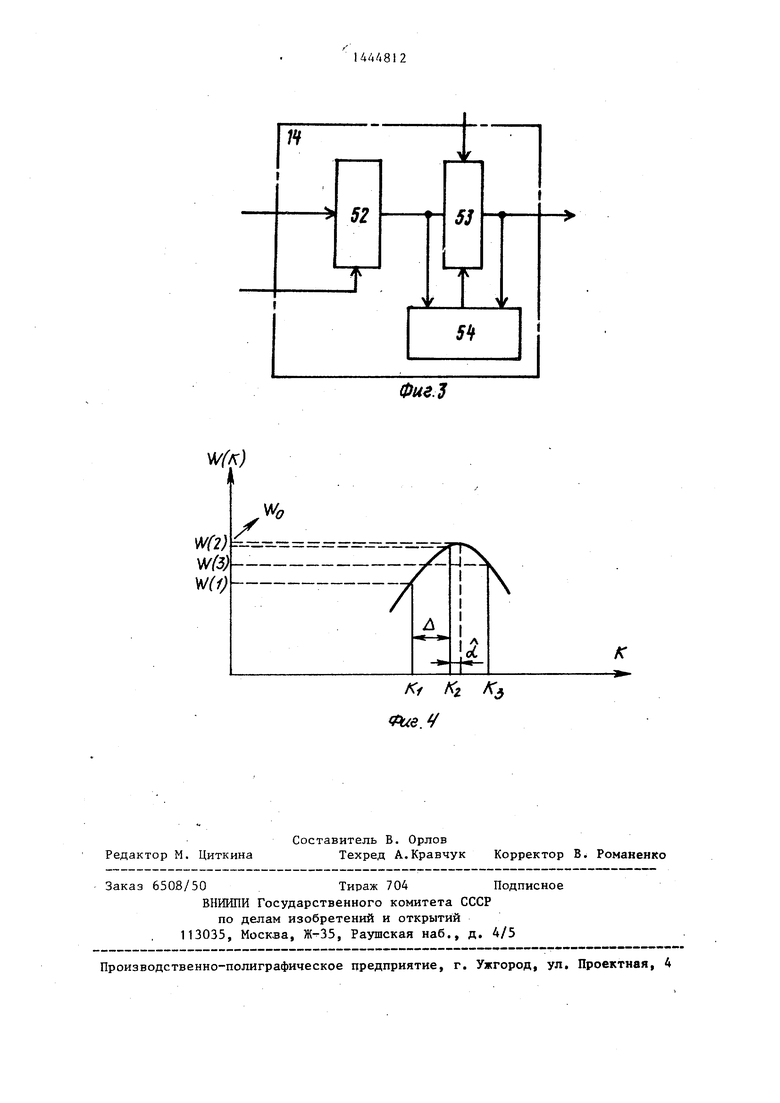

Экстремальный анализатор 14 (фиг. 3) содержит регистры 52, 53, элемент 54 сравнения,

Принцип работы устройства осно- вьшается на следующих положениях.

Вследствие постоянного доппле- ровского сдвига спектра сигнала последний или сжимается, или растяги- вается по временной оси. С этой целью, т.е. для обратного растягивания или сжатия полученного сигнала, изменяется частота дискретизации одного из сигналов, т.е. делается пере менной с помощью управляемого делителя частоты.

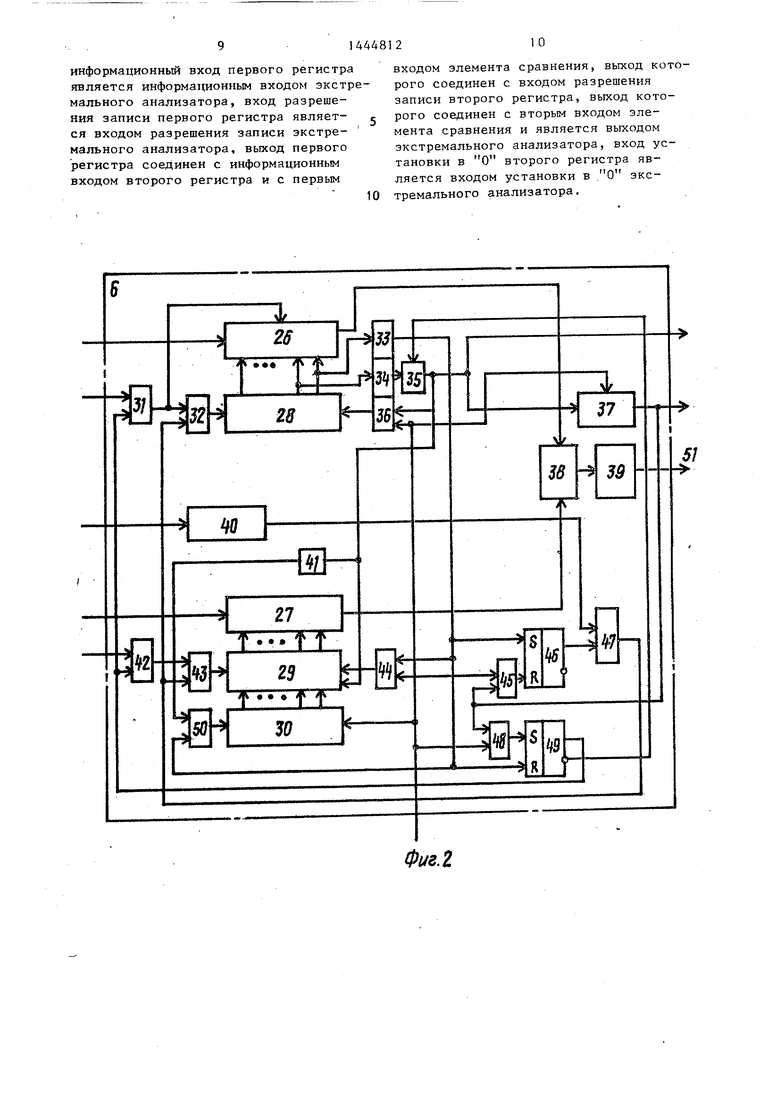

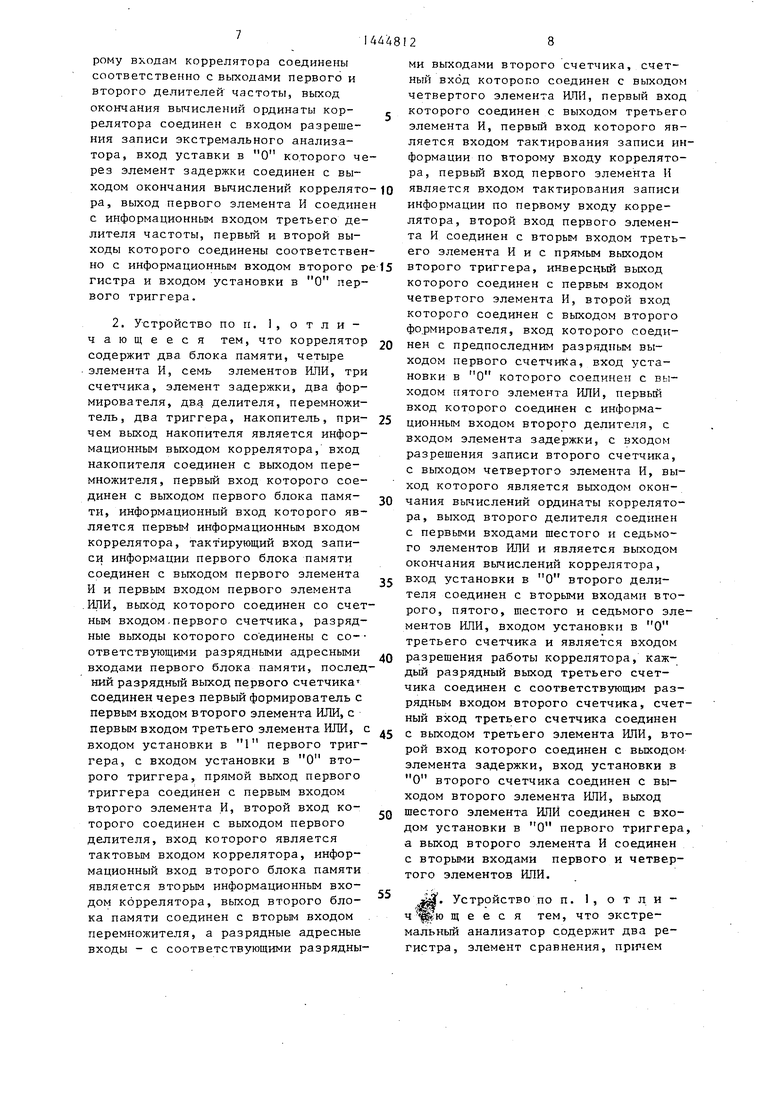

Процесс вычисления взаимной корреляционной функции заканчивается вычислением максимальной величины. На фиг. 4 показано вычисление значений корреляционной функции при трех различных значениях коэффициента де

К,,

К, К. Осуществив парабо

5 0 5

О 5

0

5 0

5

лическую интерполяцию, можно более точно определить максимум корреляционной функции. В предлагаемом уст- ройстве и осуществляется выделение трех значений взаимной корреляционной функции в трех смежных точках, т.е. определяется максимальное значение, одно значение слева и одно значение справа и по этим точкам вычисляется более точное максимальное значение корреляционной функции, т.е. более точно находится допплеровский сдвиг.

Устройство для определения взаимной корреляционной функции работает следующим образом.

В исходном состоянии делитель 9, регистры 17, 18, 20, 23 обнулены. Триггер 22 находится в нулевом состоянии. На вход запуска поступает импульс запуска. Триггер 7 переключается в единичное состояние. Нулевой код с выхода делителя 9 через от- - крытый элемент И 10 и элемент ИЛИ 25 поступает на вход задания коэффициента деления делителя 3.. Тактовые импульсы с генератора I тактовых импульсов, разделенные делителями 2 и 3, поступают на запуск аналого-цифровых преобразователей 4, 5, благодаря чему входные сигналы псщвергаются дискретизации с одинаковой частотой.На выходе коррелятора 6 выдается взаимная корреляционная функция. Выход кор- реллятора 6 при этом отключен от выхода устройства, так как элемент И 13 закрыт. Поэтому значения всех ординат коррелограммы поступают только в экстремальный анализатор 14, который выдает на своем выходе код максимального значения ординаты взаимной корреляционной функции данной реализации. Элемент сравнения 15 производит сравнение кодов, выдаваемых с анализатора 14 и регистра 17. Если вновь поступивший от экстремального анализатора код превьппает код, хранящийся в регистре 17, то на выходе элемента сравнения 15 вьщается единичный потенциал, что разрешает прохождение импульса через элемент И 16. В результате в регистр 20 записывается код, до этого хранившийся в регистре 17, в регистр 17 запи- сьгеается код с выхода экстремального анализатора 14, а в регистр 18 за- письшается код с выхода делителя 9.

314

.Триггер 22 устянавливается в единичное состояние, что разрешает работу элемента И 24. Если в следующем цикле код, вьщаваемый в анализатор 14, меньше кода, хранящегося в регистре 17, то состояние регистров 17, 20 и 18 не изменяется, а в регистр 23 записывается код с анализатора 14 и триггер 22 устанавливается в нуле- вое состояние. Импульс с выхода окончания вычисления ординаты корреля-, тора 6 несет информацию о конце вычисления очередной ординаты корреляционной функции. Этот импульс изме- няет состояние делителя 9. Изменение состояния делителя 9 приводит к изменению коэффициента деления делителя 3, т.е. начинается новый цикл вычислений взаимной корреляционной функции. При появлении импульса на выходе делителя 9 триггер 7 устанавливается в нулевое состояние. Это приводит к открьшанию элементов И 12 и 13. В процессе вычисления произош- ло выделение кода максимальной реализации взаимной корреляционной функции, амплитуда которой хранится в регистре 17, а состояние делителя - в регистре 18. В регистре 20 записан при этом код амплитуды корреляционной функции в точке, ближайшей к точке максимума, находящейся слева от йак- симума, а в регистре 23 хранится код амплитуды корреляционной функции в точке, ближайшей к точке максимума, находящейся справа от максимума. В регистре 18 находится код делителя 9 соответствутощий взаимной корреляционной функции в точке К. Используя трехточечную параболическую интерполяцию, поправку к коэффициенту деле- ния в точке 1 можно найти по выражению

н 1 wen - W(3) .,. 2 W(3)-2W(2)+W(O:

которая совместно со значением точки Kj дает положение максимального зна- чения. Эта поправка вычисляется в блоке 21 памяти, в ячейки памяти которого заложено вычисление выражения (1), пересчитанное в поправку к коэффициенту деления делителя 3, т.е. в ячейке памяти этого блока предварительно записан результат вычисления выражения (1), пересчитанньш в поправку к коэффициенту деления делителя 3, Поступ1гашие коды с регистров ;17, 20 и 23 определяют ячейку памяти, в которой предварительно записан результат. Этот результат считывается с блока 21, суммируется в сумматоре 19. со значением кода, хранящимся в регистре 18, и поступает через открытый элемент И 12 и элемент ИЛИ 25 на вход делителя 3, Делитель 3 начинает вьщавать импульсы, максимально учитывающие допплеровскую частоту. В результате этого на выходе устройства, .т.е. на выходе элемента И 13, выдается взаимная коррелляцион- ная фуйкция процесса, максимально учитывающая нал1тчие допплеровского сдвига.

Коррелятор 6 работает следующим образом.

Так как импульсы квантования на входы запуска АЦП поступают в разное время за счет, разного коэ({)фициента деления делителей 2 и 3, то реализовать вычисление взаимной.корреляционной функции непосредственно затруднительно, поэтому поступающие на первый и второй информационные входы коррелятора 6 коды записываются в блоки памяти 26 и 27 по импульсам квантования, поступающим на соответствующие входы записи информации коррелятора. Вначале триггер 49 находится в единичном состоянии, а триггер 46 - в нулевом. При полном заполнении блоков памяти,т.е. по заднему фронту импульса, с выхода последнего разряда счетчика 28 срабатывает формирователь 33 и вырабатывает импульс, который устанавливается триггер 49 в нулевое состояние, триггер 46 - в единичное, обнуляет счетчик 29 и устанавливает единичный код в с 1етчик 30. Начинается вычисление первой ординат взаимной корреляционной функции. Для этого импульсы с выхода делителя 40 проходят через элемент И 47, элементы ИЛИ 32 и 43 на счетные входы счетчиков 28 и 29. Блоки памяти работают только на.считьшание. Считанные результаты пе емнож&ются в пе-ремножи-: теле 38 и накапливаются в накопителе 39. Заканчивается цикл вычисления ординаты корреляционной функции по заднему фронту с выхода предпоследнего разряда счетчика 28. По этому фронту срабатьшает формирователь 34, с выхода которого импульс поступает

на выход окончания вычисленной ординаты коррелятора 6,а также устанавливает счетчик 28 в нулевое состояние, переписьгоает состояние счетчика 30 в счетчик 29 и с задержкой, определяемой элементом 41, прибавля- -ет к содержимому счетчика 30 единицу. Кроме того, этот импульс поступает на вход делителя 37. Начинается цикл вычисления следуищей ординаты взаимной корреляционной функции. В дальнейшем процесс работы коррелятора аналогичен. По окончании вычислений всех ординат взаимной корреляционной функции на выходе делителя 37 выра- батьтается импульс окончания вычислений коррелятора, по которому триггер 49 устанавливается в единичное состояние, а триггер 46 - в нулевое состояние.

Формула изобретения

1. Устройство для определения взаимной корреляционной функции, содер .

448126

выход первого элемента И является выходом устройства, выход второго элемента И соединен с первым входом элемента ИЛИ, первый вход третьего элемента И соединен с прямым выходом первого триггера, вход установки в 1 которого соединен с входом запуска генератора тактовых импуль10 сов и является входом запуска устройства, отличающее.с я тем, что, с целью повышения быстродейст- вияаВ него введены с четвертого по шестой элементы И, третий и четвертый

15 регистры, элемент задержки, блок памяти, сумматор и второй триггер, прямой выход которого соединен с первым входом.четвертого элемента И, второй вход которого соединен с выходом

20 окончания вьгчислений коррелятора, с вторым входом третьего элемента И, с входом элемента задержки и с первым входом пятого элемента И, второй вход которого соединен с вьрсодом эле

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения взаимной корреляционной функции | 1987 |

|

SU1427383A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Цифровой коррелятор | 1990 |

|

SU1824642A1 |

| Цифровой коррелятор сигналов различной доплеровской частоты | 1988 |

|

SU1571612A1 |

| Цифровой коррелятор | 1990 |

|

SU1727132A1 |

| Цифровой автокоррелятор | 1990 |

|

SU1829042A1 |

| Цифровой коррелятор | 1990 |

|

SU1727133A1 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР | 2002 |

|

RU2227321C2 |

| Устройство для определения взаимной корреляционной функции | 1977 |

|

SU691866A1 |

жащее два аналого-цифровых преобразо- 25 мента сравнения, а выход соединен с вателя, коррелятор, генератор тактовых импульсов, три делителя частоты элемент ИЛИ, экстремальный анализатор, первый триггер, элемент сравнения, три элемента И, два регистра, 30 причем информационные входы первого и второго аналого-цифровых преобразователей являются соответствующими информационными входами устройства.

тактовыми входами первого, второго и третьего регистров и с входом уста новки в 1 второго триггера, вход установки в О которого соединен с выходом четвертого элемента И и с та товым входом четвертого регистра, ин формационный вход которого соединен с информационным входом первого регистра и с выходом экстремального

выход- и вход запуска первого аналого- зв анализатора, разрядные адресные вхоцифрового преобразователя соединены соответственно с первым ннформацион- ным входом кбррелятора и с выходом первого делителя частоты вход которого соединен с выходом генератора тактовых импульсов, и с информационным входом второго делителя частоты, вход задания коэффицд1ента деления которого соединен с выходом элемента ИЛИ, а выход соединен с входом за пуска второго аналого-цифрового преобразователя, выход которого соединен с вторым информационным входом коррелятора, информационньй выход которого соединен с информационным вхо дом экстремального анализатора, выход которого соединен с первым входо элемента сравнения, выход первого регистра соединен с вторым входом эле

мента сравнения, инверсный выход пер,- 55 входом установки в вого триггера соединен с первыми входами первого и второго элементов И, второй вход первого элемента И соединен с информадионньм выходом коррелятора.

триггера, тактовый вход ра соединен с выходом г товых импульсов, входы записи информации по пе

мента сравнения, а выход соединен с

тактовыми входами первого, второго и третьего регистров и с входом установки в 1 второго триггера, вход установки в О которого соединен с выходом четвертого элемента И и с тактовым входом четвертого регистра, информационный вход которого соединен с информационным входом первого регистра и с выходом экстремального

-с

ды первой, второй и третьей групп блока памяти соединены соответственно с разрядными выходами первого, третьего и четвертого ре- тистров, выход первого регистра соединен с информационным входом третьего регистра, выход блока памяти соединен с первым входом сумматора, второй вход которого соединен с выходом второго регистра, а выход соединен с вторым входом- второго элемента И, второй вход элемента ИЛИ соединен с выходом четвертого элемента И, первый вход которого соединен

прямым выходом первого триггера, а второй вход соединен с первым выходом третьего делителя частоты, вход установки в О которого соединен с входом разрешения работы коррелятора

первого

входом установки в

триггера, тактовый вход коррелятора соединен с выходом генератора тактовых импульсов, входы тактирования записи информации по первому и второму входам коррелятора соединены соответственно с выходами первого и второго делителей частоты, выход окончания вычислений ординаты кор- релятора соединен с входом разрешения записи экстремального анализатора, вход уставки в О которого через элемент задержки соединен с выходом окончания вычислений коррелято pa, выход первого элемента И соедине с информационным входом третьего делителя частоты, первый и второй выходы которого соединены соответственно с информационньм входом второго р гистра и входом установки в О первого триггера.

O 5

0 5 0 Q .

5

5

ми выходами второго счетчика, счетный вход которого соединен с выходом четвертого элемента КПИ, первый вход которого соединен с выходом третьего элемента И, первый вход которого является входом тактирования записи информации по второму входу коррелятора, первый вход первого элемента И является входом тактирования записи информации по первому входу коррелятора, второй вход первого элемента И соединен с вторым входом третьего элемента И и с прямым выходом второго триггера, инверсный выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом второго формирователя, вход которого соединен с предпоследним разрядиьм выходом первого счетчика, вход установки в О которого соединен с выходом пятого элемента ИЛИ, первый вход которого соединен с информационным входом второго делителя, с входом элемента задержки, с входом разрешения записи второго счетчика, с выходом четвертого элемента И, выход которого является выходом окончания вычислений ординаты коррелятора, выход второго делителя соединен с первыми входами шестого и седьмого элементов ИЛИ и является выходом окончания вычислений коррелятора, вход установки в О второго делителя соединен с вторыми входами второго, пятого, шестого и седьмого элементов ИЛИ, входом установки в О третьего счетчика и является входом разрешения работы коррелятора, каждый разрядный выход третьего счетчика соединен с соответствующим разрядным входом второго счетчика, счетный вход третьего счетчика соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с выходом элемента задержки, вход установки в О второго счетчика соединен с выходом второго элемента ИЛИ, выход шестого элемента ИЛИ соединен с входом установки в О первого триггера, а выход второго элемента И соединен с вторыми входами первого и четвертого элементов ИЛИ.

. Устройство по п. 1, о т л и - щ е е с я тем, что экстремальный анализатор содержит два регистра, элемент сравнения, причем

информационный вход первого регистра является информационным входом экстремального анализатора, вход разрешения записи первого регистра являет- , ся входом разрешения записи экстре- мального анализатора, выход первого регистра соединен с информационным входом второго регистра и с первым

входом элемента сравнения, выход которого соединен с входом разрешения записи второго регистра, выход которого соединен с вторым входом элемента сравнения и является выходом экстремального анализатора, вход установки в О второго регистра является входом установки в / О экс10 тремального анализатора.

Фиг.2

Фи.}

KI KZ /Tj .

| Мирский Г.Я | |||

| Аппаратурное определение характеристик случайных процессов | |||

| М.: Энергия, 1972, с | |||

| Способ получения нерастворимых лаков основных красителей в субстанции и на волокнах | 1923 |

|

SU132A1 |

| Устройство для определения взаимной корреляционной функции | 1977 |

|

SU691866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| I | |||

Авторы

Даты

1988-12-15—Публикация

1987-02-10—Подача