Изобретение относится к вычислительной технике и может быть использовано в быстродействующих цифровых арифметических устройствах.

Известно матричное вычислительное устройство для перемножения двоичных операндов, которое Содержит входные регистры, матрицу вычислительных . ячеек и блок cy 1мaтopoв, причем каждая вычислительная ячейка содержит элемент И и одноразрядный сумматор Г

Недостатком этого устройства является то, что оно осуществляет пере- : множе ние операндов, заданных только в прямом коде.

Известно матричное множительное устройство осуществляющее перемножение двоичных чисел со знаками. Двоичные числа при этом .задаются в ;дополнительном коде. Для перемноже-i ния чисел, заданных обратным кодом, это устройство не предназначено 23.

Наиболее близким является устрой-, ство для перемножения двоичных операндов, содержащее матрицу вычислительных ячеек, каждая из которых со держит элемент И и одноразрядный : сумматор, причем первый и второй входы вычислительной ячейки соединены ; соответственно с первым и вторым вхот

дами элеь«ента И, выход которого соединен с одним из входов однораз-: рядного.сумматора, третий и четвер- . тый входа вычислительной ячейки сое динены соответственно с в торым и третьим входами одноразрядного сум;матора, один из выходов которого ;соединен с третьим вьрсодом вычислительной ячейки, а другой - с четвер10:Тым выходсм вычислительной ячейки, .причем первые выходы вычислительных {{чеек каждой строки матрицы соединены с первыми входами последующих : :вычислительных ячеек той же строки

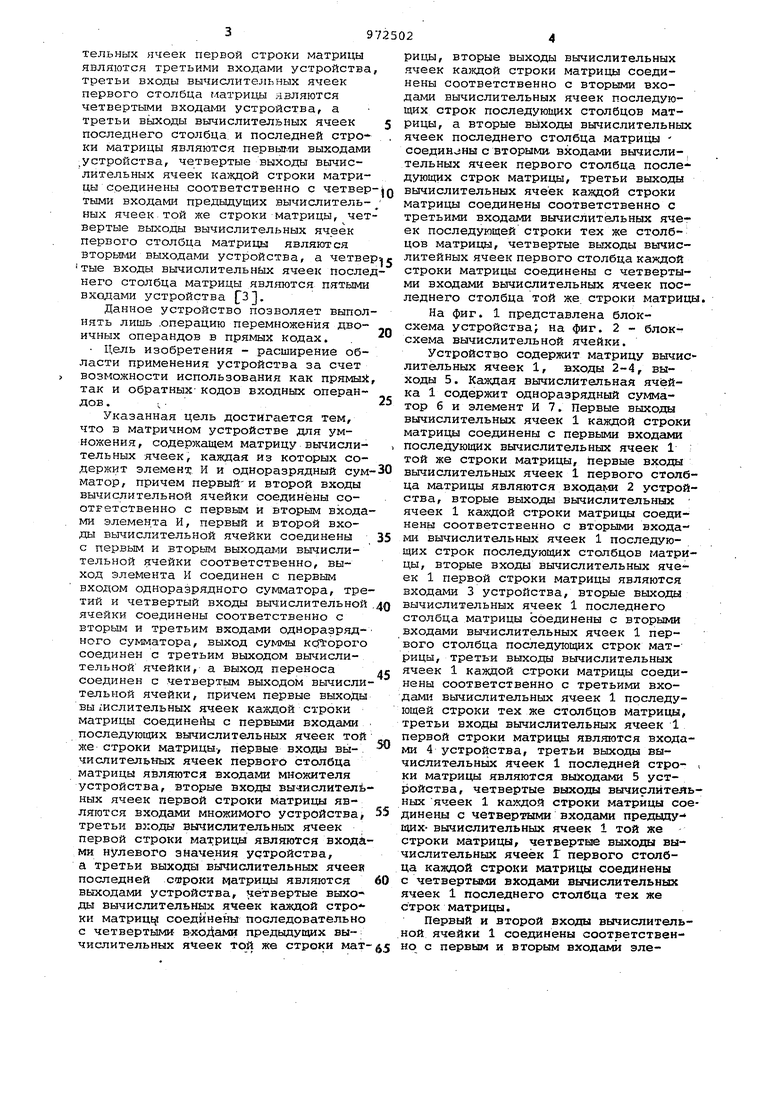

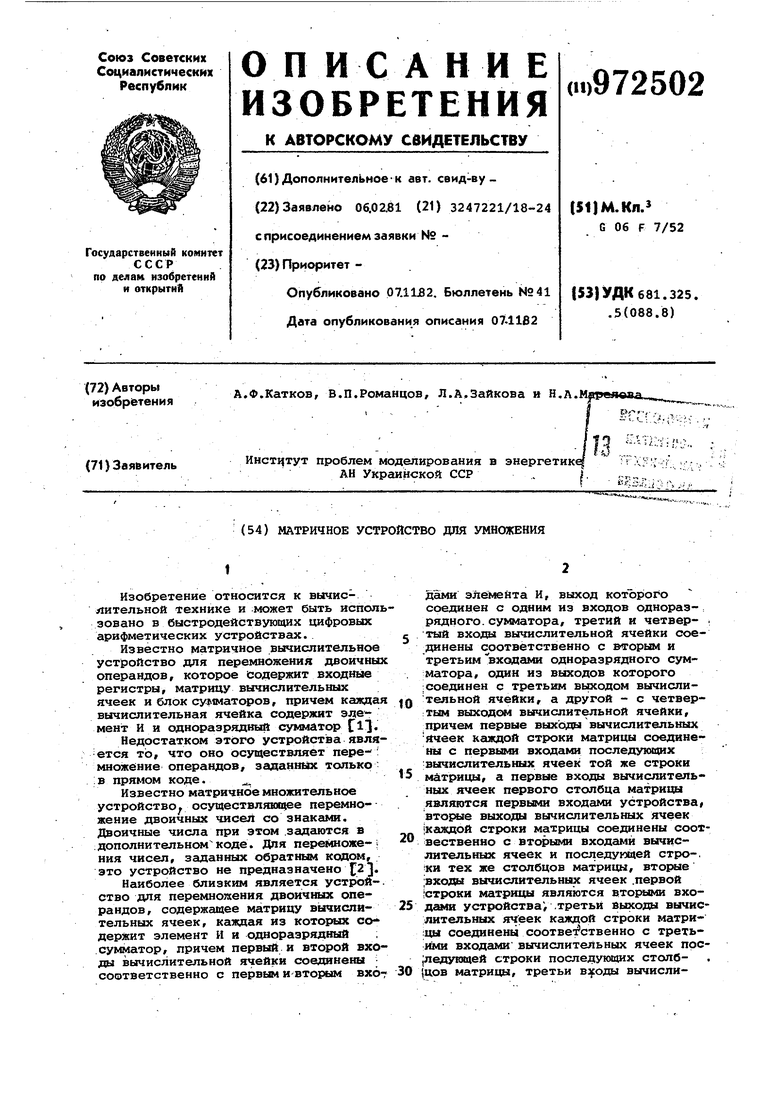

15 матрицы, а первые входы вычислительных ячеек первого столбца матрицы являются первыми входами устройства, выходы вычислительных ячеек |каждой строки матрицы соединены соот20вественно с вторыми входами вычислительных ячеек и последующей стро-. ки тех же столбцов матрицы, вто{яле :входы вычислительных ячеек .первой |строки матрицы являются вторыми вхо25ДШ4И устройства; .третьи выходы вычислительных ячеек каждой строки матри:цц соединены cooTBefcTBeHHo с третьими входами вычислительных ячеек прс|ледукяцей строки последующих столб30 ;цов матрицы, третьи вычислительных ячеек первой строки матрицы являются третьими входами устройства третьи входы вычислительных ячеек первого столбца матрицы являются четвертыми входами устройства, а третьи выходы вычислительных ячеек последнего столбца и последней строки матрицы являются первш-та: выходами ,устройства, четвертые выходы вычислительных ячеек каждой строки матрицы соединены соответственно с четвер тыми входами предыдущих вычислительных ячеек той же строки матрицы, чет вертые выходы вычислительных ячеек первого столбца матрицы являются вторыми выходами устройства, а четве тые входы вы:чиолительнЬ1х ячеек после него столбца матрицы являются пятыми вхсэдами устройства f3. Данное устройство позволяет выпол нять лишь .операцию перемножения двоичных операндов в прямых кодах. Цель изобретения - расширение области применения устройства за счет возможности использования как прямьЫ: так и обратных-кодов входных операндов . i Указанная цель достигается тем, что в матричном устройстве для умножения, содержащем матрицу вычислительных ячеек, каждая из которых содержит элемент, И и одноразрядный сум матор, причем первый- и второй входы вычислительной ячейки соединены соответственно с первым и вторым входа ми элемента И, первый и второй входы вычислительной ячейки соединены с первым и вторым выходшли вычислительной ячейки соответственно, выход элемента И соединен с первым входом одноразрядного сумматора, тре тий и четвертый входы вьгч:и ел и тельной ячейки соединены соответственно с вторым и третьим входами одноразрядного сумматора, выход суммы кфгорого соединен с третьим выходом вычислительной ячейки, а выход переноса соединен с четвертым выходом вычисли тельной ячейки, причем первые выходы вычислительных ячеек каждой строки матрицы соединейы с первыми входами последующих вычислительных ячеек той же строки матрицы-, первые входы вычислительных ячеек первого столбца матрицы яззляются входами множителя устройства, вторые входы вычислитель ных ячеек первой строки матрицы являются входами множимого устройства, третьи входы вычислительных ячеек , первой строки матрицы являются входа ми нулевого значения устройства, а третьи выхода вычислительных ячеек последней сшроки матрицы являются выходами устройства, четвертые выходы вычислительных ячеек каждой стро ки матриц соединены последовательно с четвертыми- в-хо; ами предыдущих вычислительных ячеек той же строки мат рицы, вторые выходы вычислительных ячеек каждой строки матрицы соединены соответственно с вторыми входами вычислительных ячеек последующих строк последующих столбцов матрицы, а вторые вЫходы вычислительных ячеек последнего столбца матрицы соединены с вторыми, входами вычислительных ячеек первого столбца последующих строк матрицы, третьи выходы вычислительных ячеек каждой строки матрицы соединены соответственно с третьими входсши вычислительных ячег ек последующей строки тех же столбцов матрицы, четвертые выходы вычислитейных ячеек первого столбца каждой строки Матрицы соединены с четвертыми входами вычислительных ячеек последнего столбца той же. строки матрицы. На фиг. 1 представлена блоксхема устройства; на фиг. 2 - блоксхема вычислительной ячейки. Устройство содержит матрицу вычислительных ячеек 1, входы 2-4, выходы 5. Каждая вычислительная ячейка 1 содержит одноразрядный сумматор 6 и элемент И 7. Первые выходы вычислительных ячеек 1 каждой строки матрицы соединены с первыми входами последующих вычислительных ячеек 1 той же строки матрицы, первые входы вычислительных ячеек 1 первого столбца матрицы являются входалш 2 устройства, вторые выходы вычислительных ячеек 1 каждой строки матрицы соединены соответственно с вторыми входа- Mit вычислительных ячеек 1 последующих строк последующих столбцов матрицы, вторые входы вычислительных ячеек 1 первой строки матрицы являются входами 3 устройства, вторые выходы вычислительных ячеек 1 последнего столбца матрицы соединены с вторыми входами вычислительных ячеек 1 первого столбца последующих строк матрицы, третьи выходы вычислительных ячеек 1 каждой строки матрицы соединены соответственно с третьими входами вычислительных ячеек 1 последующей строки тех же столбцов матрицы, третьи входы вычислительных ячеек 1 первой строки матрицы являются входами 4 устройства, третьи выходы вычислительньЬс ячеек 1 последней стро- ки матрицы являются выходами 5 устройства, четвертые выходы вычислйтеяьных ячеек 1 ка}кдой строки матрицы соединены с четвертыми входами предьиу- щих- вычислительных ячеек 1 той же строки матрицы, четвертЕое выходы вычислительных ячеек Г первого столбца каждой строки матрицы соединены с четвертыми входгми вычислительных ячеек 1 последнего столбца тех же строк матрицы. Первый и второй входы вычислительной ячейки 1 соединены соответственно с первым и вторым входами элемента И 7, выход которого соединен с первым из входов одноразрядного сумматора б, третий и четвертый вхо ды вычислительной ячейки 1 соединен соответственно с вторым и третьим входами одноразрядного cyNBiaTopa 6, выход суммы которого соединен с тре тьим выходом вычислительной ячейки а выход переноса соединен с четвертым выходом вычислительной ячейки 1 Число вычислительных ячеек в каж дои строке матрицы и число строк ус ройства определяются как in, где m разрядность множимого и множителя. Кратко изложим алгоритм перемнож ния двоичных операндов в обратных кодах с неявной коррекцией произве дения, который используется в устройстве . Пер емножение двоичных операндов в oбpflтныx кодах. Представление двоичных операндов в обратных,кодах необходимо для выполнения опергщии умножения отрицательных двоичных операндов. Представление отрицательных двои ных операндов в обратном коде имеет f,. (1.2 Г- ,а, г-Г./а где m - раз1 ядность операндов, /а|модуль двоичного операнда. Произведение двух отрицательных двоичных операндов есть псевдопроиз ведение fa-- V- b --rt/;(%2--0/ Для получения прааильного резуль тата в процессе выполнения умножения выполняется коррекция, т.е. к псевдопроизведению прибавляется выражение , -Г(2 - а-)- - (2 - (2 - 2- |с I . При умножении двоичных операндов в обратных кодах в устройстве за . счет соответствующих внутриматричны соединений коррекция выполняется неявно в процессе умноженияi резуль тат получается в овратнсж коде. Пример. Множимое 1. 1101011111 -5 Инояситель 1. 0100011111 -23 Состояние 1 1 1101011111 выходов О 0000000000 выходов 1 1111010111 элементов О 0000000000 О 0000000000 и каждой О OOOOOOOOQO . О 0000000000., roiiiiiliio строки 01011111111 матрицы. 10101111111 35 з2 1 101011111J О 0001110011 + 115 1024 Перемножение двоичных операндов в прямых кодах,Так как представление положительных двоичных операндов в обратном коде совпадает с их представлением в прямом коде, операция йыполняется вышеуказанным способам. Операция умножения двоичных операндов с разными знаками, представленных в обратных кодах, выполняется аналогичным образом. Устройство работает следующим образом. При выполнении операции умножения двоичных т-разргщных операндов в обратных кодах от старших разрядов множителя на входы 2 устройства поступают разряды множителя, причем знаковый разряд множителя поступает .на первый вход вычислительной ячейки 1 первой строки первого столбца матрицы, на последующие (m-l) первых входов вычислительных ячеек 1 последумдих строк первого столбца матрисщ поступают разряды множителя в порядке убывания их весов. На входы 3 устройства поступают разр}вды множимого, причем знаковый разряд множимого поступает на ВТОРОЙ вход вычислительной ячейки 1 первой строки первого столбца матрицы, (m-l) разрядов множимого поступают на вторые входы 2 вычислительных ячеек 1 первой строки последукнцих столбцов матрицы в порядке убывания их весов. При этом диапазон изменения кодов множимого и множителя ограничивается разрядагли кода произведения. Ыа входы 4 устройства подается код О. Элементы И 7 вычислительных ячеек 1 первой строки матрицы фррмируют частичное произведение старшего разряда множителя на множимое. Одноразрядные сумматоры б вычислительных ячеек 1 кгшдой строки матрицы производят суммирование частичных произведений. Окончательный результат операции - произ ведение в обратном коде с разрядностью m формируется на выходах сумм одноразрядных .сумматоров б вычислительных ячеек 1 последней строки матрицы, являкицихся выходами 5 устройства. Выполнение операции умножения т-раэрядных двоичных операндов в прямых кодах от старших разрядов множителя выполняется аналогичныл образом, так как представление положительного числа в обратном коде совпадает с его представлением в прямом коде. Таким ббразом, пре; агаемое устройство обладает расширенной областью применения по сравнению с известным и позволяет произвести неявную коррёкцию результата в процессе умножения. Формула изобретения Матричное устройство для умножени ;содержащее магрицу вычислительных йчеек, казэдая из которых содержит элемент И и одноразрядный сумматор, причем первый и второй входы вычислительной ячейки соединены соответст венно с первым и вторым входами элемента И, первый и второй входы вычис лительйой ячейки соединены с первым и вторым выходами вычислительной яче ки соответственно, выход элемента И соединен с первым входом однораэряд ного сумматора, третий и четвертый :входы вычислительной ячейки соединены соответственно с вторым и третьим входами одноразрядного сумматора, вы ход суммы которого соединен с третьи Iвыходом вычислительной ячейки, .а выход переноса соединен с четвертым выходом вычислительной ячейки, причем первые.ВЫХОДЫ вычислительных яче ек каждой строки матрицы соединены с первыми входами последующих вычислительных ячеек той же строки матриц первые входы вычислительных ячеек InepBoro столбца матрицы являются входами множителя устройства, вторы входы вычислительных ячеек первой строки матрицы являютсй входами мно жимого устройства, третьи входы .вычислительных ячеек первой строки матрицы являются входагли нулевого значения.устройства, а третьи вькоды вычислительных ячеек последней строки матрицы являются выходами

jJ- U Д

J ii . устройства, четвертые выходы вычисительных ячеек каждой строки матрицы соединены последовательно с четвертъал1 входами прбдьюущих вычислительных ячеек той же строки матрицы, отличающееся тем, что, с целью расширения области применения устройства за счет как прямых, так и обратных кодов входных операндов вторые выходы вычислительных чеек каждой строки матрицы соединены соответственно с вторыми входами вычислительных ячеек последуюпщх строк последуштх столбцов матрицы, а вторые выходы вычислительных ячеек последнего, тупают разрядысоединены с вторыми входами вычислительных ячеек. первого столбца последующих строк матрицы, третьи выходы вычислительных ячеек каждой ,строки матрицы сое динены соответствённо с третьими входами вычислительных ячеек последукяцей строки тех же столбцов матрицы, четвертые выходы вычислительных ячеек первого стсхпбца каждой строки матрицы соединены с четвертыми входами вычислительных ячеек последнего столбца той же строки матрищл. Источники информации, принятые во внимание при экспертизе 1.Карцев М.А. Арифметика ЦИФРОВЫХ мамин. М., Наука, 1969, с. 448. 2.Gehwei ler wn 1 lam F. eta. CMOS/SOS correlator and muttlpller. Proc IEEE Nat. Aerospace and Elect ron. Couf (NAECON , Dayton, ig pp. 252-259.° , 3.Карцев М.А. Арифметика цифровьк машин. М., Наука, 1969,с. 438 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1981 |

|

SU960803A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750484A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750485A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

Авторы

Даты

1982-11-07—Публикация

1981-02-06—Подача