С/

с

Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении арифметических устройств ЦВМ, в системах управления и специализированных устройствах обработки информации для преобразования позиционного кода из системы счисления с одним основанием в систему счисления с другим основанием.

Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования в код произвольной q-й системы счисления, а также повышение быстродействия.

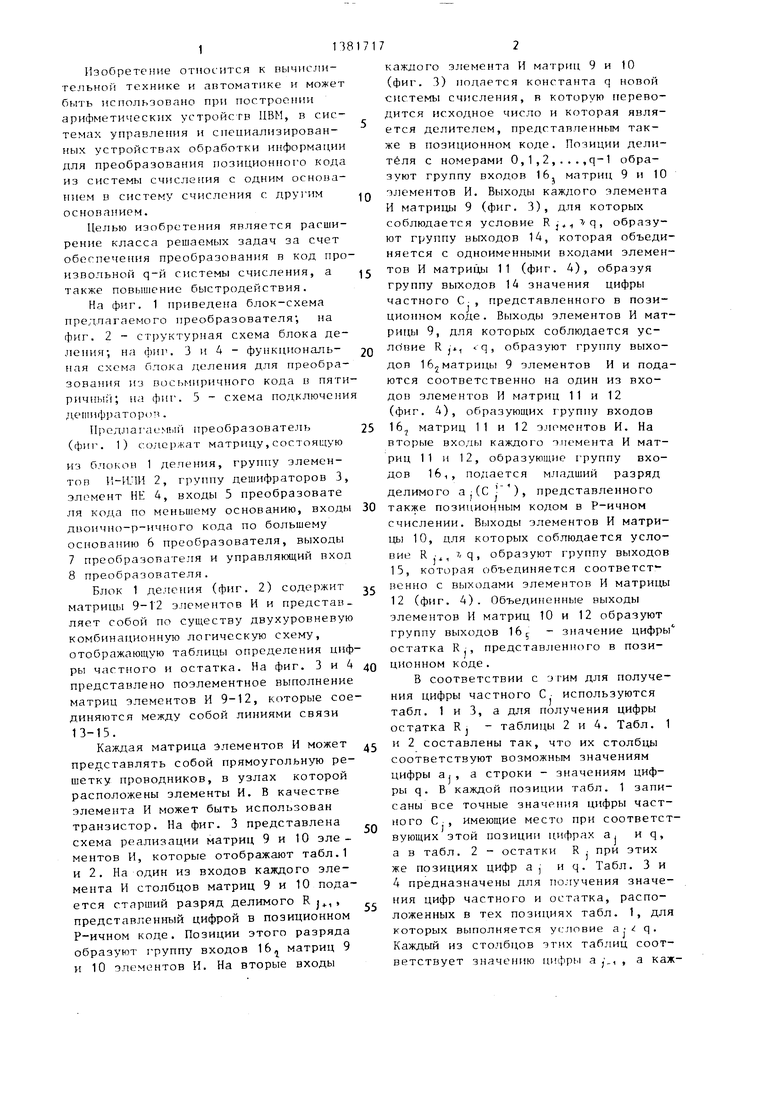

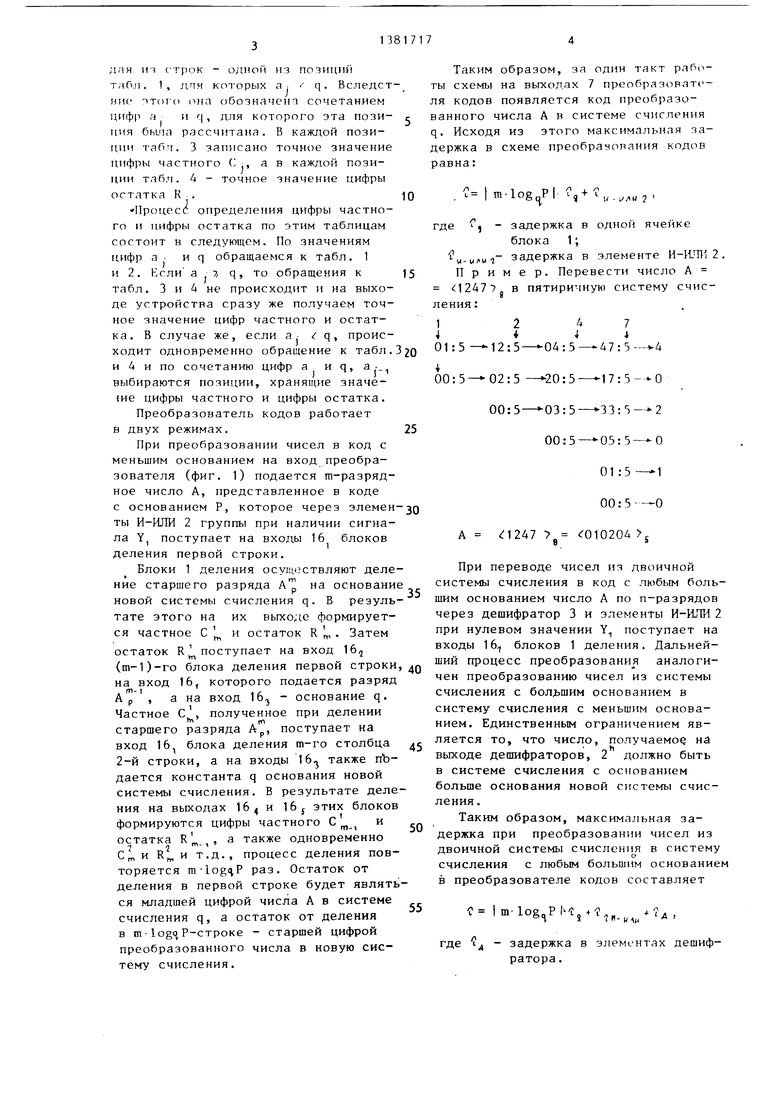

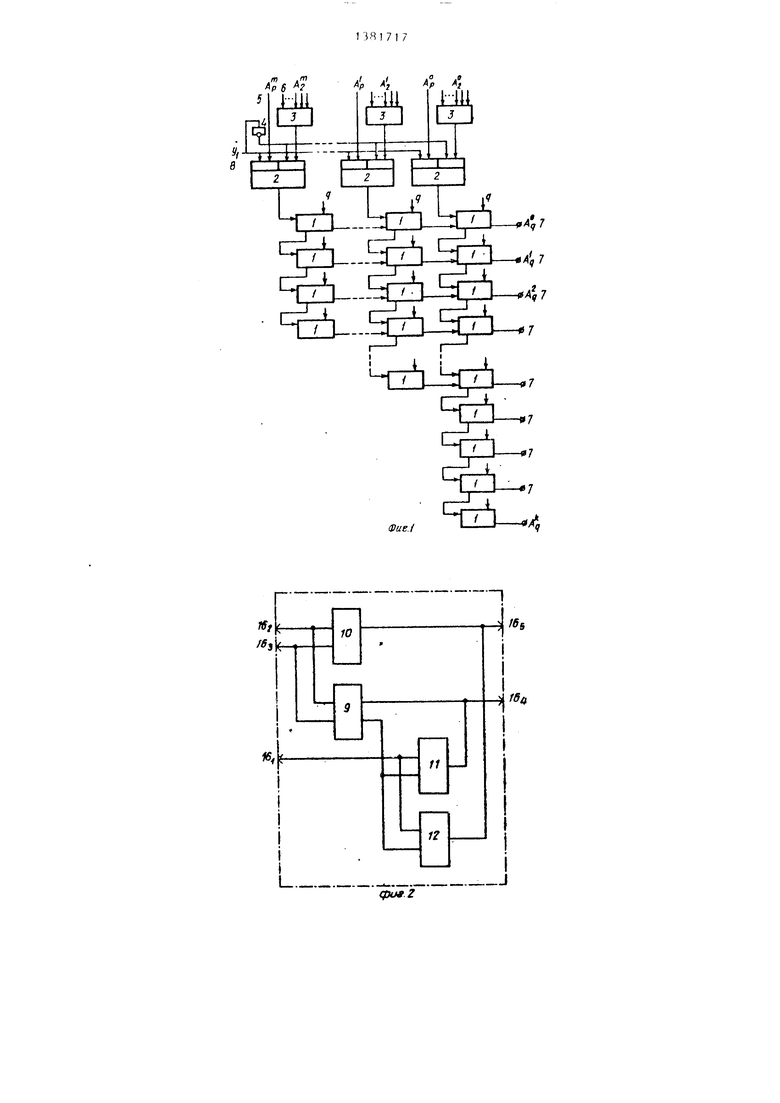

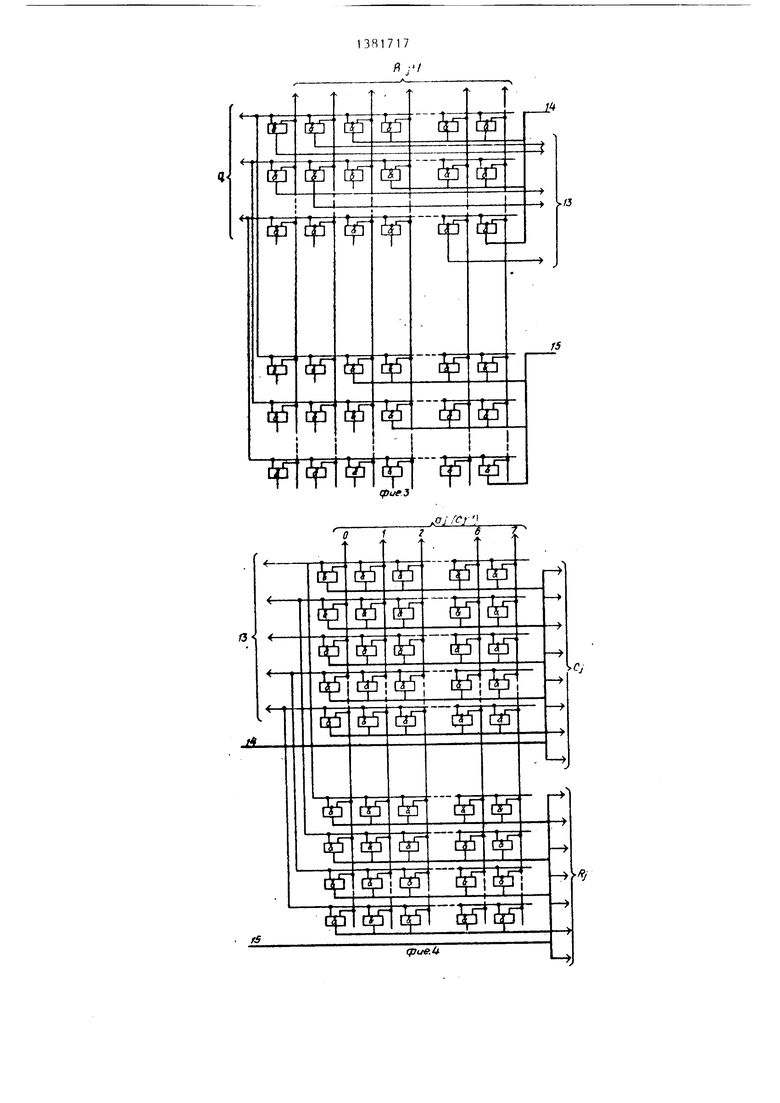

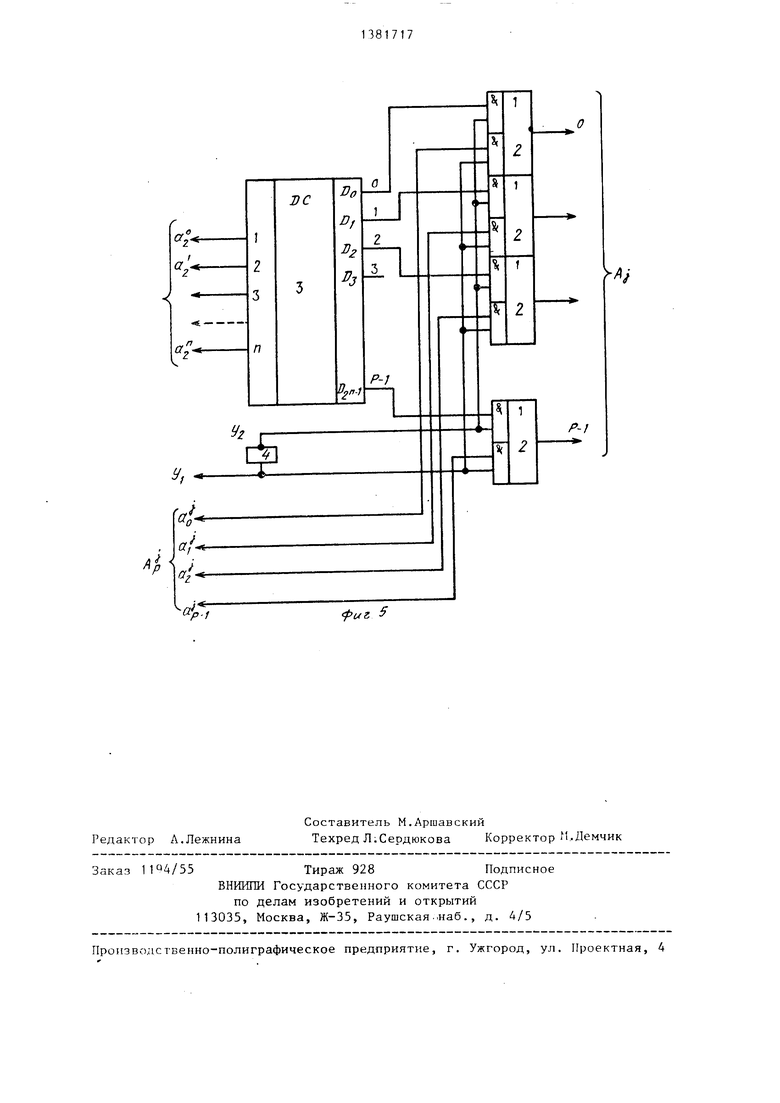

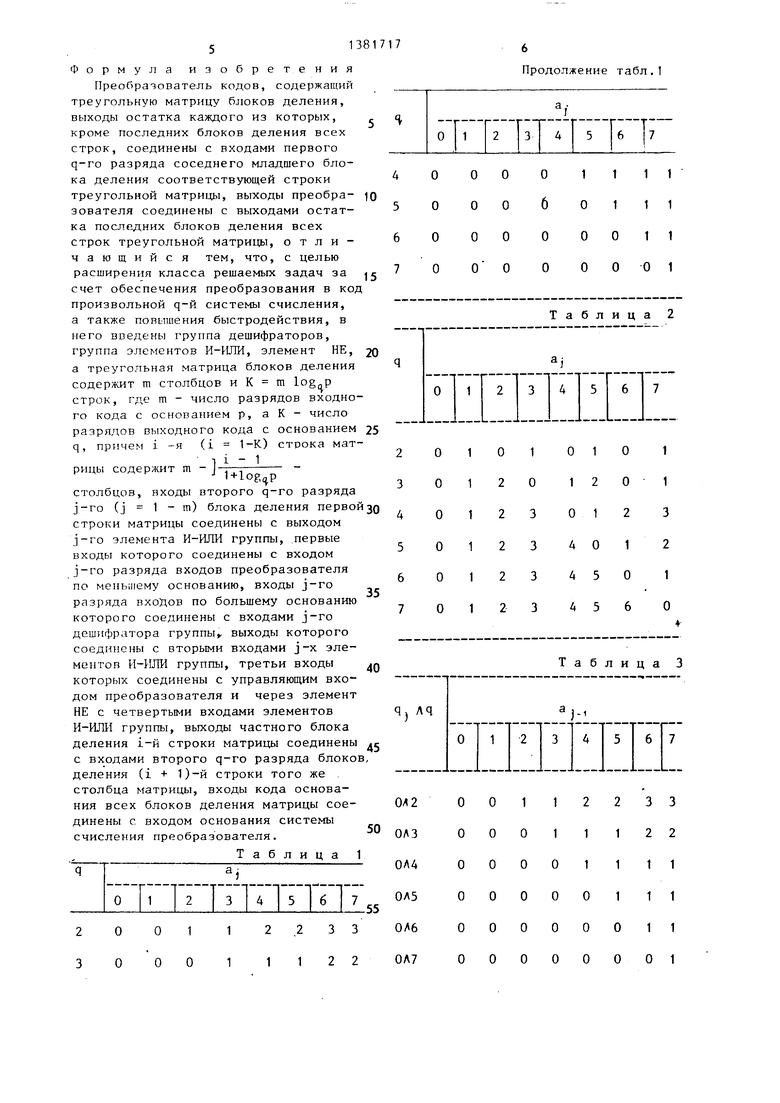

На фиг. 1 приведена блок-схема предлагаемого преобразователя; на фиг. 2 - структурная схема блока деления; на фиг. 3 и А - функциональ- ная схема блока деления для преобразования из восьмиричного кода в пятиричный; на фиг. 5 - схема подключени дешифраторов.

Предлагаемый преобразователь (фиг. 1) содержат матрицу,состоящую

из блоков 1 деления, гругпту элементов 1 -И 1И 2, группу дешифраторов 3, элемент НЕ 4, входы 5 преобразовате ля кода по меньшему основанию, входы двоично-р-ичного кода по большему основанию 6 преобразователя, выходы

7преобразователя и управляющий вход

8преобразователя.

Блок 1 деления (фиг. 2) содержит матрицы 9-12 элементов И и представляет собой по суш,еству двухуровневую комбинационную логическую схему, отображаюш,ую таблицы определения цифры частного и остатка. На фиг. 3 и 4 представлено поэлементное выполнение матриц элементов И 9-12, которые соединяются между собой линиями связи 13-15.

Каждая матрица элементов И может прер,ставлять собой прямоугольную решетку цроводников, в узлах которой расположены элементы И. В качестве элемента И может быть использован транзистор. На фиг. 3 представлена схема реализации матриц 9 и 10 элементов И, которые отображают табл.1 и 2. На один из входов каждого элемента И столбцов матриц 9 и 10 подается старший разряд делимого Rj, представленный цифрой в позиционном Р-ичном коде. Позиции этого разряда образуют группу входов 16 матриц 9 и 10 элементов И. На вторые входы

каждого элемента И матриц 9 и 10 (фиг. 3) подается константа q новой системы счисления, в которую переводится исходное число и которая является делителем, представленным также в позиционном коде. Позиции делителя с номерами О,1,2,...,q-1 образуют группу входов 16j матриц 9 и 10 элементов И. Выходы каждого элемента И матрицы 9 (фиг. 3), для которых соблюдается условие , образуют группу выходов 14, которая объединяется с одноименными входами элементов И матрицы 11 (фиг. 4), образуя группу выходов 14 значения цифры частного С., представленного в позиционном коде. Выходы элементов И матрицы 9, для которых соблюдается ус- ло вие R j4, q, образуют группу выходов 16jматрицы 9 элементов И и подаются соответственно на один из входов элементов И матриц 11 и 12 (фиг. 4), образующих группу входов 16, матриц 11 и 12 элементов И. На вторые входы каждого элемента И матриц 11 и 12, образующие группу входов 16,, подается младший разряд делимого aj(Cj ), представленного также позиционным кодом в Р-ичном счислении. Выходы элементов И матрицы 10, для которых соблюдается условие R .-4, q, образуют группу выходов 15, которая объединяется соответственно с выходами элементов И матрицы 12 (фиг. 4). Объединенные выходы элементов И матриц 10 и 12 образуют группу выходов 16 - значение цифры остатка R., представленного в позиционном коде .

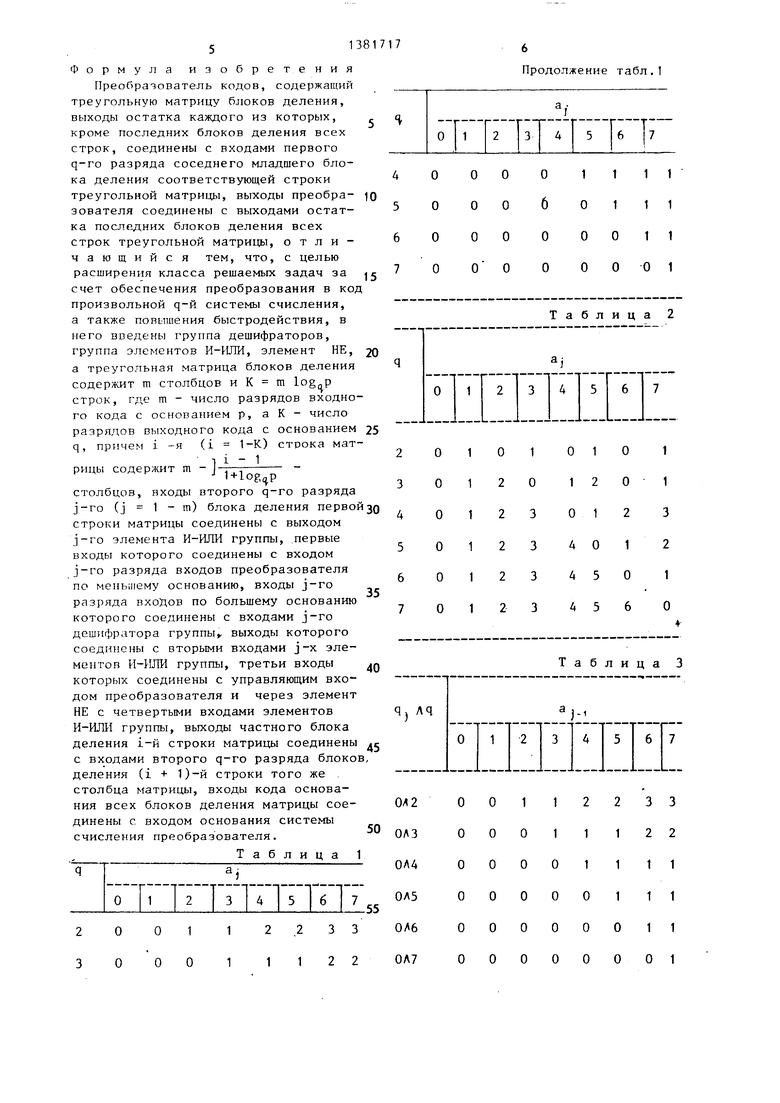

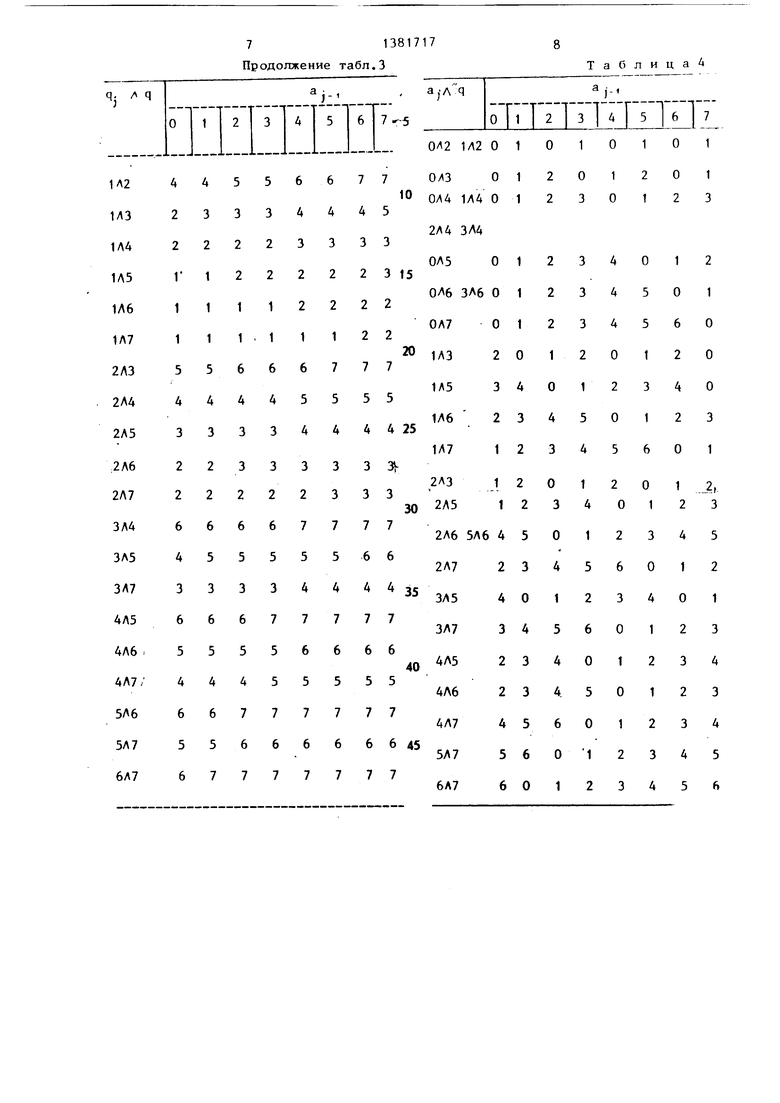

В соответствии с эгим для получения цифры частного С- используются табл. 1 и 3, а для получения цифры остзтка RJ - таблицы 2 и 4. Табл. 1 и 2 составлены так, что их столбцы соответствуют возможным значениям цифры вр а строки - значениям цифры q. В каждой позиции табл. 1 записаны все точные значения цифры частного С., имеющие место при соответствующих этой позиции цифрах а, и q, а в табл. 2 остатки R при этих же позициях цифр а , и q. Табл. 3 и 4 предназначены для получения значения цифр частного и остатка, расположенных в тех позициях табл. 1, для которых выполняется условие а : q . Каждый из столбцов этих таблиц соответствует значению цифры а у., , а кажляя m с трок - ОД11ОЙ из позиции таОл. 1, для которых а- q. Вследствие ттогч она обозначена сочетанием цифр а и с|, для которого эта пози- НИЯ 6huia рассчитана. В каждой позиции . 3 записано точное значение цифры частного С, , а в каждой позиции табл. 4 - точное значение цифры остатка R .

Процесс, опредедеция цифры частного и цифры остатка по этим таблицам состоит в следующем. По значениям цифр а . и q обращаемся к табл. 1 и 2. Ксли 37, q, то обращения к табд. 3 и 4 не происходит и на выходе устройства сразу же получаем точное значение цифр частного и остатка. В случае же, есди а- г q, происходит одновременно обраи1ение к табл. и 4 и по сочетанию цифр а и q, а выбираются позиции, хранящие значе- {ие цифры частного и цифры остатка.

Преобразователь кодов работает в двух режимах.

При преобразовании чисел в код с меньщим основанием на вход преобразователя (фиг. 1) подается т-разряд- ное число А, представденное в коде с основанием Р, которое через элемен ты И-ИЛИ 2 группы при наличии сигнала Y, поступает на входы 16 блоков деления первой строки.

Блоки 1 деления осущс ствляют деление старшего разряда А Г на основани новой системы счисления q. В результате этого на их выходе формируется частное С и остаток R . Затем остаток R поступает на вход 16 (m-l)-ro блока деления первой строки на вход 16, которого подается разряд , а на вход 16 - основание q. Частное с , полученное при делении

. гл

старшего разряда Ар, поступает на вход 16 блока деления т-го столбца 2-й строки, а на входы 16 также пЪ- дается константа q основания новой системы счисления. В результате деления на выходах 16 и 16j этих блоков формируются цифры частного С и

остатка R,

а также одновременно

Сг„ и R и т.д., процесс деления повторяется m-logi P раз. Остаток от деления в первой строке будет являться младшей цифрой числа А в системе счисления q, а остаток от деления в m log Р-строке - старшей цифрой преобразованного числа в новую систему счисления.

Таким образом, за один такт pa6ii- ты схемы на выходах 7 прсобразорате- ля кодов появляется код преобразованного числа А в системе счисления q. Исходя из этого максимальная задержка в схеме преобразования кодов равна:

: |m-log Р| С,+ С,

w - I /MJ 7

где j - задержка в одной ячейке

блока 1; «-млм1 задержка в элементе И-ИШ 2,

Пример. Перевести число А 12477 в пятиричную систему счисления:

02 : 5 -1 7 : 5 - О

4 7

; 4

04:5-47:5- -4

00:5- 03:5- 33:5- 2 00:5- 05:5- 0

01:5

1

Q

5

5

00:5--О А :i247 7 Г010204 5

При переводе чисел из двоичной системы счисления в код с любым боль- щим основанием число А по п-разрядов через дешифратор 3 и элементы И-ИЛИ 2 при нулевом значении Y поступает на входы 16 блоков 1 деления. Дальнейший процесс преобразования аналогичен цреобразованию чисел из системы счисления с большим основанием в систему счисления с меньщим основанием. Единственным ограничением является то, что число, получаемо ни выходе депшфраторов, 2 должно быть в системе счисления с основанием больше основания новой системы счисления.

Таким образом, максимальная задержка при преобразовании чисел из двоичной системы счисления в систему

С7

счисления с любым большим основанием в преобразователе кодов составляет

С |т.,.,.7д,

где - задержка в элемс-нтах дешифратора .

Формула изобретения Преобразователь кодов, содержащий треугольную матрицу блоков деления, выходы остатка каждого из которых, кроме Последних блоков деления всех строк, соединены с входами первого q-ro разряда соседнего младшего блока деления соответствующей строки треугольной матрицы, выходы преобра- зователя соединены с выходами остатка последних блоков деления всех строк треугольной матри, отличающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения преобразования в ко произвольной q-й системы счисления, а также повышения быстродействия, в него введены группа дешифраторов, группа элементов H-tfflH, элемент НЕ, а треугольная матрица блоков деления содержит m столбцов и К m log.p строк, где m - число разрядов входного кода с основанием р, а К - число разрядов выходного кода с основанием q, причем i -я (i 1-К) строка мат 1 i - 1

рицы содержит m - -:-: 1+log p

столбцов, входы второго q-ro разряда j-ro (j 1 - m) блока деления перво строки матрицы соединены с выходом -го элемента И-ИЛИ группы, первые входы которого соединены с входом j-ro разряда входов преобразователя по мень 11ему основанию, входы j-ro разряда входов по большему основанию которого соединены с входами j-ro дешифратора группы выходы которого соединены с вторыми входами j-x элементов И-ЩШ группы, третьи входы которых соединены с управляющим входом преобразователя и через элемент НЕ с четвертыми входами элементов И-ИЛ11 группы, выходы частного блока деления i-й строки матрицы соединены с входами второго q-ro разряда блоко деления (i + 1)-й строки того же столбца матрицы, входы кода основания всех блоков деления матрицы соединены с входом основания системы счисления преобразователя.

Таблица

Продолжение табл,1

F TT T - FT

о о о

о

оо

оо

оо

о о

о

6

о о

1

о о о

1 1

о о

1 1 1 1 1 1 о 1

Таблица 2

2 3

4 5 6

7

О О О О О О

О1

2О

23

23

23

23

01 О

12 О 01 2 А О 1 450 456

1 1 3 2 1 О

Таблица 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь позиционного кода в двоичный код | 1982 |

|

SU1064276A1 |

| Преобразователь позиционного кода в код с большим основанием | 1987 |

|

SU1444959A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Устройство для деления | 1985 |

|

SU1332312A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Преобразователь позиционного кода из одной системы счисления в другую | 1986 |

|

SU1302438A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2025897C1 |

| Устройство для деления | 1985 |

|

SU1291974A1 |

| Преобразователь кода в код с большим основанием | 1985 |

|

SU1332537A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при построении арифметических устройств и преобразователей из системы счисления с одним основанием в систему счисления с другим основанием. Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования в код произвольной q-й системы счисления и повышение быстродействия. Постав- пенная цель достигается тем, что в преобразователь кодов, содержащий треугольную матрицу делителей, дополнительно введены группа элементов И-ИЛИ, группа дешифраторов, элемент НЕ. 4 табл. 5 ил. $

ОЛ7

00000001

т ,т Ар 6 Af

Фие.{

.;I

фив Z

;

I

CpiJfS

Р

Ж

CO

f

тТ rrY Vr

/5

TF JUrl ЛДГ

ф ф t

1381717 Я ,-/

.t4

G J

5

IS

ж

ж

..

I I

-

| Л-- . ^ - .. -.^nsTfy-;-;:.-; , ,. ^lii-i i _i; i iiCi" . . ,. ,BHb/.hoО. Ф. Лобов | 0 |

|

SU317061A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3535500, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

Авторы

Даты

1988-03-15—Публикация

1986-01-22—Подача