(Л

с:

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система обработки данных | 1987 |

|

SU1455342A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451712A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Адаптивная система обработки данных | 1988 |

|

SU1552195A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных комплексах и автоматизированных системах управления. Целью изобретения является увеличение пропускной способности системы за счет повышения степени распараллеливания процесса обработки входного потока данных. Поставленная цель достигается тем, что в систему введено N блоков выбора каналов, а в каждый из N блоков обработки введено L процессоров . 1 з.п. ф-лы, 12 ил. е

4 СД

оо

Изобретение относится к вычисли- тельной технике и может быть использовано в измерительно-вычислительных комплексах и автоматизированных системах управления на основе мультипроцессорных вычислительных систем.

Целью изобретения является увеличение пропускной способности системы за счет повьшения степени распараллеливания процесса обработки входного потока данных.

На фиг. 1 представлена схема системы j на фиг. 2 - схема блока обработки и процессора; на фиг. 3 - схема операционного блока и его система команд; на фиг. 4 - схема блока буферной памяти; на фиг, 5 - схема блока коммутации; на фиг. 6 - схема блока подключения магистралиJ на фиг. 7 - схема арифметико-логического блока с временной диаграммой и системой микрокоманд; на фиг. 8 - схема блока обмена с временной диаграммой и системой микрокоманд} на фиг. 9 - схема элементов коммутации; на фиг. 10-12 - блок-схемы алгоритмов, поясняющих работу системы.

Адаптивная система обработки данных содержит блок 1 памяти, блоки .2 обработки, блоки 3 выбора каналов, каждый из которых содержит приемопередатчики 4,5 и селектор 6 каналов.

Система имеет входы 7 задания режима работы системы, 8 сигналов запроса, системную магистраль 9 передачи сигналов, содержащую шину 10 сигналов разрешения, шину 11 адреса и шину 12 данных.

Блок 2 обработки имеет выход 13 запроса, вход 14 задания режима рабо ты, выход 15 разрешения, два информационных входа 16, 17, вход 18 разрешения, а также выходной разъем 19. Блок 2 обработки содержит процессоры 20, каждый из которых содержит блок 21 коммутации, элемент ИЛИ 22, блок 23 буферной памяти, операционный блок 24, элемент И 25, инвертор 26, элемент И 27 Блок обработки содержит также элементы И 28, 29 и локаль ную магистраль передачи сигналов, ко торая содержит шину 30 данных, шину 31 адреса, шину 32 сигналов выдачи, шину 33 сигналов приема, шину 34 сигналов захвата-ответа, шину 35 сиг налов запроса, шину 36 сигналов за- нятости. Блок 21 коммутации имеет задающий вход 37, вход 38 разрешения

10

15

20

25

выход 39 запроса, информационный вход 40, выход 41 разрешения, вход 42 запроса, выход 43 запуска, вход 44 обращения, выход 45 записи. Операционный блок 24 имеет выход 46 опроса, второй вход 47 запуска. Блок . 23 имеет дополнительно выходы 48-51. Процессор 20 имеет входы-выходы 52 данных, 53 адреса, 54 признака выдачи, 55 признака приема, вход 56 признака захвата, выход 57 признака ответа, выход 58 признака запроса, вход-выход 59 признака готовности.

Операционный блок 24 содержит блок 60 памяти, счетчик 61 команд, дешифратор 62, элемент ИЛИ 63, арифметико-логический блок 64, блок 65 обмена, блок 66 подключения магистрали. Арифметико-логический блок имеет выход 67 сигнала исполнения, информационный выход 68, вход 69 запуска, вход 70 кода микрокоманды, входы-выходы 71 данных, 72 признака выдачи, 73 признака приема. Блок обмена имеет выход 74 сигнала исполнения, вход 75 кода микрокоманды, вход. 76 внутреннего запуска, первый 77 и второй 78 входы внешнего запус- 30 ка, выход 79 захвата, вход 80 разрешения захвата..

Блок 23 буферной памяти содержит первый счетчик 81 адреса, счетчик 82 заполнения, второй счетчик 83 адреса, первый 84 и второй 85 дешифраторы адреса, первый входной регистр 86, первый блок 87 памяти, первый выходной регистр 88, второй входной регистр 89, второй блок 90 памяти, второй выходной регистр 91.

Блок 21 коммутации содержит элементы И 92-96 и элемент ИЛИ 97. Блок 66 подключения магистрали содержит элементы И 98-101, триггер 102 и ключевые элементы 103, 104.

Арифметико-логический блок 64 содержит приемо-передатчик 105, регистр 106, регистровую память 107, сумматор 108, сдвигатель 109, регистр 110 состояния, арифметический элемент 111 коммутации, дешифратор 112 микрокоманд, регистр 113 микрокоманд, формирователь 114 си 1хросиг- налов.

Блок 65 обмена содержит приемопередатчики 118-121, элементы 122, 123 коммутации, регистр 124, коммутатор 125, дешифратор 126 микрокоманд, формирователь 127 синхросигнй35

40

45

50

55

лов, элемент И 128, регистр 129 микрокоманд, элемент ИЛИ 130.

На фиг. 9 показан пример реализации элементов 111, 122, 123 коммутации, которые содержат элементы И 131-, 132, элемент ИЛИ 133.

Система работает следующим образом.

В системе в качестве заявок могу быть использованы идентифицированны выборки параметров,.последовательно поступающие р блок 1 памяти от многоканальных систем сбора информации При этом каждая заявка представляет собой совокупность номера (адреса) измерительного канала и выборки (значения параметра) по этому канал Номер канала используется в процессоре в качестве начального адреса програмг-1Ы обработки выборки,

В работе системы можно выделить два процесса, которые происходят асинхронно: процесс приема заявок и блока 1 памяти в блоки 2 обработки для последующей обработки, процесс собственно обработки заявок, которая производится в блоках 2 обработки.

В свою очередь, в зависимости от значения сигналов на щинах 14 задания режима работы магистрали 7 задания режима работы системы каждый блок 2 обработки может работать в одном из двух режимов: в режиме параллельной обработки (применяется для каналов с обработкой выборок по независимым алгоритмам) и в режиме последовательной обработки (для каналов с обработкой выборок по взаимозависимым алгоритмам). Ниже (при описании работы системы) предполагается, что все каналы разбиты предварительно на группы по числу блоков обработки, причем номера каналов одной группы используются как адрес, по которым в соответствующих селекторах 6 каналов записаны 1, а по остальным адресам селекторов каналов записаны О.

Прием заявок на обработку. Для приема заявок на обработку каждый блок обработки, который не загружен полностью, выставляет на выходе 13 запроса сигнал запроса. Запросы от блоков обработки по щине 8 сигналов запроса поступают на вход запроса блока 1 памяти. При этом выходы 13 запроса подключены к шине 8 запросов по схеме МОНТАЖНОЕ (ПРО

ВОДНОЕ) lUIH так, что при отсутствии запроса на выходе 13 хотя бы одного блока 2 обработки сигнал запроса на входе блока 1 памяти отсутствует, Этим обеспечивается обязательный прием заявки, выданной из блока 1 в один из блоков обработки, а при этом заявка не теряется.

Г

При наличии заявок и сигнала запроса на соответствующем входе блока 1 памяти последний выставляет на шинах 11, 12 адреса и данных коды номера канала и выборки очередной заявки и выдает по шине 10 сигнал разрешения, длительность которого превьшдает время цикла локальной магистрали передачи сигналов блоков обработки.

25

0

5

Под действием сигнала разрешения, поступающего с выхода блока 1 памяти на синхровходы селекторов каналов, на выходе 18 селектора 6 каналов одного из блоков 3 выбора каналов обязательно устаавливается еди- .ничный сигнал разрешения, который поступает на входы элементов И 28,29 соответствующего блока обработки. При этом цепь действия сигналов запроса от процессоров прерывается, т.к. на выходе элемента И 29 появляется нулевой сигнал. Таким образом, на время действия сигнала разрешения по связи 18 ни один из процессоров не может осуществить захват локальной магистрали передачи сигналов . Если на шине 36 отсутствует сигнал занятости, то сигнал разреше- 0 НИН проходит через элемент И 28. Если же сигнал разрешения по связи 18 поступает в момент, когда локальная магистраль уже занята (на шине 36 - единичный сигнал), то, поск оль- ку длительность сигнала разрешения превьш1ает длительность цикла локальной магистрали,в момент снятия сигнала занятости в конце этого цикла сигнал разрешения проходит на выход элемен- 0 та-И 28. С выхода элемента И 28 сигнал поступает на вход разрешения первого процессора рассматриваемого блока обработки и одновременно по связи 15 поступает на стробирующие 5 входы приемопередатчиков 4 и 5 соответствующего блока выбора каналов. В результате информация с шин 12 и 11 через приемопередатчики 4р5 по связям 16,17 подается соответственно

5

на шины 30,31 локальной магистрали передачи сигналов блока 2 обработки.

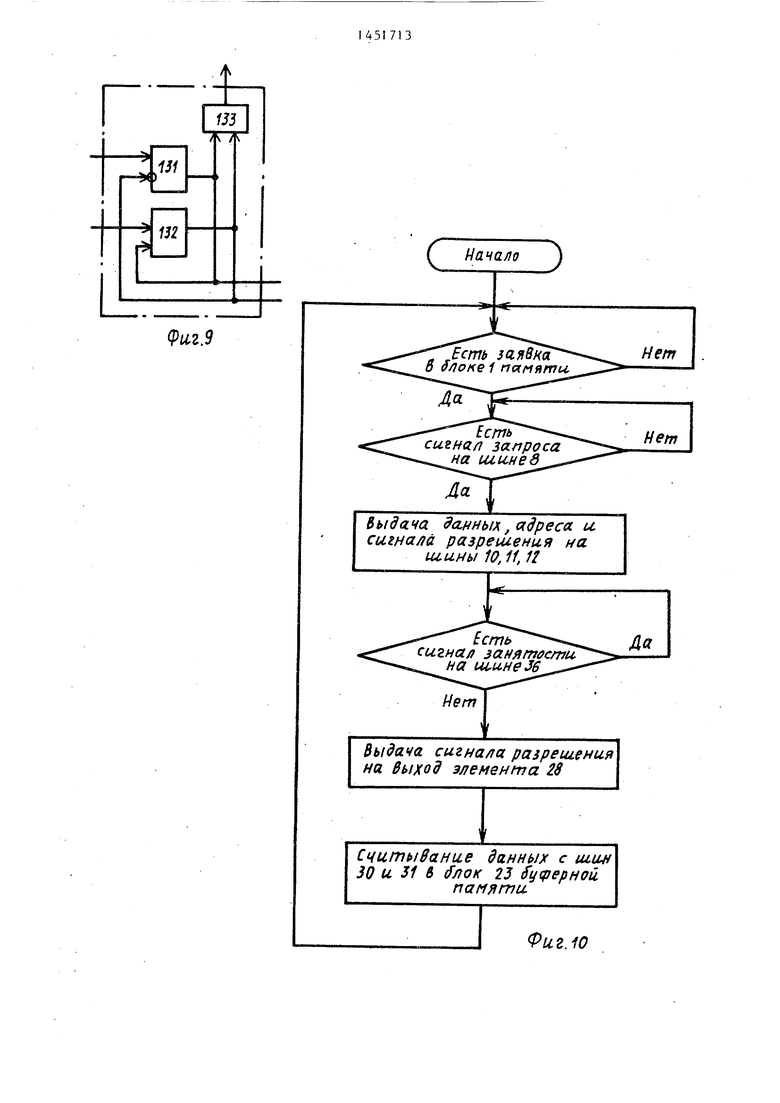

Цепь распространения сигнала разрешения, поступившего на вход разрешения первого процессора 20 блока 2 обработки, устроена таким образом, что этот сигнал проходит на вход 45 записи блока 23 буферной памяти или на вход 43 операционного блока одного из процессоров (какого именно зависит от режима работы блока обработки) и разрешает запись данных а соответствующий блок с шин 30, 31 локальной магистрали передачи сигналов. По окончании действия сигнала разрешения локальная магистраль освобождается. Таким образом, процесс приема заявок на обработку совмещен в общем случае с процессом обработки заявок (независимо от режима работы блоков обработки). Алгоритм работы системы при приеме заявок на обработку из блока 1 памяти показан на фиг.10.

Работа блока обработки в режиме параллельной обработки заявок.

В этом режиме на один блок обработки назначаются каналы, характеризующиеся обработкой выборок по независимым алгоритмам.

Исходное состояние блока 2 обработки: все процессоры 20 свободны, блок 23 буферной памяти пуст (т.е. значение сигнала на выходе 48 равно 1, а на выходе 49 - О), значение сигнала на входе 14 задания режима работы равно 1. В этом случае каждый процессор выдает сигнал запроса на выходе элемента ИЛИ 22, т.к. на выходе инвертора 26 сигнал равен 1 и он поступает на третий вход элемента ИЛИ 22, На первый вход этого элемента поступает сигнал 39 от блока 21 коммутации, который формируется из запросов последующих процессоров блока обработки. Сигнал разрешения, поступающий на вход первого процессора блока обработки, проходит последовательно через все блоки 21 коммутации и производит запись очередной заявки в блок 23 буферной памяти последнего процессора, выставившего запрос.

При появлении в блоке 23 буферной памяти хотя бы одной заявки сигнал Пуст на выходе 48 становится равным С, поэтому сигнал опроса с выхода 46 операционного блока 24 (ко14517136

торый формируется операционным блоком 24 всякий раз, когда он освобождается от обработки очередной заявки) по связи 47 производит считывание очередной заявки из блока 23 буферной памяти и включает операционный блок 24 в работу. Одновременно заканчивается сигнап опроса, 10 поступивший с выхода 46 операционно- . го блока.

0

5

Если блок 23 буферной памяти пуст, то свободный процессор при отсутствии запросов от последующих процес- соров может запускаться по связи 43, что позволяет производить прием заявки в операционный блок 24 непосредственно с щин 30, 31 локальной магистрали по сигналу разрешения. По , номеру канала, считанному в операционный блок 24, определяется программа обработки заявки (номер первой выполняемой микрокоманды). Если блок 23 буферной памяти заполнен, то сигнал .на выходе 49 этого блока становится равным 1, а на выходе 48 - О. Поэтому сигнал на выходе элемента И 26 равен О, что блокирует цепь прохождения сигнала разреше0 ния на выход 45 блока 21 коммутации соответствующего процессора, т.е. цепь записи заявок в блок 23 буферной памяти этого процессора. При этом не формируется сигнал запроса

5 по третьему входу элемента ИЛИ 22. В этом случае по окончании обработки заявки операционный блок 24 выставляет сигнал опроса на выходе 46, который с помощью элемента И 27 фор0 мирует сигнал считывания из блока 23 буферной памяти и запуска операционного блока 24 (по связи 47), а с помощью элемента И 25 формирует сигнал запроса, не дожидаясь окончания

5 цикла считывания из блока буферной памяти. Таким образом, в рассматриваемом случае осуществляется опережение запроса на подкачку блока буферной памяти (на один цикл считы0 вания). Так как длительность обработки заявок в общем случае является величиной произвольной (случайной) , то произвольной будет и последовательность включения процессос ров 20 в работу по мере их освобождения. Тем самым обеспечивается непрерывность работы всех процессоров и отсутствие простоев в их работе при условии их непрерывной загрузки.

I Алгоритм работы блока обработки в режиме параллельной обработки преставлен на фиг. 11.

Работа блока обработки в режиме

-ее

последовательной обработки. J . .

В этом режиме на один блок обработки назначаются каналы, которые характеризуются обработкой выборок по зависимым алгоритмам. При этом каждая заявка последовательно обслуживается в каждом процессоре блока обработки по частям, начиная с первого процессора этого блока.

I

Исходное состояние блока 2 обработки: все процессоры 20 свободны, блок 23 буферной памяти пуст (т.е. значение сигнала на выходе 48 равно 1, а на выходе 49 - О), значени сигнала на входе 14 задания режима равно О. В этом режиме сигнал за- проса на выходе каждого процессора 20 формируется так же, как и в параллельном режиме. Отличие состоит в том, что в последовательном режи- ме сквозная цепь прохождения запроса от предыдущего процессора к последующему от входа 42 на выход 39 блока 21 коммутации блокируется ну- левым значением сигнала задания режима на входе 37 блока 21. Поэтому сигнал на первом входе 39 элемента ИЛИ 22 всегда равен О. Таким образом, запросы на выходе 13 блока обработки в последовательном режиме формируются только от первого процессора 20 этого блока обработки. Появление сигнала разрешения на входе 38 разрешения блока 21 комму- тации первого процессора инициирует iзапись заявки по связи 45 в блок 23 буферной памяти первого процессора 20 блока 2 обработки. Если блок буферной памяти первого процессора пуст в момент появления сигнала разрешения, то по связи 43 инициируется прием заявки с шин 30, 31 в операционный блок 24 первого процессора и ее обработка в нем. Если бло 23 буферной памяти не пуст, то сигнал опроса на выходе 46 первого процессора при его освобождении формирует сигнал по связи 47,который запускает операционный блок 24, а так же передает в него из блока 23 буферной памяти очередную заявку, которую блок 24 начинает обрабатывать по соответствующему алгоритму час

5

0

5

5

0 0 5 0 5 0 g

138

тичной обработки. При этом сигнал

опроса с выхода 46 блока 24 снимается.

Блок 24 выполнения операций первого процессора 20 блока 2 обработки, выполнив первую часть алгоритма обработки заявки, вьщает с выхода обращения по связи 44 сигнал обращения в блок 21 коммутации. Если при этом на входе 42 запроса блока 21 имеется сигнал запроса от второго процессора, то блок 21 вьвдает с выхода 41 сигнал разрешения, поступающий на вход разрешения блока 21 второго процессора блока 2 обработки. По этому сигналу во втором процессоре рроисходят такие же действия, что и в первом процессоре . При этом в операционном блоке 24 второго процессора выполняются вторые части алгоритмов обработки заявки.

Аналогичным образом происходит работа остальных процессоров 20 блока 2 обработки в последовательном режиме. Алгоритм работы процессоров

20блока обработки в режиме последовательной обработки показан на

фиг. 12.

Режимы работы блоков обработки устанавливаются от внешних устройств путем установки соответствующих сигналов на шинах 14 задания режима работы магистрали 7 задания режима работы системы. Таким образом, в системе может быть организовано несколько различных режимов обработки, что позволяет системе эффективно адаптироваться к входным потокам разной структуры. Логика формирования сигналов, управляющих работой процессоров 20 в нужном режиме блока 2 обработки реализуется в блоке

21коммутации, а также в элементах ИЛИ 22 и 25-27.

Формула изобретения

914

второго приемопередатчиков каждого из N блоков выбора каналов подключены соответственно к входам-выходам данных и адреса блока памяти, информационный вход селектора канало каждого из N блоков выбора каналов подключен к входу-выходу адреса блока памяти, выход разрешения которого подключен к синхровходу селектора каналов каждого из N блоков выбора канала, выход селектора каналов i-fo блока выбора каналов(,...,N) подключен, к входу разрешения i-ro блока обработки, входы-выходы первого и второго приемопередатчиков i-ro блока выбора каналов подключены соответственно к входам-выходам данных и адреса i-ro блока обработки, выход разрешения которого подключен к входам разрешения первого и второго приемопередатчиков i-ro блока выбора каналов, выход запроса каждого из N блоков обработки подключен к входу запроса блока памяти, входы задания режима каждого из N блоков обработки являются соответствующими входами системы, , группа входов- выходов адреса, данных и управления каждого из N блоков обработки является входом-выходом системы.

обработки, выход первого элемента И подключен к входу разрешения первого процессора и является выходом g запроса блока обработки, выход разрешения j-ro процессора является входом разрешения ()-ro процессора, выход запроса первого процессора является выходом запроса блока обра- 0 ботки, вход запроса j-ro процессора подключен к выходу запроса (j-t-D-ro процессора, входы задания режима каждого из L процессоров объединены между собой и являются выходом зада- 15 ния. режима блока обработки, входы- выходы данных и адреса каждого из L процессоров соединены между собой и являются соответственно входами и выходами данных и адреса блока 2Q обработки, выходы сигналов запроса каждого из L процессоров соединены между собой и подключены к входу второго элемента И, выход которого подключен к входу захвата первого 25 процессора, выход ответа j-ro процессора подключен к входу захвата (j+1)-ro процессора, входы-выходы занятости каждого из L процессоров соединены между собой и подключены 3Q к второму инверсному входу первого элемента И, входы-выходы сигналов выдачи и приема каждого из L процессоров объединены между собой, входы- выходы данных адреса, вьщачи приема, занятости, выход запроса каждого из L процессоров и выход ответа L-ro процессора являются соответствующими входами-выходами блока обработки.

Систена команд б/юна 2.

иг.З

( - ULLnpOKOMandOL

11 „ |Л-У7г

w UЯ

SJ

t

J/

от 65

U

i

LI

r

«Put.

ф,5И

/rff

i

5{ 21

Ov

S

vj

«

«S

ro «

V

«: «t

I.

I

ft) 5S

:S

5r

f

:c i:

Cj 5t

i ii

g

ro

:i

X

Й i t; 5J f

С5

«

n

К 66 ffm66 от ВО

временная 9ис1грагчп г работы fffona 65

TTTZO Запиа 8129

Сигнет на. 32 Сигнал на 33

от 62 om2i omZl

Система, микрокоманд лона 65

9ll2.d

9u,z.S

С Начало j

Выдача да,нны)( cfdpeca и, сигна/fa разрешения на luuHbi 10,11,12

Выдача сигнала разрешения на Выход элемента 28

Ct umt /BaHiie данны е с шш/ 30 и 31 6 лок 23 fyqiepHOu. памяти.

Фиг. 10

Г Начапо jj

Вндачи си на/ia запроса из fnoHa I по связи, 15

с/я

. сигня/г разре шения на в)(оде $/)океГ Z oSpaSornKU

Да

прием заявни uj лока i в лон Z ofpa ofnKti

заявки.

Нет

Фиг. 11

Выдача сигнала запроса. /77 tipoi eccopa

Есть

сигнал на. входе разрешения npoifeccopa

Поием за(1вни,. Частичная оопаоотка. jaftBHu. Выдача сиг на/ а of ращение по cdfsi

Ест

сигнал запро от последующе to процессора

---

Ла

Выдача реуультата частичной 0(fpa fotrjKu в последи- ющци процессор

Редактор И.Рыбченко

Составитель Б.Резван Уехред А.Кравчук.

Нет

Нет

9и.г. П ,

Корректор О.Кравцова

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1987-06-11—Подача