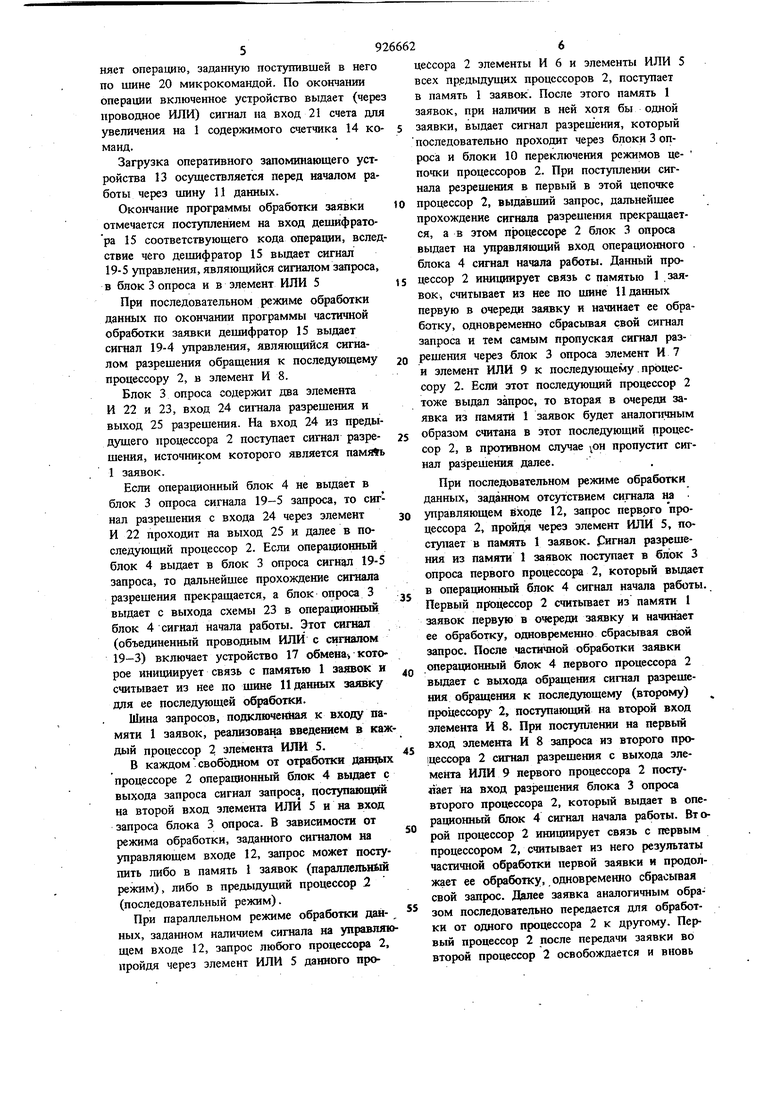

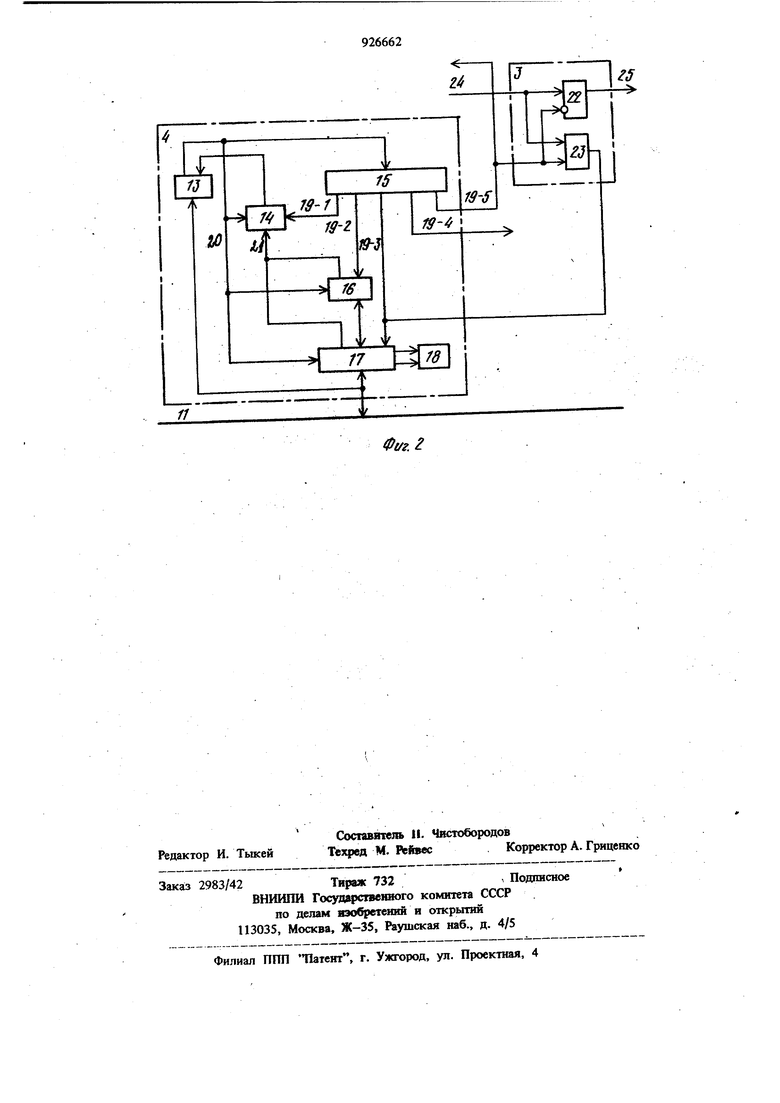

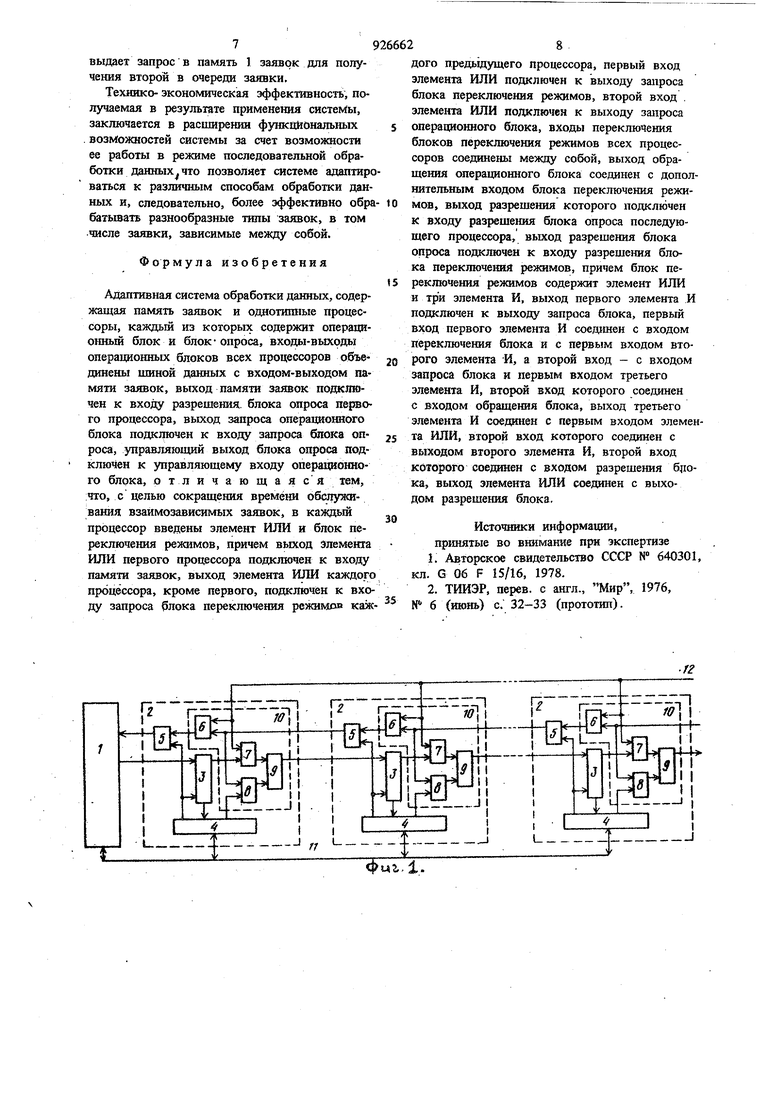

Изобретение относится к вь1числительной технике, в частности к адаптивным вычислительным системам, перестраивающим .свою структуру в зависимости от заданных спОсо бов обработки данных, и может быть приме нено в измерительно-вычислительных комплексах и в автоматизированных системах управления технологическими, процессами. Известно адаптивное вычислительное устройство, содержащее многофункциональные. модули обработки, блоки памяти, блок конт роля, коммутаторы, элементы И, ИЛИ, НЕ, кольцевые регистры, в котором могут быть организованы как последовательный, так и параллельный способы вычисления функций, и, кроме того, осуществляется перенастройка модулей при их отказах 1. Недостатками известного устройства являются значительные аппаратурнь е затраты и сложная логика организации реконфигурации многофункциональных модулей. Наиболее близкой к предлагаемот Цо технической сущности является система обработ содержащая центральный процессор и несколько устройств ввода-вывода. Известная система может обслуживать как системные щ ерываш1я от устройств вводавывода, так и заявки на обработку данных. В последнем случае известная система обработки данных содержит память заявок и однотшшые процессоры, каждый из которых содержит операхшонный блок и блок опроса, причем входы-выходы операционных блоков всех процессоров объединены щиной данных с входом-выходом памяти заявок, вход памяти заявок подключен к шине запросов, выход - к первому входу блока опроса первого процессора, выход операционного блока в каждом процессоре подключен к ишне запросов и к второму входу блока опро-. са, пертый выход которого соединен с входом (шерационного блока. В этой системе обработки данных операциОШ1ЫЙ блок каждого процессора по шине запросов выдает запрос на получе ше заявки из памяти заявок для ее обслужива1шя. При наличии запроса память заявок выдает сигнал разрешения, который последовательно проходит через блоки опроса, всех- процессоров в направлении снижения приоритета. Первый процессор из числа выдавших запрос останавливает дальнейшее прохождение сигнала раз- . решения, устанавливает связь с памятью заявок, считывает из нее по шиле данных первую в очереди заявку и сбрасывает свой запрос, разрешая тем самым считывание следуюших заявок другими процессорами, выдавшими запросы. Считанная в первый процес сор заявка обрабатывается в его операционном блоке до конца, после чего этот процессор вновь выдает запрос. В случае отказа процессора он не выдает запрос, тем самым пропуская сигнал разрешения к последующим процессорам. Процессоры идентичны и каждый из них может обработать любую заявку, позтому система адап тируется к отказам отдельных процессоров, а распределение заявок по процессорам носит случайный характер. В системе одновременно MorjT обрабатываться несколько независимых заявок. Таким образом, в системе реализуется параллельный способ обработки, заявок { Основным недостатком известной системы является функциональная ограниченность ее только параллельным способом обработки. В ней невозможна организация, последовательного способа обработки, который для Некоторых типов заявок (в частности для заявок, зависимых между собой) более эффективен. Цель изобретения - сокращение времени обслуживания взаимозависимых заявок. Указанная цель достигается тем, что в адап тивную систему обработки данных, содержащую память заявок и однотипные процессоры, каждый из которых содержит операционный блок и блок опроса, входы-выходы операционных блоков всех процессоров объединены шиной данных с входом-выходом памяти заявок, выход памяти заявок подалючен к входу разрешения блока опроса первого процессора, выход запроса операционного блока подаслючен к входу запроса блока опроса, управляющий выход блока опроса подключен к управляющему вХоду операционного блока, введены в каждый процессор элемент ИЛИ и блок переключения режимов, причем выход элемента ИЛИ первого процессора подключен к входу памяти заявок, выход элемента ИЛИ каждого процессора, кроме первого, подключен к входу запроса блока переключения режимов каждого предыдущего процессора, первый вход элемента ИЛИ подключен к выходу запроса блока переключения режимов, вто рой вход элемента ИЛИ подключен к, выходу запроса операционного блока, входы переключения, блоков переключения режимов всех нроцессоров соединены между собой, выход обрашения операционного блока соединен с входом обращения блока переключения режимов, выход реарешения которого иодключен к входу разрешения блока опроса последующего процессора, выход разрешения блока опроса подключен к входу разрешения блока переключения режимов, причем блок переключения режимов содержит элемент ИЛИ и три элемента И, выход первого элемента И подключен к выходу запроса блока, первый вход первого элемента И соединен с входом переключения блока и с первым входом второго элемента И, а второй вход с входом запроса блока и первым входом третьего элемента И, второй вход которого соединен с входом обращения блока, выход третьего элемента И соединен с первым входом элемента ИЛИ, второй вход которО1о соединен с выходом второго элемента И, второй вход которого соединен с входом разрешения блока, выход элемента ИЛИ соединен с выходом разрешения блока. На фиг. 1 представлена блок-схема адаптивной системы обработки данных; на фиг. 2блок-схема операционного блока и блока опроса. Система содержит память 1 заявок, процессоры 2, блок 3 опроса, операционный блок 4, элемент ИЛИ 5, элементы И 6-8, элемент ИЛИ 9, блок 10 переключения режимов, шину 11 данных, управляющий вход 12 системы. Операционный блок 4 содержит оперативное запоминающее устройство 13, счетчик 14 команд, дешифратор 15, арифметически-логическое устройство 16, устройство 17 обмена, узел 18 захвата магистрали, сигналы 19 управления, шину 20, вход 21 счета. Программы обработки хранятся в оперативном запоминающем устройстве 13, запрос к которому производится по адресу, сформированному в счегшке команд 14. Команда, поступающая из оперативного запоминающего устройства 13, состоит из кода операции и адреса перехода, который по шине 20 передается в счетчик команд 14, или микрокоманды, которая по шине 20 передается для вьтолнения в арифметически-логическое устройство 16 или в устройство обмена 17. Код операции дешифрируется в дешифраторе 15. При выполнении команды перехода дешифратор 15 сигналом 19 управления защ1сывает адрес перехода с шины 20 в счетчик команд 14. При выполнении других команд дешифратор 15 сигналами 19-2 или 19-3 управления включает соответственно арифметическилогическое устройство 16 или устройство 17 обмена. Затем включенное устройство выпол59266626

няет операцию, заданную поступившей в негоцессора 2 элементы И 6 и элементы ИЛИ 5

по шине 20 микрокомандой. По окончаниивсех предыдущих процессоров 2, поступает

операции включенное устройство выдает (через

проводное ИЛИ) сигнал на вход 21 счета для увеличения на 1 содержимого счетчика 14 ко манд. Загрузка оперативного запоминающего устройства 13 осуществляется перед началом работы через шину 11 данных. Окончание программы обработки заявки отмечается поступлением на вход дешифратора 15 соответствующего кода операции, вслед ствие чего дешифратор 15 выдает сигнал 19-5 управления, являющийся сигналом запроса, в блок 3 опроса и в элемент ИЛИ 5 Прн последовательном режиме обработки данных по окончании программы частичной обработки заявки дешифратор 15 выдает сигнал 19-4 управления, являющийся сигналом разрешения обращения к последующему процессору 2, в элемент И 8. Блок 3 опроса содержит два элемента И 22 и 23, вход 24 сигнала разрешения и выход 25 разрешения. На вход 24 из предыдушего процессора 2 поступает сигнал раэрещения, источником которого является память 1 заявок. Если операционный блок 4 не выдает в блок 3 опроса сигнала 19-5 запроса, то сигнал разрешения с входа 24 через элемент И 22 проходит на выход 25 и далее в последующий процессор 2. Если операционный блок 4 выдает в блок 3 опроса сигнал 19-5 запроса, то дальнейшее прохождение сигнала разрешения прекращается, а блок опроса 3 выдает с выхода схемы 23 в операционный блок 4 сигнал начала работы. Этот сигнал (объединенный проводным ИЛИ с сигналом 19-3) включает устройство 17 обмена которое инициирует связь с памятью 1 заявок и считывает из нее по шине 11 данных заявку для ее последующей обработки. Шина запросов, подключенная к входу памяти 1 заявок, реализована введением в каж дый процессор 2 элемента ИЛИ 5. В каждом свободном от отработки данцых процессоре 2 операционный блок 4 выдает с выхода запроса сигнал запроса, поступаюащй на второй вход элемента ИЛИ 5 и на вход запроса блока 3 опроса. В зависимости от режима обработки, заданного сигналом на управляющем входе 12, запрос может поступить либо в память I заявок (параллельной режим), либо в предьщущий процессор 2 (последовательный режим). При параллельном режиме обработки дан- , ных, заданном наличием сигнала на управляю щем входе 12, запрос любого процессора 2, пройдя через элемент ИЛИ 5 данного пров память 1 заявок. После этого память 1 заявок, прн наличии в ней хотя бы одной заявки, выдает сигнал разрешения, который последовательно проходит через блоки 3 опроса и блоки 10 переключения режимов цепочки процессоров 2. При поступлении сигнала резрешения в первый в этой цепочке процессор 2, выдавашй запрос, дальнейшее прохождение сигнала разрешения прекращается, а в этом процессоре 2 блок 3 опроса выдает на управляющий вход операционного . блока 4 сигнал начала работы. Данный процессор 2 инициирует связь с памятью 1 .заявок, считывает из нее по щине 11 данных первую в очереди заявку и начинает ее обработку, одновременно сбрасьшая свой сигнал запроса и тем самым пропуская сигнал разрешения через блок 3 опроса элемент И 7 и элемент ИЛИ 9 к последующему процессору 2. Если зтот последующий процессор 2 тоже выдал запрос, то вторая в очереди заявка из памяти 1 заявок будет аналопгчным образом считана в этот последующий процессор 2, в противном случае он пропустит сигнал разрешения далее. При последовательном режиме обработки данных, заданном отсутствием сигнала м управляющем входе 12, запрос первого процессора 2, пройду через элемент ИЛИ 5, поступает в память 1 заявок. | игнал разрешения из памяти 1 заявок поступает в блок 3 опроса первого процессора 2, который выдает в операционный блок 4 сигнал начала работы. Первый процессор 2 считьгаает из памяти 1 заявок первую в очереди заявку и начин;ает ее обработку, одновременно сбрасывая свой запрос. После частичной обработки заявки операционный блок 4 первого процессора 2 выдает с выхода обращения сигнал разрешения обращения к последующему (второму) процессору 2, поступающий на второй вход элемента И 8. При поступлении на первый вход элемента И 8 запроса из второго прощессора 2 сигнал разрешения с выхода элемента ИЛИ 9 первого процессора 2 поступает на вход разрешения блока 3 опроса второго процессора 2, который выдает в операционный блок 4 сигнал начала работы. Второй процессор 2 инициирует связь с первым процессором 2, считывает из него результаты частичной обработки первой заявки и продолжает ее обработку, одновременно сбрасывая свой запрос. Далее заявка аналогичным образом последовательно передается для обработки от одного процессора 2 к другому. Первый процессор 2 после передачи заявки во второй процессор 2 освобождается и вновь выдает запрос в память 1 заявок для получения второй в очереди заявки. Технико- экономическая эффективность, получаемая в результате применения системы, заключается в расширении функциональных возможностей системы за счет возможности ее работы в режиме последовательной обработки данных что позволяет системе адаптиро ваться к различным способам обработки данных и, следовательно, более эффективно обра батывать разнообразные типы заявок, в том числе заявки, зависимые между собой. ормула изобретения Адаптивная система обработки данных, содержащая память заявок и однотипные процессоры, каждый из которых содержит операцио ный блок и блок-опроса, входы-выходы операционных блоков всех процессоров объединены шиной данных с входом-выходом памяти заявок, выход памяти заявок подкгаочен к входу разрешения, блока опроса первого процессора, выход запроса операодонного блока подкорочен к входу запроса блока опроса, управляющий выход блока опроса подключен к управляющему входу операционного блока, отличающаяся тем, что, с целью сокращения времени обслуживания взаимозависимых заявок, в ка5кдый процессор введены элемент ИЛИ и блок переключения режимов, причем выход элемента ИЛИ нервого процессора подключен к входу памяти заявок, выход элемента ИЛИ каждого процессора, кроме первого, подключен к входу запроса блока переключения режимов каждого предьщущего процессора, первый вход элемента ИЛИ подключен к выходу запроса блока переключения режимов, второй вход элемента ИЛИ подключен к выходу занроса операционного блока, входы переключения блоков переключения режимов всех процессоров соединены между собой, выход обращения операционного блока соединен с дополнительным входом блока переключения режимов, выход разрещения которого подключен к входу разреше11ия блока опроса последующего процессора, выход разрешения блока опроса подключен к входу разрещення блока переключения режимов, причем блок переключения режимов содержит элемент ИЛИ и три элемента И, выход первого элемента И подключен к выходу запроса блока, первый вход первого элемента И соещшен с входом переключения блока и с первым входом второго элемента И, а второй вход - с входом запроса блока и первым входом третьего элемента И, второй вход которого соединен с входом обращения блока, выход третьего элемента И соеданен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, второй вход которого соединен с входом разрешения бцока, выход элемента ИЛИ соеданен с выходом разреще1шя блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 640301, кл. G 06 F 15/16, 1978. 2.ТИИЭР, перев. с англ., Мир, 1976, N 6 (июнь) с. 32-33 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1455342A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451713A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451712A1 |

| Адаптивная система обработки данных | 1988 |

|

SU1509921A1 |

| Адаптивная система обработки данных | 1988 |

|

SU1552195A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

| Мультиплексный канал | 1979 |

|

SU922713A1 |

| Устройство для сопряжения | 1981 |

|

SU1001072A1 |

фмг,,1.

Авторы

Даты

1982-05-07—Публикация

1980-05-26—Подача