1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики в системах автоматики, вычислительных и в других цифровых устройствах.

Целью изобретения является сокращение аппаратных затрат при построе- НИИ многовходовых сигнатурных анализаторов.

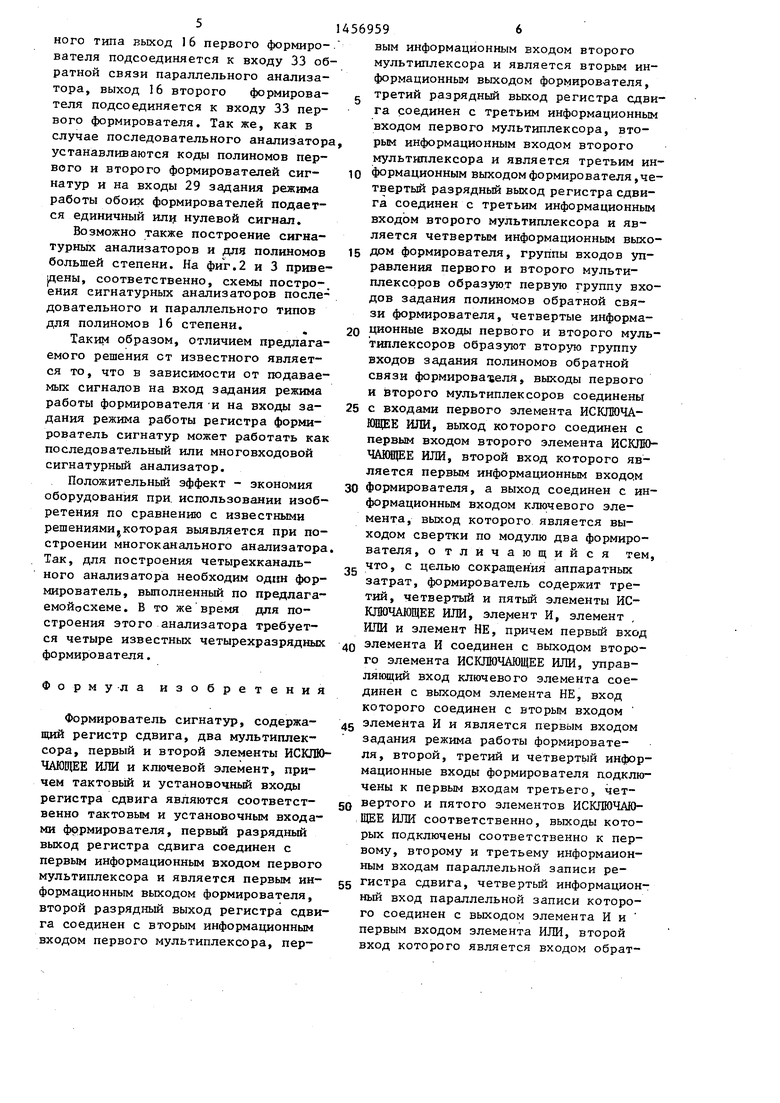

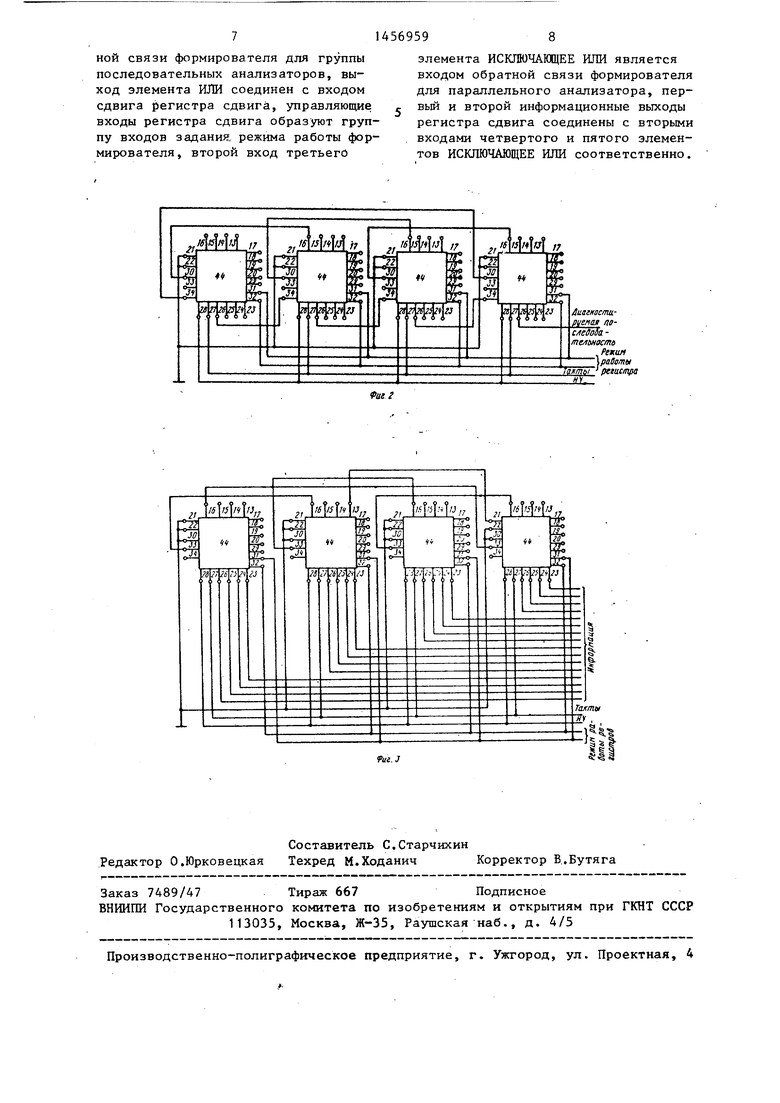

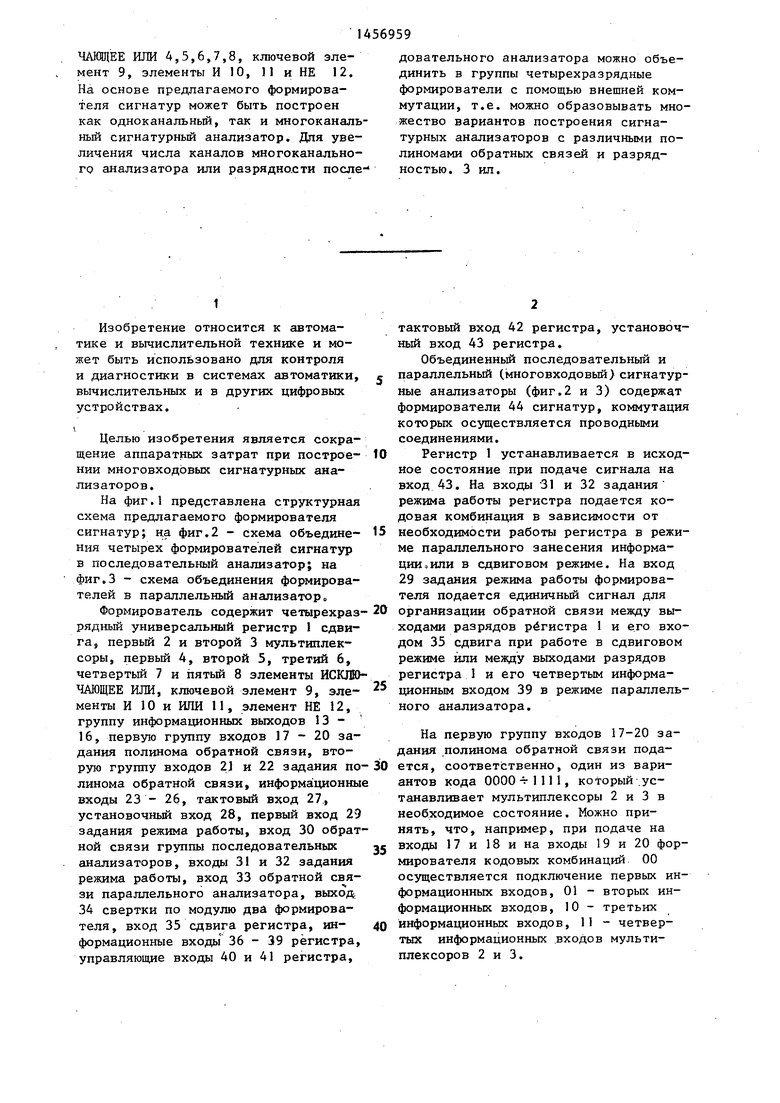

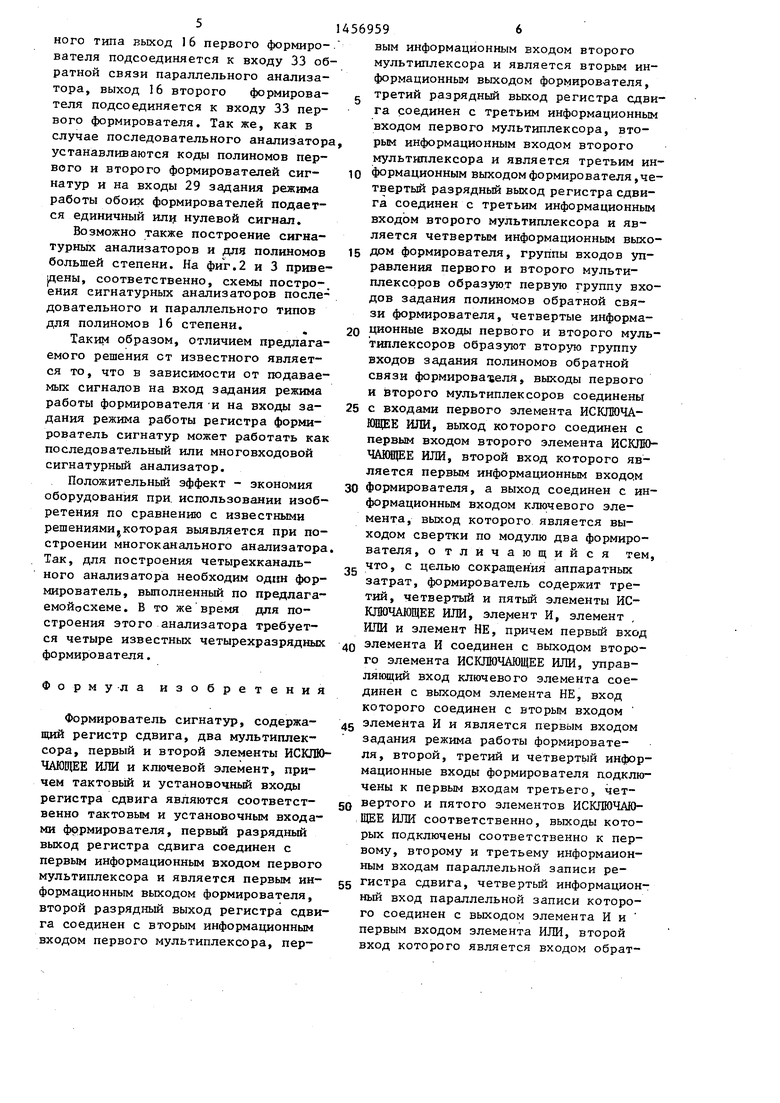

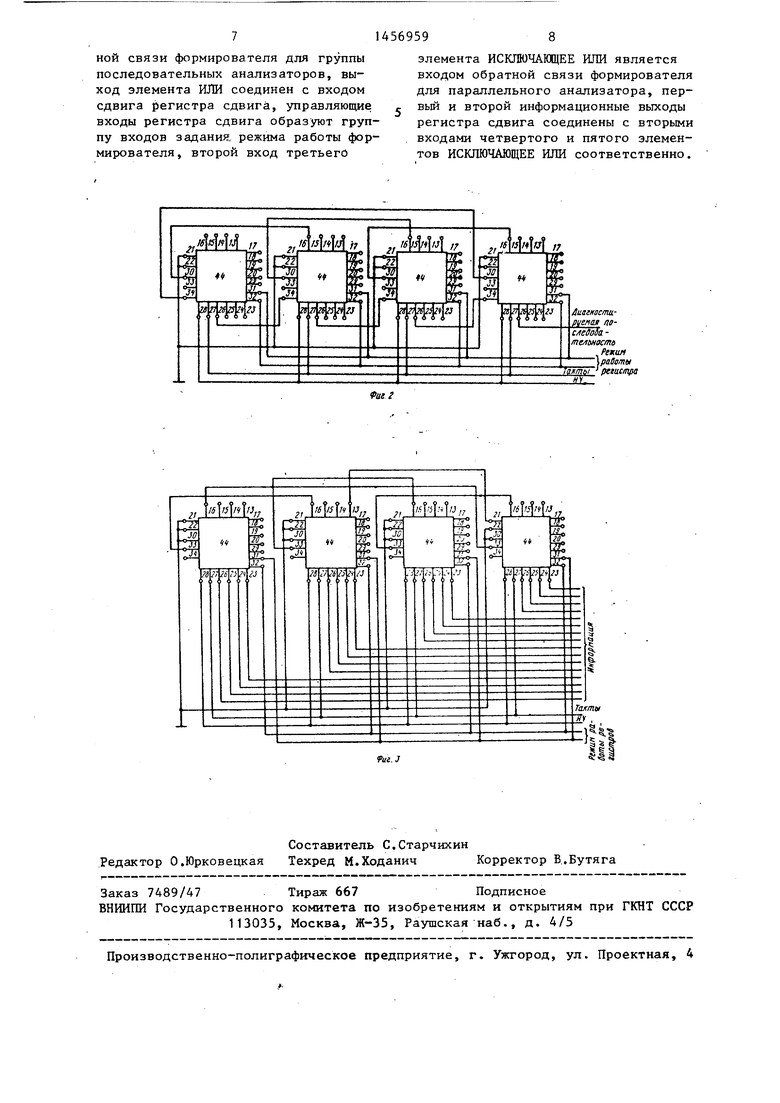

На фиг.1 представлена структурная схема предлагаемого формирователя сигнатур; нд фиг.2 - схема объедине- НИН четырех формирователей сигнатур в последовательный анализатор; на фиг.З - схема объединения формирователей в параллельный анализатор.

Формирователь содержит четарехраз- рядный универсальный регистр 1 сдвига, первый 2 и второй 3 мультиплексоры, первый 4, второй 5, третий 6, четвертый 7 и пятый 8 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, ключевой элемент 9, эле- менты И 10 и ШШ 11, элемент НЕ 12, группу информационных выходов 13 - 16, первую группу входов 17-20 задания полинома обратной связи, вторую группу входов 2) и 22 задания по- линома обратной связи, информационные входы 23 - 26, тактовый вход 27, установочньй вход 28, первый вход 29 задания режима работы, вход 30 обратной связи группы последовательных анализаторов, входы 31 и 32 задания режима работы, вход 33 обратной связи параллельного анализатора, выход, 34 свертки по модулю два формирователя, вход 35 сдвига регистра, ин- формационные входы 36 - 39 регистра, управляющие входы 40 и 41 регистра.

тактовый вход 42 регистра, установочный вход 43 регистра.

Объединенный последовательный и параллельный (многовходовый) сигнатурные анализаторы (фиг.2 и 3) содержат формирователи 44 сигнатур, коммутация которых осуществляется проводными соединениями.

Регистр 1 устанавливается в исходное состояние при подаче сигнала на вход 43. На входы 31 и 32 задания режима работы регистра подается кодовая комбинация в зависимости от необходимости работы регистра в режиме параллельного занесения информации, или в сдвиговом режиме. На вход 29 задания режима работы формирователя подается единичньш сигнал для организации обратной связи между выходами разрядов регистра 1 и его входом 35 сдвига при работе в сдвиговом режиме или между выходами разрядов регистра 1 и его четвертым информационным входом 39 в режиме параллельного анализатора.

На первую группу входов 17-20 задания полинома обратной связи подается, соответственно, один из вариантов кода 0000-V 1 11 1, который .устанавливает мультиплексоры 2 и 3 в необходимое состояние. Можно принять, что, например, при подаче на входы 17 и 18 и на входы 19 и 20 формирователя кодовых комбинаций 00 осуществляется подключение первых информационных входов, 01 - вторых информационных входов, 10 - третьих информационных входов, 11 - четвертых информационных входов мультиплексоров 2 и 3.

Если регистр 1 работает в сдвиговом режиме, то информация поступает только с четвертого информационного входа 26 формирователя через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и элемент ИЛИ 11 на вход 35 сдвига регистра 1 информационные входы 36-39 регистра 1 зарыты комбинацией сигналов на входах 31 и 32 задания режима работы регистра.

При работе регистра 1 в параллельном режиме вход 35 сдвига регистра 1 закрыт комбинацией сигналов на входах 3 и 32 задания режима работы регистра, а информационные входы 36- 39 регистра открыты той же комбинацией сигналов на входах 31 и 32. Информация поступает на информационные входы 36-39 регистра с информационных входов 23-26 формирователя через элементы ИСКПЮЧАЩЕЕ ИЛИ 5-8.

Для обеспечения работы формирователя сигнатур в режиме параллельного анализатора необходимо путем внешней коммутации соединить выход 16 формирователя с входом 33 обратной связи параллельного анализатора.

Для обеспечения работы формирователя сигнатур в режиме последовательного анализатора необходимо на вход 30 обратной связи группы последовательных анализаторов подать нулевой сигнал для того, чтобы не искажалась информация, поступающая с четвертого информационного входа 26 формирователя на вход 35 сдвига регистра 1.

Для реализации определенного полинома обратной связи на входы 17 - 20 формирователя необходимо подать один из вариантов кода ОООО-г} 111, После этого в случае работы в режиме параллельного анализатора на информационные входы 23-26 подается диагностируемая последовательность сигналов и осуществляется ее свертка по выбранному полиному. В случае работы в режиме последовательного анализатора диагностируемая последовательность сигналов подается только на информационный вход 26. Свертка диагностируемой последовательности с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 поступает через элемент ШШ-П на вход сдвига регистра 1. Информационные входы 23-25 формирователя в этом случае, не используются, поскольку

56959

они являются входами элементов ИС- КЛЮЧАЮИЩЕ ИЛИ 6-8, выходы которых соединены с информационными входами

36-38 регистра 1, которые, в свою очередь, заблокированы кодовой комбинацией сигналов, поступающей на управляющие входы 40 и 41 регистра 1 с входов 31 и 32 задания режима

10 работы регистра. При необходимости повысить достоверность диагностирования в процессе его проведения изменяется код на первой группе входов 17-20 формирователя, т.е. меняет15 ся образуняций полином.

0

5

0

5

Таким образом, осуществляется функционирование одного четырехразрядного формирователя сигнатур.

Для увеличения числа каналов многоканального анализатора или разрядности последовательного анализатора можно объединить в группы четырех- разрядньге формирователи с помощью внешней коммутации, т.е. можно образовывать множество вариантов построения сигнатурных анализаторов с различными полиномами обратных связей и разрядностью.

Например, для построения восьмиразрядного сигнатурного анализатора последовательного типа выход 16 первого формирователя сигнатур подсоединяется к входу 30 обратной связи группы последовательных анализаторов вторю го формирователя сигнатур, выход 34 перього формирователя подсоединяется к информационному входу 26 второго, выход 34 свертки по модулю два второго формирователя подсоединяется к входу 30 обратной связи группы последовательньк анализаторов первого формирователя. Устанавливаются коды полиномов первого и второго формирователей сигнатур путем подачи управляющих сигналов на первую группу входов 17-20 задания полинома обратной связи первого и второго формирователей. На входы 29 задания режима работы первого и второго формирователей подается единичный или нулевой сигнал в зависимости от необходимости организации обратных связей с выходов разрядов регистров на входы регистров при последовательном режиме работы первого и второго формирователей.

При построении восьмиразрядного сигнатурного анализатора параллель0

0

5

ного типа выход 16 первого формиро-. вателя подсоединяется к входу 33 обратной связи параллельного анализатора, выход 16 второго формирователя подсоединяется к входу 33 первого формирователя. Так же, как в случае последовательного анализатора, устанавливаются коды полиномов первого и второго формирователей сигнатур и на входы 29 задания режима работы обоих формирователей подается единичный илч нулевой сигнал.

Возможно также построение сигнатурных анализаторов и длд полиномов большей степени. На фиг.2 и 3 приведены, соответственно, схемы построения сигнатурных анализаторов последовательного и параллельного типов для полиномов 16 степени.

Таким образом, отличием предлагаемого решения от известного является то, что в зависимости от подаваемых сигналов на вход задания режима работы формирователя-и на входы задания режима работы регистра формирователь сигнатур может работать как последовательный или многовходовой сигнатурный анализатор.

Положительный зффект - экономия оборудования при использовании изобретения по сравнению с известными решениями которая выявляется при построении многоканального анализатора. Так, для построения четырехканаль- ного анализатора необходим один формирователь, выполненный по предлага- емойосхеме. В то же время для построения этого анализатора требуется четыре известных четырехразрядных формирователя.

1456959

Формула

изобретения

Формирователь сигнатур, содержащий регистр сдвига, два мультиплексора, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и ключевой элемент, причем тактовьй и установочный входы регистра сдвига являются соответственно тактовым и установочным входами формирователя, первый разрядный выход регистра сдвига соединен с первым информационным входом первого мультиплексора и является первым информационным выходом формирователя, второй разрядный выход регистра сдвига соединен с вторым информационным входом первого мультиплексора, первым информационнь м входом второго мультиплексора и является вторым ин- формационньм выходом формирователя, третий разрядный выход регистра сдвига соединен с третьим информационным входом первого мультиплексора, вторым информационным входом второго мультиплексора и является третьим ин- 10 Формационным выходом формиро вателя, че- твертьй разрядньй выход регистра сдвига соединен с третьим информационным входом второго мультиплексора и является четвертым информационным выхо- 15 дом формирователя, группы входов управления первого и второго мультиплексоров образуют первую группу входов задания полиномов обратной связи формирователя, четвертые информа- 20 ционные входы первого и второго мультиплексоров образуют вторую группу входов задания полиномов обратной связи формирователя, выходы первого и второго мультиплексоров соединены 25 с входами первого элемента ИСКЛЮЧА- ННЦЕЕ ИЛИ, выход которого соединен с первым входом второго элемента ИСКЛЮ- ЧАНШЩЕ ИЛИ, второй вход которого является первым информационным входом 30 формирователя, а выход соединен с информационным входом ключевого элемента, выход которого является выходом свертки по модулю два формирователя, отличающийся тем, 35 целью сокращения аппаратных затрат, формирователь содержит третий, четвертый и пятый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, И, элемент ИЛИ и элемент НЕ, причем первый вход 40 элемента И соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющий вход ключевого элемента соединен с выходом элемента НЕ, вход которого соединен с вторым входом 45 элемента И и является первым входом задания режима работы формирователя, второй, третий и четвертый информационные входы формирователя подключены к первым входам третьего, чет- 50 вертого и пятого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, выходы которых подключены соответственно к первому, второму и третьему информаион- ным входам параллельной записи ре- 55 гистра сдвига, четвертьш информационный вход параллельной записи которого соединен с выходом элемента И и первым входом элемента ИЛИ, второй вход которого является входом обратной связи формирователя для группы последовательных анализаторов, выход элемента ИЛИ соединен с входом сдвига регистра сдвига, управляющие входы регистра сдвига образуют группу входов задания, режима работы формирователя, второй вход третьего

элемента ИСКЛЮЧАЮЩЕЕ ШШ является входом обратной связи формирователя для параллельного анализатора, пер- вьй и второй информационные выходы регистра сдвига соединены с вторыми входами четвертого и пятого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1984 |

|

SU1238075A1 |

| Сигнатурный анализатор с перестраиваемой стуктурой | 1986 |

|

SU1336009A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для диагностики неисправностей цифровых узлов | 1987 |

|

SU1481773A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1451772A1 |

| Сигнатурный анализатор | 1987 |

|

SU1416997A1 |

| Сигнатурный анализатор | 1987 |

|

SU1427370A1 |

Изобретение относится к автоматике и вычислительной технике и позволяет сократить аппаратные затраты при построении многоканальных сигнатурных анализат оров. Формирователь сигнатур содержит з ниверсальный четы- рехзарядный регтлстр сдвига 1, два мультиплексора 2, 3, элементы ИСКЛЮ

| Вопросы радиоэлектроники | |||

| Сер | |||

| ТПО, 1982, 1, с.114-117 | |||

| Сигнатурный анализатор | 1984 |

|

SU1238075A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-07—Публикация

1987-06-01—Подача